Introduction to the NI MIMO Prototyping System Hardware

Overview

As more devices are connected wirelessly, the need for wireless technologies that can handle increased data and capacity demands has grown exponentially. The coming onslaught of Internet of Things (IoT) devices threatens to overwhelm existing wireless networks while the proliferation of video streaming and virtual reality technology requires faster data rates than are currently available. Multiple input, multiple output (MIMO) is one technology that has the potential to solve these problems by enabling the next generation of wireless. By using more than one antenna, multiple data signals can be sent in the same time and frequency domain to offer huge gains in capacity, throughput, reliability, or a combination of the three. As leading researchers and wireless companies rush to explore new communications technologies, MIMO will be a crucial topic.

Multi-User MIMO (MU-MIMO) in particular shows immense promise for fifth-generation (5G) wireless networks. MU-MIMO enables a base station with a large number of antennas to use advanced signal processing techniques to target multiple users simultaneously while reusing the same time and frequency space. MU-MIMO and Massive MIMO, a version of MU-MIMO, open the possibility of increasing the capacity of a wireless network by more than tenfold while increasing reliability and network density.

Some of the theory behind MU-MIMO and Massive MIMO has been laid out, but researchers need to innovate faster by building real-world prototypes. The NI MIMO Prototyping System is a testbed that enables researchers to prototype these 5G MIMO systems and achieve rapid results.

Contents

- MIMO Prototyping System Hardware

- System Architecture

- System Configuration Options

- Software Interface

- Summary

MIMO Prototyping System Hardware

The MIMO Prototyping System includes USRP RIO radio heads, FlexRIO FPGA co-processors, clock distribution modules, PCIe routing hardware, and a PXIe chassis and controller. The system can be configured in a variety of sizes to meet the requirements of a wide range of MIMO applications including single user MIMO (SU-MIMO), multiple user MIMO (MU-MIMO), and Massive MIMO. The various system components and configurations will be discussed in detail in this paper. Application software is discussed in MIMO Application Framework white paper.

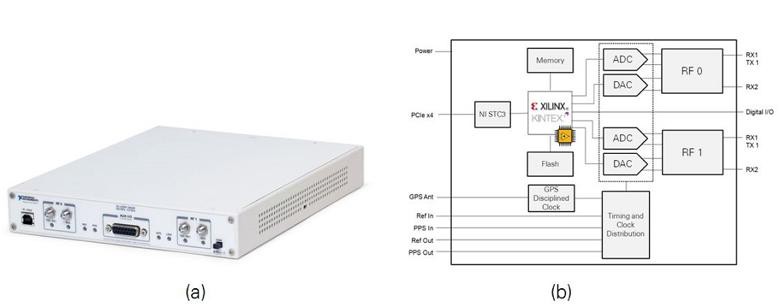

USRP Software Defined Radio

The USRP RIO software defined radio (SDR) features an integrated 2x2 MIMO transceiver and a high-performance Xilinx Kintex-7 FPGA, all contained in a half-width 1U rack-mountable enclosure, to accelerate baseband processing. It connects to a host controller through a cabled PCI Express x4 connection to the system controller to allow up to 800 MB/s of streaming data transfer to the desktop or PXI Express host computer (or laptop at 200 MB/s over ExpressCard). Figure 1 shows a block diagram overview of the USRP RIO hardware.

Figure 1. USRP RIO Hardware (a) and System Block Diagram (b)

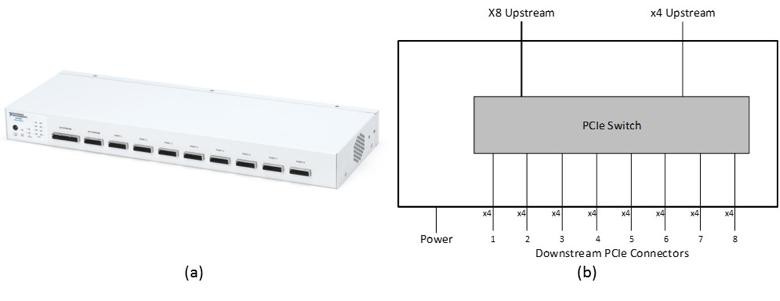

Cabled PCI Express Switch Box

The CPS-8910 cabled PCI Express switch box (CPS) combines multiple USRP RIO PCI Express connections into a single stream, which simplifies the system while allowing it to efficiently aggregate many channels. The switch box can support up to eight separate downstream devices through cabled PCI Express x4 Gen 1 connections. In the MIMO configuration, these streams are combined into a single PCI Express x8 Gen 2 connection, which allows an aggregate data rate of up to 3.2 GB/s. In other configurations, a PCI Express x4 Gen 1 upstream connection can be used instead. Additionally, the CPS-8910 enables peer-to-peer streaming between USRP devices. Both copper and fiber-optic PCI Express cables are supported. Figure 2 shows a block diagram overview of the CPS-8910 hardware.

Figure 2. Switch Box (a) and System Diagram (b)

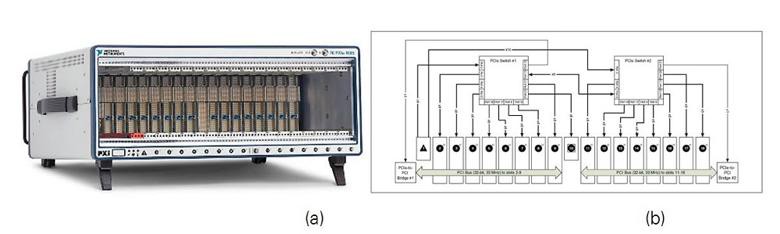

PXI Express Chassis Backplane

The system uses a PXIe-1085, which is an advanced 18-slot PXI chassis that features PCI Express Gen 3 technologies in every slot for high-throughput, low-latency applications. The chassis is capable of 8 GB/s of per slot bandwidth and 24 GB/s of system bandwidth. Figure 3 shows the dual-switch backplane architecture.

Figure 3. 18-Slot PXIe-1085 Chassis (a) and System Diagram (b)

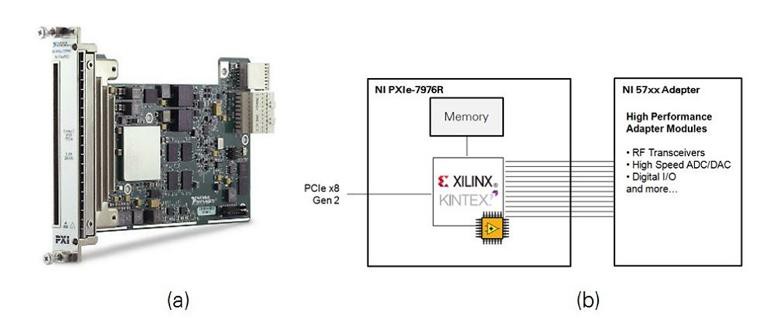

High Performance FPGA Co-Processor

The MIMO Prototyping System integrates flexible, high-performance FlexRIO FPGA processing modules that are programmable with the LabVIEW FPGA Module in the PXI form factor. You can use the PXIe-7976R FPGA Module for FlexRIO as a stand-alone device that provides a large and customizable Xilinx Kintex-7 410T with PCI Express x8 Gen 2 connectivity to the PXI Express backplane.

Figure 4. PXIe-7976R FlexRIO Module (a) and System Diagram (b)

Precision Clock Generation

A PXIe-6674T Synchronization Module (Figure 5) is used to generate a 10 MHz reference clock with a highly accurate onboard oven-controlled crystal oscillator (OCXO). This signal is used to form the reference timebase for each USRP RIO radio head to ensure accurate synchronization. The PXIe-6674T also is used to process and re-output a sync trigger from one of the USRP RIO SDRs.

Figure 5. A PXIe-6674T Timing and Synchronization Module

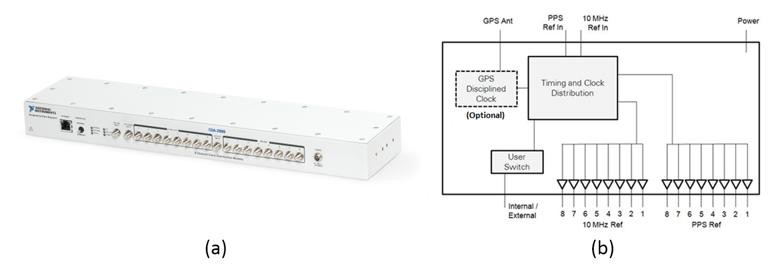

8-Channel Clock Synchronization

The CDA-2990 eight-channel clock distribution module provides both frequency and time synchronization for up to eight USRP devices by amplifying and splitting the 10 MHz reference and pulse per second signal eight ways through matched-length traces. The CDA-2990 adds an internal time and frequency reference using an integrated GPS-disciplined oscillator (GPSDO). Figure 6 shows a system overview of the CDA-2990 with a GPSDO.

Figure 6. CDA-2990 (a) and System Diagram (b)

System Architecture

The hardware elements above combine to form a testbed that can scale from a few antennas to more than 128 synchronized antennas. For simplicity, this paper uses a 128-antenna configuration in each diagram.

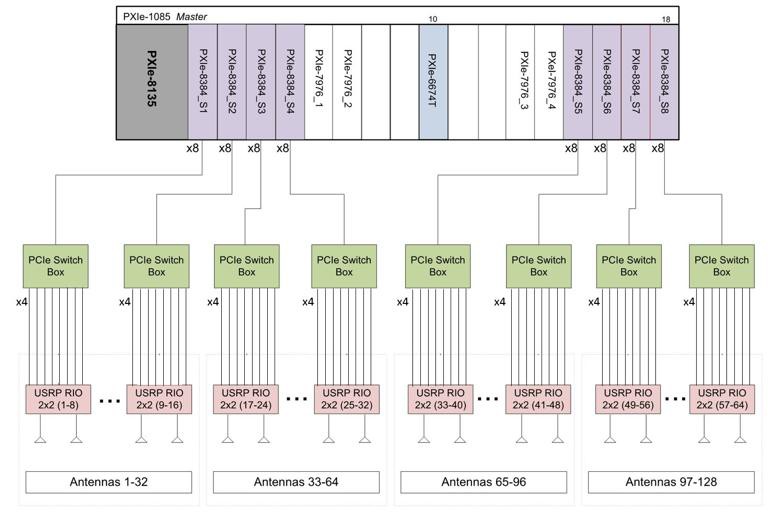

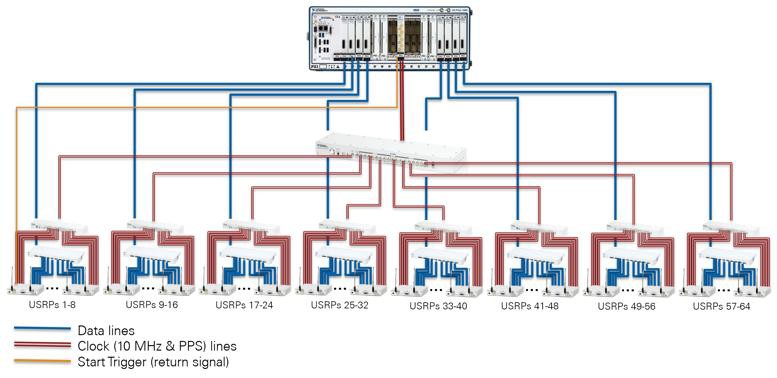

Data Processing

High-channel-count MIMO systems require exceptionally robust data processing. Up to 128 channels of I and Q samples must be processed in real time for both transmit and receive. To handle this amount of data, the MIMO Prototyping System uses high-throughput PCI Express buses. Data is sent from the USRP RIO SDRs through PCI Express switch boxes to a single PXI Express chassis. The chassis aggregates data for centralized processing with both FPGA coprocessors and a quad-core Intel i7 PXI controller. As shown in Figure 7, a PXIe-1085 Chassis is the main data aggregation node and real-time signal processing engine. In slot 1 of the chassis, the PXIe-8135 RT Controller acts as a central system computer. The PXIe-8135 RT features a 2.3 GHz quad-core Intel Core i7-3610QE processor (3.3 GHz maximum in single-core Turbo Boost mode). The chassis additionally houses eight PXIe-8384 (S1 to S8) Remote Control Modules to connect the PCI Express switch boxes to the master system. Each switch box in turn aggregates eight USRP RIO connections. The connection between the PXI chassis and the switch boxes uses PCI Express x8 Gen 2 technology to provide up to 3.2 GB/s between the chassis and each switch box.

The system also features PXIe-7976R FlexRIO FPGA coprocessor modules to address the real-time signal processing requirements for the MIMO Prototyping System. Each PXIe-7976R features a powerful Kintex-7 410T FPGA. Each FlexRIO module can receive or transmit data across the backplane to each other and to all the USRP RIO SDRs with <5 µs of latency and up to 3.2 GB/s throughput per FPGA coprocessor. The number of FlexRIO FPGA coprocessors required scales from one to four based on the number of antennas used.

Figure 7. Data Channels in the MIMO Prototyping System

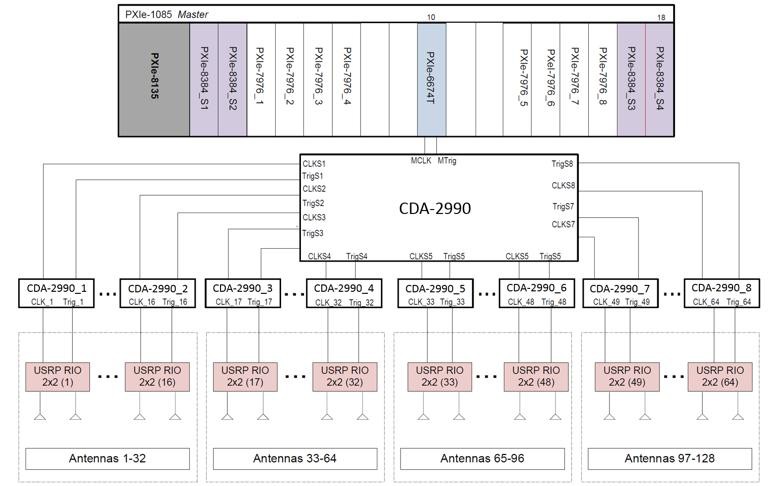

Timing and Synchronization

Proper timing and synchronization are critical in any MIMO system. The MIMO Prototyping System shares a common 10 MHz reference clock and a digital trigger to start acquisition or generation on each radio and ensure system-level synchronization (see Figure 8). The PXIe-6674T Synchronization Module in the chassis uses an OCXO to produce a very stable and accurate 10 MHz reference clock (80 ppb accuracy). It also supplies a digital trigger for device synchronization to the master CDA-2990 clock distribution accessory. The master CDA-2990 then supplies and buffers the 10 MHz reference (MCLK) and trigger (MTrig) to eight additional CDA-2990 modules that feed the USRP RIO SDRs, thereby ensuring that each antenna shares the 10 MHz reference clock and master trigger. As a result, the timing and synchronization architecture offers very precise control of each radio/antenna element. This produces phase-coherent operation, where each channel maintains a constant phase offset from the other channels. You can then use software calibration techniques to sufficiently align the channels.

Figure 8. Clock distribution in the MIMO Prototyping System

Combining the data path hardware with the timing modules produces a powerful testbed that can handle massive flows of data in real time and meet the synchronization needs of MIMO researchers. This system is also inheriently scalable. You can easily add more antennas with only minor changes in the hardware architecture.

Single Antenna UE

In MU-MIMO, a base station with many antennas communicates with several single antenna User Equipment (UE). The MIMO Application Framework supports up to 1 single antenna UEs. Each UE represents a handset or other wireless device. UEs can be represented by using an individual USRP RIO with an internal GPS-disciplined oscillator (GPSDO) connected to a laptop through cabled PCI Express to ExpressCard connection. The GPSDO is important because it provides improved frequency accuracy plus additional synchronization and geo-location capability. A typical MU-MIMO testbed implementation will include multiple USRP RIOs acting independently as UEs. Since each USRP RIO has two RF channels, each USRP and laptop combination can represent two UEs.

Multiple Antenna UE

The MIMO Application Framework supports both single antenna and multiple antenna UEs. UEs can be configured with 1, 2, 4, 6, 8, 10, or 12 antennas. Note that while up to 12 antennas are supported at the UE, the MIMO Application Framework only supports up to 12 spatial streams out of the box. Support for additional spatial streams can be added with modifications to the code base.

For UEs with more than 1 antenna, the required hardware is identical to that of the base station. That is, in addition to the USRP RIO, a PXI chassis, controller, FlexRIO FPGA modules, PXIe-6674T timing and synchronization module, CDA-2990 reference & PPS distribution module, and CPS-8910 PCIe switch box module are also required.

System Configuration Options

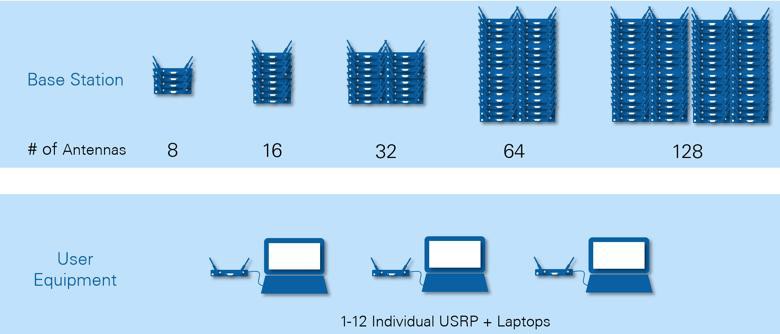

The MIMO Prototyping System is designed to be inherently scalable and flexible to user needs. The system can handle as many as 128 antennas (Figure 9) and as few as two.

Multi-User MIMO

Figure 9. 128 Channel MU-MIMO setup

As shown in figure 10, The most common base station configurations are for 16 antennas, 32 antennas, 64 antennas, and 128 antennas. If the MIMO Application Framework is used, a maximum of 12 spatial streams is supported. However, the number of UEs should never exceed the number of base station antennas minus one. Optimal performance is derived when the ratio of base station antennas to UEs is greater than 8:1.

Figure 10. Common MU-MIMO configurations

The exact MU-MIMO setup may also be different depending on your research needs. For instance, you can use antennas supplied through NI or interface your own antenna designs with the radio heads. You can optionally purchase larger MIMO configurations fully assembled and tested in a rack.

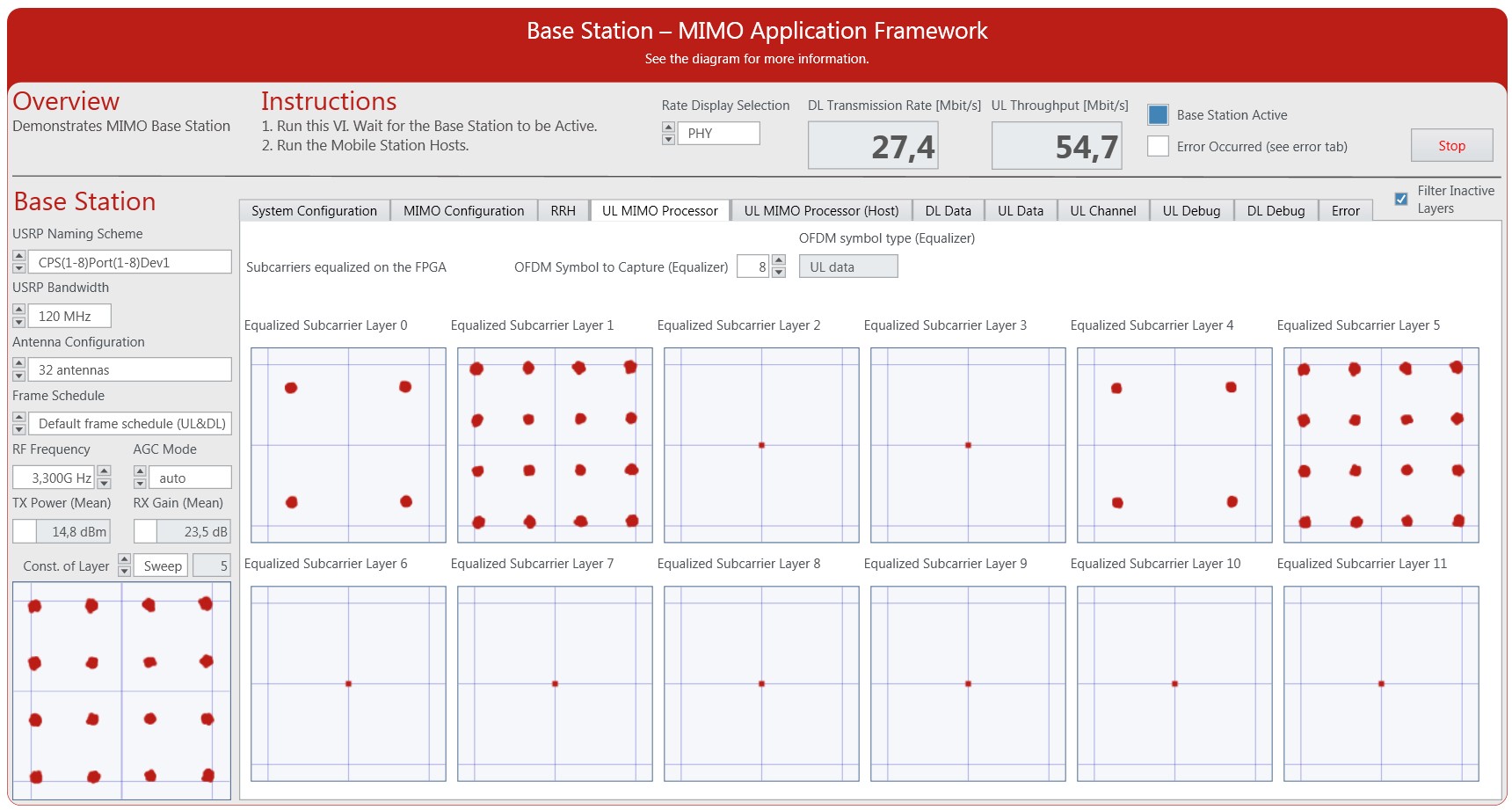

Software Interface

While the MIMO Prototyping System can be programed from the ground up with LabVIEW and LabVIEW Communications, it is designed specifically to be used with the MIMO Application Framework. This software framework, shown in Figure 11, provides an open and reconfigurable physical layer reference design that can be configured to meet research needs or used as a foundation for a brand-new MIMO application.

Figure 11. Front panel of the MIMO Application Framework

The MIMO Application Framework is implemented in LabVIEW Communications, and supports ready-to-run FPGA IP for MMSE, MRC, and ZF beamforming. The Application Framework also offers over-the-air synchronization, channel reciprocity calibration, a reconfigurable frame structure, MIMO detection, precoding, and real-time communication. Read the MIMO Application Framework white paper for more information.

Summary

The MIMO Application Framework is implemented in LabVIEW Communications, and supports ready-to-run FPGA IP for MMSE, MRC, and ZF beamforming. The Application Framework also offers over-the-air synchronization, channel reciprocity calibration, a reconfigurable frame structure, MIMO detection, precoding, and real-time communication. Read the MIMO Application Framework white paper for more information.