Fonction En virgule fixe

- Mise à jour2026-02-04

- Temps de lecture : 3 minute(s)

Convertit tout nombre non complexe en représentation en virgule fixe.

Si vous ne câblez pas de valeur à l'entrée type virgule fixe ou que vous ne configurez pas les paramètres de sortie de cette fonction, le type de données de la sortie virgule fixe s'adapte aux données que vous câblez à l'entrée nombre. Par exemple, si vous câblez un entier non signé 8 bit à l'entrée nombre, LabVIEW renvoie un nombre à virgule fixe non signé 8 bits avec 8 bits pour la partie entière. Cette fonction sature le nombre par défaut si un dépassement a lieu.

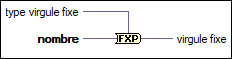

Entrées/Sorties

type virgule fixe

—

type virgule fixe

—

type virgule fixe correspond au type de données à virgule fixe dans lequel vous voulez convertir les données de type entier. Vous pouvez configurer le type de données à virgule fixe sur la page Type de données de la boîte de dialogue Propriétés. LabVIEW ignore les données de la constante ou de la commande câblée à type virgule fixe. Vous pouvez aussi laisser cette entrée non câblée et configurer le type de données en sortie sur la page Configuration de la sortie de la boîte de dialogue Propriétés.  nombre

—

nombre

—

nombre peut être n'importe quel nombre non complexe.  virgule fixe

—

virgule fixe

—

virgule fixe correspond aux données en entrée mises à l'échelle dans le type de données à virgule fixe demandé. |

Pour supplanter le comportement par défaut de cette fonction, cliquez avec le bouton droit sur la fonction et sélectionnez Propriétés dans le menu local pour afficher la page Configuration de la sortie de la boîte de dialogue Propriétés. Vous pouvez utiliser cette boîte de dialogue pour configurer les paramètres de sortie de cette fonction.

Détails du LabVIEW FPGA Module

Les détails suivants s'appliquent lorsque vous utilisez cet objet dans un FPGA VI.

| Boucle cadencée à un cycle | Supporté pour les entrées virgule fixe et entier uniquement. |

| Utilisation | Cette fonction ne supporte pas les entrées tableau. Cependant, vous pouvez transmettre des données tableau à cette fonction élément par élément si vous répondez aux critères suivants :

|

| Cadencement | Cette fonction ne requiert aucun cycle d'horloge pour les entrées virgule fixe et entier si vous sélectionnez le mode de dépassement Encapsulation et le mode Tronquer l'arrondi. D'autres modes de dépassement et d'arrondi peuvent avoir un impact sur le cadencement. Cette fonction requiert plusieurs cycles pour s'exécuter pour les entrées flottantes simple précision. |

| Ressources | Cette fonction ne consomme pas de ressources FPGA pour les entrées virgule fixe et entier si vous sélectionnez les modes de dépassement Encapsulation et Tronquer. D ' autres modes de dépassement pourraient avoir un impact sur les ressources. Cette fonction consomme beaucoup de ressources FPGA si le type d'entrée est à virgule flottante simple précision pour mettre à l'échelle le significand au type de sortie approprié. |

| Remarques | Vous pouvez aussi utiliser la fonction Haut débit en virgule fixe pour effectuer des analyses mathématiques en virgule fixe sur une cible FPGA. |