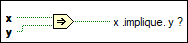

Fonction Implique

- Mise à jour2026-02-04

- Temps de lecture : 3 minute(s)

Obtient l'opposé de x, puis calcule le OU logique de y et de l'opposé de x. Les deux entrées doivent être des valeurs booléennes, des valeurs numériques ou des clusters d'erreur. Si x est VRAI et y est FAUX, la fonction renvoie FAUX. Sinon, elle renvoie VRAI.

Le connecteur affiche les types de données par défaut de cette fonction polymorphe.

Entrées/Sorties

x

—

x

—

x doit être une valeur booléenne ou un nombre. x peut être un scalaire, un tableau ou un cluster de nombres ou de valeurs booléennes, un tableau de clusters de nombres ou de valeurs booléennes, et ainsi de suite. Si x est un cluster d'erreur, seul le paramètre état du cluster d'erreur est transmis au terminal d'entrée.  y

—

y

—

y doit être une valeur booléenne ou un nombre. y peut être un scalaire, un tableau ou un cluster de nombres ou de valeurs booléennes, des tableaux de clusters de nombres ou de valeurs booléennes, et ainsi de suite. Si y est un cluster d'erreur, seul le paramètre état du cluster d'erreur est transmis au terminal d'entrée.  x .implique. y ?

—

x .implique. y ?

—

x .implique. y ? correspond au OU logique de y et de la négation logique de x. |

Table de vérité implicite

| x | y | x .implique. y ? |

|---|---|---|

| V | V | V |

| V | F | F |

| F | V | V |

| F | F | V |

Détails du LabVIEW FPGA Module

Les détails suivants s'appliquent lorsque vous utilisez cet objet dans un FPGA VI.

| Boucle cadencée à un cycle | Supportée. |

| Utilisation | Pour optimiser l'utilisation du temps et des ressources, utilisez des fonctions booléennes dans une boucle cadencée à un cycle. |

| Cadencement | À l'intérieur d'une boucle cadencée à un cycle -- Lorsque vous utilisez des fonctions booléennes dans une boucle cadencée à un cycle, chaque opération booléenne ajoute légèrement au délai de logique combinatoire de la boucle cadencée à un cycle. En dehors d'une boucle cadencée à un cycle -- Lorsque vous utilisez des fonctions booléennes en dehors d'une boucle cadencée à un cycle, chaque opération booléenne requiert un cycle d'horloge. |

| Ressources | Les fonctions booléennes ne consomment des ressources FPGA importantes que si vous câblez un grand tableau à l'entrée. Envisagez de limiter les tableaux pour conserver les ressources FPGA. |

Exemples

Reportez-vous aux fichiers d'exemple inclus avec LabVIEW.

- labview\examples\Booleans\Boolean Functions.vi