회전 함수

- 업데이트 날짜:2026-02-04

- 2분 (읽기 시간)

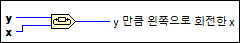

y로 지정된 비트 수만큼 x를 회전합니다.

커넥터 팬은 이 다형성 함수의 기본 데이터 타입을 디스플레이합니다.

입력/출력

y

—

y

—

y는 x에서 이 함수가 회전하는 비트 수를 지정합니다. If y is greater than 0, the function shifts the first y bits at the left end of x to the right end. If y is less than 0, the function shifts the first y bits at the right end of x to the left end. x

—

x

—

x가 8, 16, 32, 또는 64 비트 정수인 경우, y의 모든 값에 대해서 y ± 8, y ± 16, y ± 32, 또는 y ± 64는 각각 y와 같은 출력값을 만듭니다. For example, if x is an 8-bit integer, y = 1 and y = 9 yield the same result. y 만큼 왼쪽으로 회전한 x

—

y 만큼 왼쪽으로 회전한 x

—

y 만큼 왼쪽으로 회전한 x는 회전의 결과입니다. The data type of y 만큼 왼쪽으로 회전한 x is determined by the data type of the x input. |

다음 테이블은 x와 y가 y 만큼 왼쪽으로 회전한 x에 미치는 영향을 보여줍니다.

| y | x | y 만큼 왼쪽으로 회전한 x | 주석 |

|---|---|---|---|

| 1 | 3 (00000011) | 6 (00000110) | 이 함수는 왼쪽의 첫번째 비트 한 개, 0을 오른쪽 끝으로 이동합니다. |

| 2 | 3 (00000011) | 12 (00001100) | 이 함수는 왼쪽의 첫번째 비트 두 개, 00을 오른쪽 끝으로 이동합니다. |

| –3 | 3 (00000011) | 96 (01100000) | 이 함수는 오른쪽의 첫번째 비트 세 개, 011을 왼쪽 끝으로 이동합니다. |

LabVIEW FPGA Module 세부사항

다음 세부사항은 FPGA VI에서 이 객체를 사용할 때 적용됩니다.

노트 다음 세부사항은 각 LabVIEW FPGA Module 버전에 따라 변경될 수 있습니다.

| Single-Cycle Timed 루프 | 지원함. |

| Usage | 해당 없음 |

| 타이밍 | 단일 사이클 Timed 루프 내부 --단일 사이클 Timed 루프내에서 이 함수를 사용하는 경우, 조합 로직 지연은x의 비트 개수에 비례합니다. 단일 사이클 Timed 루프밖에서 --이 함수를 단일 사이클 Timed 루프 밖에서 사용하는 경우, 하나의 클럭 사이클과 하나의 레지스터를 사용합니다. |

| 리소스 | 이 함수는x의 비트 개수에 비례하는 FPGA 리소스를 필요로 합니다. |