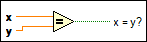

等しい?関数

- 更新日2026-02-04

- 5分で読める

xがyと等しい場合、TRUEを返します。それ以外の場合は、この関数はFALSEを返します。この関数の比較モードを変更できます。

2つの行列を比較する場合、デフォルトの比較モードは基礎群の比較で、この関数はスカラを返します。同じデータタイプのスカラと配列またはクラスタを比較して、ブール値の配列またはクラスタを生成できます。コネクタペーンには、この多態性関数のデフォルトのデータタイプが表示されます。

入力/出力

x

—

x

—

xはyと比較する値  y

—

y

—

yはxと同じタイプでなければなりません。  x = y?

—

x = y?

—

x = y?は、配列を比較する場合、集合比較モードを使用するとスカラになり、要素の比較モード (デフォルト) を使用するとブール配列になります。 |

VIサーバリファレンスを比較すると、2つのリファレンスが同じオブジェクトを参照している場合は、リファレンスの機能や値が同じかどうかに関係なく、常にTRUEが返されます。たとえば、1つのリファレンスがデジタル数値制御器への指定リファレンスで、もう一方は汎用リファレンスである場合も、同じオブジェクトを参照する場合は等しいとみなされます。リファレンスの実際の値を比較するには、「型変換」関数を使用して、リファレンスを32ビット符号付き整数に変換します。次に、「等しい?」関数を使用してそれらの整数を比較します。

上記の場合と同様に、同じLabVIEWオブジェクトに対するローカルリファレンスとリモートリファレンスをこの関数で比較すると、FALSEが返されます。ただし、2つのリファレンスが同じオブジェクトを参照していて、リファレンスの1つが認証されており、他方が認証されていない場合でも、この関数はTRUEを返します。

この関数に行列データを入力として配線すると、その行列データタイプと動作するサブVIを含むVIは関数を置換します。結果のVIは同じアイコンで表示されますが、行列固有のアルゴリズムを含みます。この入力から行列の接続を解除しても、ノードはVIのままの状態で残ります。他のデータタイプを入力として配線して、元の関数を復元します。データタイプを関数に配線し、そのデータタイプによって基本的な数学演算に失敗する場合は、関数は空の行列またはNaNを返します。

LabVIEW FPGAモジュールの詳細

以下の詳細は、このオブジェクトをFPGA VIで使用する場合に適用されます。

| シングルサイクルタイミングループ | サポートあり |

| Usage | この関数を単精度浮動小数点データタイプと使用する場合、リソース使用、レイテンシ、およびシングルサイクルタイミングループのサポートへの影響については、 単精度浮動小数点データタイプを使用 するおよび FPGA設計で使用するデータタイプを決定する トピックを参照してください。 |

| タイミング | シングルサイクルタイミングループの内側―比較関数をシングルサイクルタイミングループ内で使用すると、組み合わせ論理の遅延は比較するデータタイプの幅に比例します。 シングルサイクルタイミングループの外側―比較関数をシングルサイクルタイミングループの外側で使用すると、各比較関数に1クロックサイクルが必要となります。 固定小数点データタイプを扱う比較関数では、オーバーフローモードと丸め込みモードによってタイミングが影響を受ける可能性があります。 |

| リソース | 比較関数が使用するFPGAリソースの量は、比較するデータタイプの幅に比例します。 |

サンプルプログラム

LabVIEWに含まれている以下のサンプルファイルを参照してください。

- labview\examples\Comparison\Comparison Functions.vi