Decimate 1D Array

- Updated2026-02-04

- 3 minute(s) read

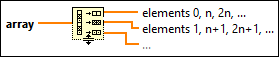

Divides the elements of array into the output arrays, placing elements into the outputs successively. This function drops any elements that cause the output arrays to have different lengths.

You also can add additional output terminals by resizing the function.

Inputs/Outputs

array

—

array

—

array can be a 1D array of any type.  decimated array

—

decimated array

—

elements 0, n, 2n, … is the first output array. The function stores array[0] at index 0 of the first output array, array[1] is stored at index 0 of the second output array, array[n-1] at index 0 of the last output array, array[n] at index 1 of the first output array, and so on, where n is the number of output terminals for this function. For example, assume the array has 16 elements and that you wire four output arrays. The first output array receives elements 0, 4, 8, and 12. The second output array receives elements 1, 5, 9, and 13. The third output array receives elements 2, 6, 10, and 14. The last output array receives elements 3, 7, 11, and 15. This is the expected behavior. If you remove one element from the input array there will only be 15 elements. The last decimated array will only have 3 elements (3, 7, and 11) since element 15 was deleted. Since the function will only return arrays of the same size, the other 3 decimated arrays will drop their last element so that all of the arrays now contain 3 elements.  decimated array

—

decimated array

—

elements 1, n+1, 2n+1, … is the second output array, and so on. |

FPGA Module Details

The following details apply when you use this object in an FPGA VI.

| Single-Cycle Timed Loop | Supported. |

| Usage | The LabVIEW FPGA Module supports only one-dimensional arrays that resolve to a single size at compile time. You can use constant or non-constant inputs. |

| Timing | This function requires no clock cycles to execute because it does not include an internal register. |

| Resources | This function consumes no FPGA resources because it is purely a wiring operation. |