NI does not actively maintain this document.

This content provides support for older products and technology, so you may notice outdated links or obsolete information about operating systems or other relevant products.

Each issue appears as a row in the table and includes the following fields:

| ID | Known Issue | |||||

|---|---|---|---|---|---|---|

| 386326 | The DAC outputs of the VST may be off by multiples of ~1 ns up to one full period of the Sample Clock Calling the Basecard Configure Clocks VI more than once per power cycle could cause the DAC outputs of the VST to be off by multiples of ~1 ns up to one full period of the Sample Clock within a single Sample Clock period, which could affect synchronization and MIMO applications. Workaround: Upgrade to version 2012.1 or later of the NI PXIe-5644R/5645R Instrument Design Libraries.

| |||||

| 364860 | A deadlock can occur when creating two peer-to-peer streams between two devices in opposite directions concurrently Workaround: To avoid the deadlock, serialize the calls to the niP2P Create Peer to Peer Stream VIs.

| |||||

| 365866 | Typographical error in NI PXIe-5644R Specifications Absolute Amplitude Accuracy table footnote The last footnote in Table 3. VSA Absolute Amplitude Accuracy (dB) should be "For reference levels <–30 dBm, absolute amplitude gain accuracy..." Workaround: N/A

| |||||

| 364736 | Waveform Sequencer does not generate any samples if the Set Priming Depth VI is set to a value of 4 samples or less The Retrieve Waveform Sample FPGA VI of the Waveform Sequencer library does not generate any samples if you set the generation priming depth to a value less than or equal to 4 in the Set Priming Depth VI of the Wavefrom Sequencer host library. Workaround: Configure the Set Priming Depth VI to a value of at least 5 samples; otherwise do not call the Set Priming Depth VI. If you do not call the Set Priming Depth VI, the application uses the default priming depth.

| |||||

| 363009 | NI PXIe-5644R device may occasionally appear outside the chassis in MAX when the device is installed for the first time NI PXIe-5644R device may occasionally appear outside the chassis in Measurement & Automation Explorer (MAX) when the hardware/software is installed for the first time. The device should still function properly. Workaround: Reboot the machine to get the device to appear in MAX properly.

| |||||

| 364518 | Error –52018. A hardware failure has occurred. The operation could not be completed as specified. This error may occur when an Instrument Design VI accesses elements of an FPGA VI that are inside a Single Cycle Timed Loop (SCTL) that does not have a running clock. In this case, the problem is not a hardware failure and can be fixed by enabling the clock of the SCTL. Workaround: Ensure that the SCTL clocks are running before calling the VI that returns the error.

| |||||

| 365456 | NI-RIO device may not be enumerated and may not appear in MAX Under some circumstances, an NI-RIO device may not be enumerated properly when attempting to access the device before the driver has finished loading. As a result, the device may not be accessible or visible through Measurement & Automation Explorer (MAX). Workaround: Reboot the machine or enable and disable the device in device manager.

| |||||

| 365552 | LabVIEW application builder returns Error 1502 when building an executable or DLL for the NI PXIe-5644R Attempting to build into a LabVIEW executable or DLL code that uses the NI PXIe-5644R vector signal transceiver (VST) might result in error 1502: LabVIEW: Cannot save a bad VI without its block diagram. For example, this error might occur if you build an executable from one of the VST Sample Projects. Detailed error description: An error occurred while saving the following file: C:\LabVIEW Data\MyVST\Host\VSA and VSG Acquisition and Generation (Host).vi. Visit the Request Support page at ni.com/ask to learn more about resolving this problem. Use the following information as a reference: Error 1502 occurred at AB_Source_VI.lvclass:Close_Reference.vi AB_Build.lvclass:Save.vi AB_Build.lvclass:Copy_Files.vi AB_Application.lvclass:Copy_Files.vi AB_EXE.lvclass:Copy_Files.vi AB_Build.lvclass:Build.vi AB_Application.lvclass:Build.vi AB_EXE.lvclass:Build.vi AB_Build.lvclass:Build_from_Wizard.vi AB_UI_Frmwk_Build.lvclass:Build.vi AB_UI_FRAMEWORK.vi AB_CreateNewWizard_Invoke_CORE.vi EBUIP_CreateNewWizard_Invoke.vi EBUIP_CreateNewWizard_Invoke.vi.ProxyCaller Possible reason(s): LabVIEW: Cannot save a bad VI without its block diagram. Workaround: From the build specification Additional Exclusions properties page, remove the checkmark from the Remove unused polymorphic VI instances checkbox prior to building the executable.

| |||||

| 365340 | Running a VST Sample Project FPGA VI in Development Computer with simulated IO context causes LabVIEW to hang Running a VST Sample Project FPGA VI in the Development Computer with simulated IO context causes LabVIEW to hang due to the way LabVIEW FPGA allocates and uses the DRAM memory primitive when executing in the development computer context. Workaround: There is no workaround to achieve full functionality, that is, to achieve the same waveform and record memory size available when running on hardware. However, you can use the following instructions to work around the LabVIEW memory hang:

| |||||

| 344816 | DIO Clock In does not appear in the drop-down menu of FPGA clock controls. The DIO Clock In for the NI PXIe-5644R is exposed through a socketed CLIP. However, in LabVIEW FPGA, CLIP input clocks don't appear in the drop-down menu of the FPGA Clock controls. Workaround: Use one of the following workarounds to configure a timed loop to use the DIO Clock In:

| |||||

| 356334 | External Calibration sessions that are not closed will lock up the device. If the External Calibration session is not closed, for example, if execution aborts before the call to the Close External Calibration VI, the device becomes unusable. Even new calls to Initialize External Calibration will fail. Workaround: To release the session, unload the External Calibration DLL or close the process that called the External Calibration DLL. Otherwise, restart the computer.

| |||||

| 365671 | The Open Session VI from the ECB instrument design library does not clear the ECB port memory when the clear memory parameter is set to True. Workaround: Use the Clear VI from the ECB instrument design library to clear the memory of the ECB port.

| |||||

| 372033 | The NI RF Vector Signal Transceivers Readme Version 1.0.0 does not state that local compilation requires a 64-bit operating system If you try to compile a Vector Signal Transceiver FPGA VI on a system with a 32-bit operating system, the following error occurs: "LabVIEW FPGA: The selected target requires 64-bit Xilinx tools, but the system uses a 32-bit OS." Workaround: Use a 64-bit OS to compile a VST FPGA VI on the local machine. Alternatively, you can use a 64-bit compile worker or the NI LabVIEW FPGA Compile Cloud Service.

| |||||

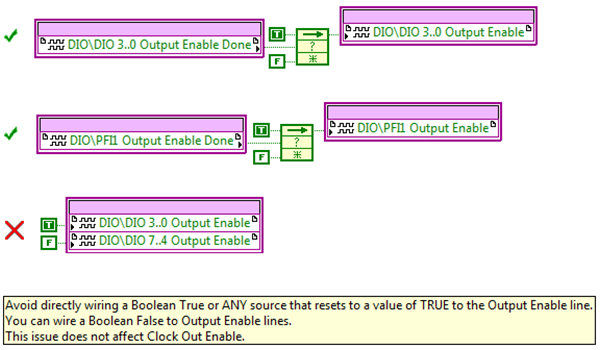

| 372623 | 5644R DIO Output Enable may not function as expected if wired to a Boolean True The DIO CLIP documentation includes the following statement: "The direction control should only be changed when the corresponding Output Enable Done bit is true; however, the Output Enable lines can be statically wired to either true or false." However, if you wire a Boolean True to an Output Enable line, the DIO can fail to enable, thus leaving the DIO outputs disabled. Workaround: Only change the Output Enable value from the default (False) when the Output Enable Done signal is true in the LabVIEW FPGA block diagram. For example, insert an Output Enable Done before the Output Enable signal. Wire the Output Enable Done to a Feedback Node that resets to false and wire a Boolean True to the input of the Feedback Node. Wire the output of the Feedback Node to the Output Enable, as shown in the following figure. You can also tie the Output Enable signals to controls that are written by software.

|

Related Topics:

Contact NI regarding this document or issues in the document. If you contact NI in regards to a specific issue, reference the ID number given in the document. The ID number contains the current issue ID number as well as the legacy ID number (use the current ID number when contacting NI). You can contact us through any of the normal support channels including phone, email, or the discussion forums. Visit the NI Website to contact us. Also contact us if you find a workaround for an issue that is not listed in the document.