NI InstrumentStudio™ Interactive Software

PXI Waveform Generators are shipped with an interactive soft front panel called InstrumentStudio for ready-to-run operation. You can also combine your PXI Waveform Generator with a PXI Oscilloscope into a single view.

Standard Waveform Generation

A waveform generator can output many types of standard functions, such as sine, square, triangle, ramp, or noise waveforms, and user-defined arbitrary waveforms using the NI-FGEN API in LabVIEW, LabWindows™/CVI, and .NET languages.

Recommendations for First-Time Users

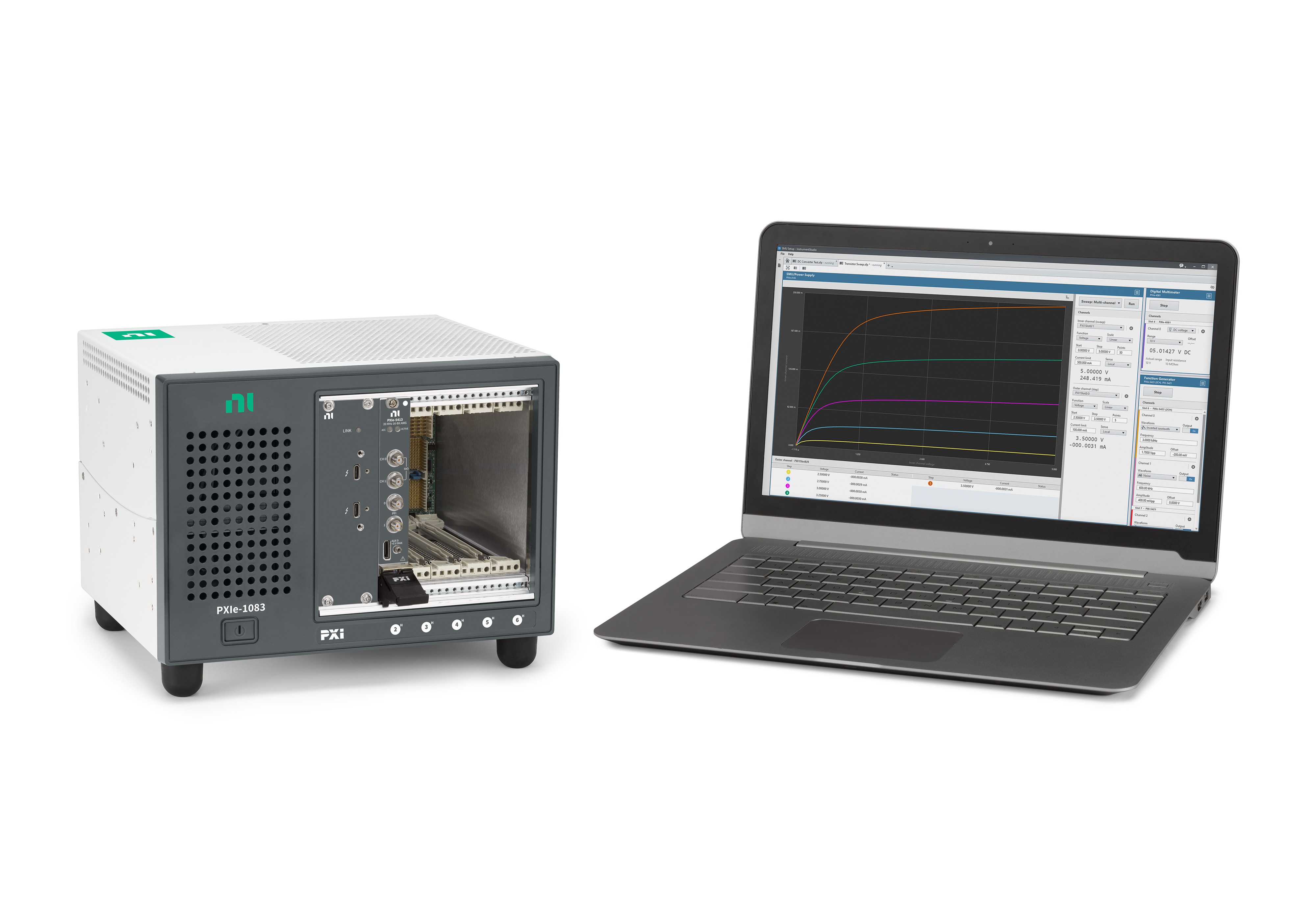

PXI Waveform Generator Bundle

The PXI Waveform Generator Bundle is a preconfigured set of one of NI’s most popular, high-quality waveform generators and a Thunderbolt™-controlled chassis so that you can get started with ease.

Featured Content

The PXIe-54x3 Arbitrary Waveform Generator Family

Receive a new fractional resampling architecture as well as waveform scripting and streaming capabilities with a PXIe-54x3 arbitrary waveform generator.

Onboard Signal Processing (OSP) on NI Signal Generators

The OSP technology on NI signal generators significantly extends waveform playback time and reduces the time required to compute and download waveform data by computing the waveform data using an FPGA.

The Right Waveform Generator for Your Application

Learn about the different types of analog signal generators to choose the right instrument to add to your measurement system.

Application Resource

Fundamentals of Building a Test System

Defining a test strategy and planning system investments are critical to reducing cost, optimizing your test-investment life cycle, and maximizing efficiency. Learn test strategies, best practices, and design tradeoffs for your test systems.

Related Products

PRODUCT SUPPORT RESOURCES

Support Library

Explore a wide range of support content, including examples and troubleshooting information.