乘函数

- 更新时间2026-02-19

- 阅读时长4分钟

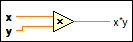

返回输入值的乘积。

如连线两个波形数据或动态数据类型至该函数,函数可显示错误输入和错误输出接线端。连线板显示该多态函数的默认数据类型。

输入/输出

x

—

x

—

x可以是标量数值、数值数组或簇、数值簇组成的数组等多种数据类型。  y

—

y

—

y可以是标量数字、数字数组或数字簇、数字簇数组等。  x*y

—

x*y

—

x*y是x与y的积。 |

不能使用该函数计算矩阵和向量的积。改用A x B VI。

两个矩阵相乘时,如第二个矩阵的行数和第一个矩阵的列数不相等,该函数将返回空矩阵。关于矩阵相乘的详细信息,见A x B VI。

将矩阵数据作为输入连线至函数时,该函数会被替代为一个含有可处理矩阵数据类型子VI的VI。得到的VI图标相同,但其中包括与矩阵相关的算法。如在输入端断开与矩阵的连线,该节点仍可作为VI使用。连线其他数据类型作为输入时,该节点可恢复为原来的函数。如数据类型连线至函数后导致基本数学运算的失败,则该函数可返回空矩阵或NaN。

定点详细信息

如连线定点值至加、减、乘和平方根等数值函数,则函数返回的值通常不会丢失任何字长的位数。但是,如运算所得结果超过LabVIEW能接受的最大字长,则可能发生溢出或凑整的情况。LabVIEW接受的最大字长为64位。通过数值节点属性对话框为定点数配置LabVIEW处理溢出或凑整的方法。

LabVIEW FPGA模块详细信息

下列信息适用于在FPGA VI中使用此对象。

| 单周期定时循环 | 支持。 |

| Usage | 多数FPGA终端包含一定数量的嵌入式乘数。FPGA模块编译器使用嵌入式乘数实现乘法运算,直至耗尽所有嵌入式乘数。FPGA终端缺少嵌入式乘数时,编译器使用类属逻辑门替代。此时,乘法函数将占用大量的FPGA资源。 如使用带有单精度浮点型数据类型的函数,关于资源使用、延时和单周期定时循环支持的信息,见使用单精度浮点型数据类型和判定在FPGA设计中使用何种数据类型。 |

| 定时 | 在单周期定时循环内-在单周期定时循环内使用函数时,组合逻辑延时与x或y(取两者中数据类型较长者)的位数成比例。 在单周期定时循环外-在单周期定时循环外使用函数时,每个函数使用一个时钟周期和一个寄存器。 如果配合使用函数和定点数据类型,溢出和取整模式可能影响定时。 |

| 资源 | 函数占用的FPGA资源与x或y(取两者中数据类型较长者)的位数成比例。考虑使用尽可能小的数据类型,以优化FPGA VI。如果配合使用函数和定点数据类型,溢出和取整模式可能影响资源的使用。 |

| 注 | 使用高吞吐率乘函数也可以在FPGA终端上执行定点数的数学运算与分析。 |

范例

请参考LabVIEW附带的下列示例文件。

- labview\examples\Numerics\Numeric Functions.vi