선택 함수

- 업데이트 날짜:2025-07-30

- 3분 (읽기 시간)

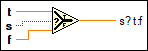

s의 값에 따라 t 입력 또는 f 입력에 연결된 값을 반환합니다. s가 참인 경우, 이 함수는 t에 연결된 값을 반환합니다. s가 거짓인 경우, 이 함수는 f에 연결된 값을 반환합니다.

커넥터 팬은 이 다형성 함수의 기본 데이터 타입을 디스플레이합니다.

입력/출력

t

—

t

—

t는 s가 참값을 전달한 경우 이 함수가 반환하는 값입니다. t and f must be of the same type, but they can have different numeric representations. s

—

s

—

s는 함수가 s? t:f에 t의 값을 반환할지 또는 f의 값을 반환할지 여부를 결정합니다. If you wire an error cluster to s and an error occurs, the error cluster passes a TRUE value to the function. Otherwise, the error cluster passes a FALSE value to the function. f

—

f

—

f는 s가 거짓값을 전달한 경우 이 함수가 반환하는 값입니다. t and f must be of the same type, but they can have different numeric representations. s? t:f

—

s? t:f

—

s? t:f는 s가 참인 경우 t에 연결된 값입니다. s? t:f는 s가 거짓인 경우 f에 연결된 값입니다. |

FPGA 모듈 세부사항

다음 세부사항은 FPGA VI에서 이 객체를 사용할 때 적용됩니다.

노트 다음 세부사항은 각 LabVIEW FPGA Module 버전에 따라 변경될 수 있습니다.

| Single-Cycle Timed 루프 | 지원함. |

| Usage | 이 함수를 단정도 부동소수 데이터 타입과 함께 사용하는 경우,단정도 부동소수 데이터 타입 사용하기 FPGA 설계에서 사용할 데이터 타입 결정하기에서는 리소스 사용, 지연 시간 및 단일 사이클 Timed 루프 지원의 의미에 대해 설명합니다. |

| 타이밍 | 단일 사이클 Timed 루프 내부 --단일 사이클 Timed 루프내에서 비교 함수를 사용하는 경우, 조합 로직 지연은 비교하는 데이터 타입의 폭에 비례합니다. 단일 사이클 Timed 루프 밖에서 --단일 사이클 Timed 루프밖에서 비교 함수를 사용하는 경우, 각 비교 함수는 하나의 클럭 사이클을 취합니다. 비교 함수를 고정 소수점 데이터 타입과 함께 사용하는 경우,오버플로우 및 반올림 모드는 타이밍에 영향을 미칠 수 있습니다. |

| 리소스 | 비교 함수는 비교하는 데이터 타입의 폭에 비례하여 FPGA 리소스를 사용합니다. |