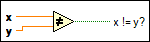

같지 않음? 함수

- 업데이트 날짜:2025-07-30

- 3분 (읽기 시간)

x가 y와 같지 않은 경우 참을 반환합니다. 그렇지 않은 경우, 이 함수는 거짓을 반환합니다. 이 함수의 비교 모드를 변경할 수 있습니다.

두 개의 행렬을 비교할 경우 기본 비교 모드는 집합 비교이며 이 함수는 스칼라를 반환합니다. 데이터 타입의 배열 또는 클러스터 비교를 같은 데이터 타입의 스칼라와 하고 불리언 배열 또는 클러스터를 생성할 수 있습니다. 커넥터 팬은 이 다형성 함수의 기본 데이터 타입을 디스플레이합니다.

입력/출력

x

—

x

—

x는y 와 비교할 값  y

—

y

—

y must be of the same type as x

x != y?

—

x != y?

—

x!=y?는 연산의 불리언 결과를 반환합니다. 배열을 비교할 때, x!=y?는 집합 비교 모드에서는 스칼라, 원소 비교 모드(기본)에서는 불리언 배열입니다. |

VI 서버 참조를 비교할 때 이 함수는 참조가 같은 기능 또는 같은 값인지에 상관 없이 두 개의 참조가 같은 객체를 참조할 때 거짓을 반환합니다. 예를 들면, 하나는 디지털 숫자형 컨트롤에 대한 엄격한 참조이고 다른 하나는 일반 참조이면 그들은 같은 객체를 참조하기 때문에 같습니다. 참조의 실제 값을 비교하려면 [타입 캐스트] 함수를 사용하여 참조를 32비트 부호 있는 정수로 변환합니다. 그 다음 [같지 않음?] 함수를 사용하여 정수를 비교합니다.

이전 상황과 마찬가지로 같은 LabVIEW 객체에 대해 로컬 참조와 원격 참조를 가질 경우 이 함수는 참을 반환합니다. 그러나 두 참조가 같은 객체를 참조하고 그 중 하나가 인증이 되어있고 다른 하나가 되어있지 않을때 이 함수는 여전히 거짓을 반환합니다.

행렬 데이터를 입력으로 이 함수에 연결할 때, 행렬 데이터 타입을 사용하는 SubVI를 포함하는 VI는 함수를 대체합니다. 결과 VI는 같은 아이콘을 가지지만 행렬 특정 알고리즘을 포함합니다. 입력으로부터 행렬을 연결 해제할 경우 노드는 VI를 남깁니다. 다른 데이터 타입을 입력으로 연결하여 원래 함수를 복구합니다. 데이터 타입을 함수에 연결하고 데이터 타입이 기본 수학 연산에서 실패를 유발할 경우, 함수는 빈 행렬 또는 NaN을 반환합니다.

FPGA 모듈 세부사항

다음 세부사항은 FPGA VI에서 이 객체를 사용할 때 적용됩니다.

| Single-Cycle Timed 루프 | 지원함. |

| Usage | 이 함수를 단정도 부동소수 데이터 타입과 함께 사용하는 경우,단정도 부동소수 데이터 타입 사용하기 FPGA 설계에서 사용할 데이터 타입 결정하기에서는 리소스 사용, 지연 시간 및 단일 사이클 Timed 루프 지원의 의미에 대해 설명합니다. |

| 타이밍 | 단일 사이클 Timed 루프 내부 --단일 사이클 Timed 루프내에서 비교 함수를 사용하는 경우, 조합 로직 지연은 비교하는 데이터 타입의 폭에 비례합니다. 단일 사이클 Timed 루프 밖에서 --단일 사이클 Timed 루프밖에서 비교 함수를 사용하는 경우, 각 비교 함수는 하나의 클럭 사이클을 취합니다. 비교 함수를 고정 소수점 데이터 타입과 함께 사용하는 경우,오버플로우 및 반올림 모드는 타이밍에 영향을 미칠 수 있습니다. |

| 리소스 | 비교 함수는 비교하는 데이터 타입의 폭에 비례하여 FPGA 리소스를 사용합니다. |

예제

LabVIEW 포함되는 다음 예제 파일을 참조하십시오.

- labview\examples\Comparison\Comparison Functions.vi