1D 배열 끼워넣기

- 업데이트 날짜:2025-07-30

- 2분 (읽기 시간)

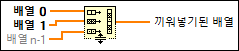

입력 배열의 대응하는 원소를 하나의 출력 배열에 인터리브합니다.

입력/출력

배열

—

배열

—

배열 0..n-1은 반드시 1D 여야 합니다. 입력 배열의 크기가 같지 않은 경우, 끼워넣기된 배열의 원소 개수는 가장 작은 입력 배열의 원소 개수를 입력 배열의 개수로 곱한 것과 같습니다.  배열

—

배열

—

끼워넣기된 배열

—

끼워넣기된 배열

—

끼워넣기된 배열[0]은 배열 0[0]을, 끼워넣기된 배열[1]은 배열 1[0]을, 끼워넣기된 배열[n-1]은 배열 n-1[0]을, 끼워넣기된 배열[n]은 배열 0[1]을 포함하며 이후도 마찬가지입니다. 이 때 n은 입력 터미널의 개수입니다. 다음 테이블은 입력 배열의 원소가 끼워넣기된 배열에 어떤 영향을 미치는지를 보여줍니다.

|

FPGA 모듈 세부사항

다음 세부사항은 FPGA VI에서 이 객체를 사용할 때 적용됩니다.

노트 다음 세부사항은 각 LabVIEW FPGA Module 버전에 따라 변경될 수 있습니다.

| Single-Cycle Timed 루프 | 지원함. |

| Usage | LabVIEW FPGA Module 은 컴파일 시 단일 크기로 결정되는 1차원 배열만 지원합니다. 상수 또는 상수가 아닌 입력을 사용할 수 있습니다. |

| 타이밍 | 이 함수는 내부 레지스터를 포함하지 않기 때문에 클럭 사이클을 실행할 필요가 없습니다. |

| 리소스 | 이 함수는 순수하게 와이어 연결 작업이기 때문에 FPGA 리소스를 사용하지 않습니다. |