選択関数

- 更新日2026-02-04

- 4分で読める

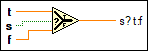

sの値に応じて、t入力またはf入力に配線された値を返します。sがTRUEの場合、この関数はtに配線された値を返します。sがFALSEの場合、この関数はfに配線された値を返します。

コネクタペーンには、この多態性関数のデフォルトのデータタイプが表示されます。

入力/出力

t

—

t

—

tは、sがTRUE値の場合にこの関数が返す値です。 t and f must be of the same type, but they can have different numeric representations. s

—

s

—

sは、s? t:fにtまたはfのどちらの値が返されるかを決定します。 If you wire an error cluster to s and an error occurs, the error cluster passes a TRUE value to the function. Otherwise, the error cluster passes a FALSE value to the function. f

—

f

—

fは、sがFALSE値の場合にこの関数が返す値です。 t and f must be of the same type, but they can have different numeric representations. s? t:f

—

s? t:f

—

s? t:fには、sがTRUEの場合はtに配線された値、sがFALSEの場合はfに配線された値が返されます。 |

LabVIEW FPGAモジュールの詳細

以下の詳細は、このオブジェクトをFPGA VIで使用する場合に適用されます。

メモ 以下の詳細は、LabVIEW FPGAモジュールの各バージョンごとに変更される可能性があります。

| シングルサイクルタイミングループ | サポートあり |

| Usage | この関数を単精度浮動小数点データタイプと使用する場合、リソース使用、レイテンシ、およびシングルサイクルタイミングループのサポートへの影響については、 単精度浮動小数点データタイプを使用 するおよび FPGA設計で使用するデータタイプを決定する トピックを参照してください。 |

| タイミング | シングルサイクルタイミングループの内側―比較関数をシングルサイクルタイミングループ内で使用すると、組み合わせ論理の遅延は比較するデータタイプの幅に比例します。 シングルサイクルタイミングループの外側―比較関数をシングルサイクルタイミングループの外側で使用すると、各比較関数に1クロックサイクルが必要となります。 固定小数点データタイプを扱う比較関数では、オーバーフローモードと丸め込みモードによってタイミングが影響を受ける可能性があります。 |

| リソース | 比較関数が使用するFPGAリソースの量は、比較するデータタイプの幅に比例します。 |