インタリーブ1D配列

- 更新日2025-07-30

- 3分で読める

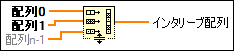

入力配列から対応する要素を単一の出力配列にインタリーブします。

入力/出力

配列

—

配列

—

配列0..n-1は、1Dである必要があります。入力配列のサイズが同じでない場合、交互配置配列の要素数は、最小の入力配列の最小要素数を入力配列の数で乗算した値と等しくなります。  配列

—

配列

—

インタリーブ配列

—

インタリーブ配列

—

交互配置配列[0]には配列0[0]が含まれ、交互配置配列[1]には配列1[0]が含まれ、交互配置配列[n-1]には配列n-1[0]が含まれ、交互配置配列[n]には配列0 [1]が含まれます。ここで、nは入力端子の数です。 以下の表は、入力配列の要素が交互配置配列に対して与える影響を示しています。

|

FPGAモジュールの詳細

以下の説明は、このオブジェクトをFPGA VIで使用する場合に適用されます。

メモ 以下の詳細は、LabVIEW FPGAモジュールのバージョンごとに変更される場合があります。

| シングルサイクルタイミングループ | サポートあり |

| Usage | LabVIEW FPGAモジュールは、コンパイル時に固定サイズに決定される1次元配列のみをサポートしています。定数と定数以外の入力を使用できます。 |

| タイミング | この関数は、内部レジスタを持たないため実行クロックサイクルは必要ありません。 |

| リソース | この関数は単なる配線操作であるため、FPGAリソースを必要としません。 |