PCIe-5775 Specifications

- Updated2025-04-25

- 9 minute(s) read

PCIe-5775 Specifications

Specifications

Definitions

Warranted specifications describe the performance of a model under stated operating conditions and are covered by the model warranty.

Characteristics describe values that are relevant to the use of the model under stated operating conditions but are not covered by the model warranty.

- Typical specifications describe the performance met by a majority of models.

- Nominal specifications describe an attribute that is based on design, conformance testing, or supplemental testing.

Specifications are Typical unless otherwise noted.

PCIe-5775 Pinout

Digital I/O

Connector | Molex™ Nano-Pitch I/O™ |

5.0 V Power | ±5%, 50 mA maximum, nominal |

| Signal | Type | Direction |

|---|---|---|

| MGT Tx± <0..3>1 Multi-gigabit transceiver (MGT) signals are available on devices with KU040 and KU060 FPGAs only.[1] | Xilinx UltraScale GTH | Output |

| MGT Rx± <0..3>[1] | Xilinx UltraScale GTH | Input |

| DIO <0..7> | Single-ended | Bidirectional |

| 5.0 V | DC | Output |

| GND | Ground | — |

Digital I/O Single-Ended Channels

Number of channels | 8 |

Signal type | Single-ended |

Voltage families | 3.3 V, 2.5 V, 1.8 V, 1.5 V, 1.2 V |

Input impedance | 100 kΩ, nominal |

Output impedance | 50 Ω, nominal |

Direction control | Per channel |

Minimum required direction change latency | 200 ns |

Maximum output toggle rate | 60 MHz with 100 μA load, nominal |

| Voltage Family (V) | VIL (V) | VIH (V) | VOL (100 µA Load) (V) | VOH (100 µA Load) (V) | Maximum DC Drive Strength (mA) |

|---|---|---|---|---|---|

| 3.3 | 0.8 | 2.0 | 0.2 | 3.0 | 24 |

| 2.5 | 0.7 | 1.6 | 0.2 | 2.2 | 18 |

| 1.8 | 0.62 | 1.29 | 0.2 | 1.5 | 16 |

| 1.5 | 0.51 | 1.07 | 0.2 | 1.2 | 12 |

| 1.2 | 0.42 | 0.87 | 0.2 | 0.9 | 6 |

Digital I/O High-Speed Serial MGT[3]3 For detailed FPGA and High-Speed Serial Link specifications, refer to Xilinx documentation.

Data rate | 500 Mbps to 16.375 Gbps, nominal |

Number of Tx channels | 4 |

Number of Rx channels | 4 |

I/O AC coupling capacitor | 100 nF |

MGT TX± Channels[4]4 For detailed FPGA and High-Speed Serial Link specifications, refer to Xilinx documentation.

MGT RX± Channels

| |||||||

Differential input resistance | 100 Ω, nominal | ||||||

I/O coupling | DC-coupled, requires external capacitor | ||||||

Reconfigurable FPGA

PCIe-5775 modules are available with multiple FPGA options. The following table lists the FPGA specifications for the PCIe-5775 FPGA options.

| KU035 | KU040 | KU060 | |

|---|---|---|---|

| LUTs | 203,128 | 242,200 | 331,680 |

| DSP48 slices (25 × 18 multiplier) | 1,700 | 1,920 | 2,760 |

| Embedded Block RAM | 19.0 Mb | 21.1 Mb | 38.0 Mb |

| Data Clock Domain | 200 MHz, 16 samples per cycle per channel (dual channel mode), 32 samples per cycle (single channel mode) | ||

| Timebase reference sources | Onboard 100 MHz oscillator | ||

| Data transfers | DMA, interrupts, programmed I/O | DMA, interrupts, programmed I/O, multi-gigabit transceivers | |

| Number of DMA channels | 59 | ||

Onboard DRAM

Memory size | 4 GB (2 banks of 2 GB) |

DRAM clock rate | 1064 MHz |

Physical bus width | 32 bit |

LabVIEW FPGA DRAM clock rate | 267 MHz |

LabVIEW FPGA DRAM bus width | 256 bit per bank |

Maximum theoretical data rate | 17 GB/s (8.5 GB/s per bank) |

Analog Input

General Characteristics

Number of channels | 2, single-ended, simultaneously sampled | ||||||

Connector type | SMA | ||||||

Input impedance | 50 Ω | ||||||

Input coupling | AC | ||||||

| |||||||

| |||||||

Analog-to-digital converter (ADC) | ADC12DJ3200, 12-bit resolution | ||||||

239 ns | |||||||

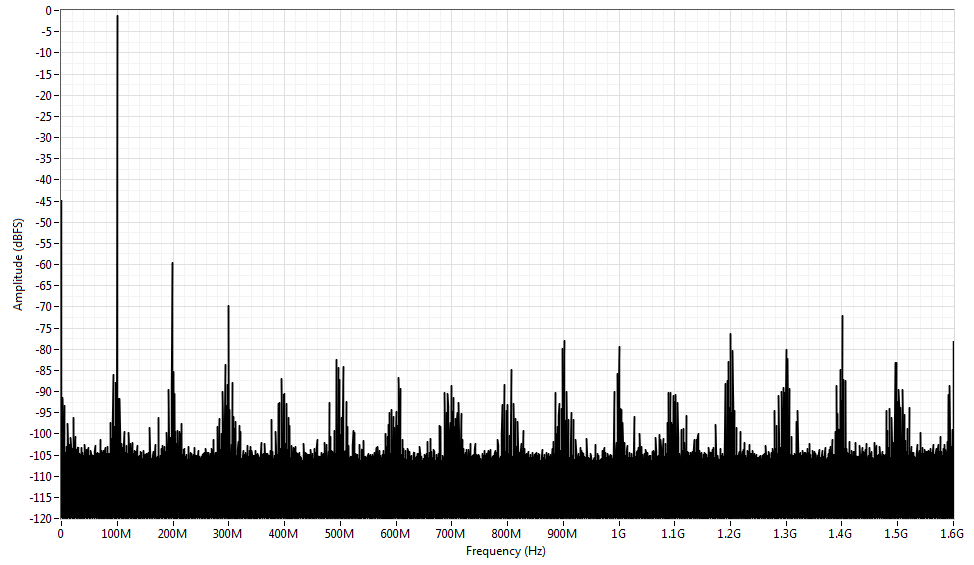

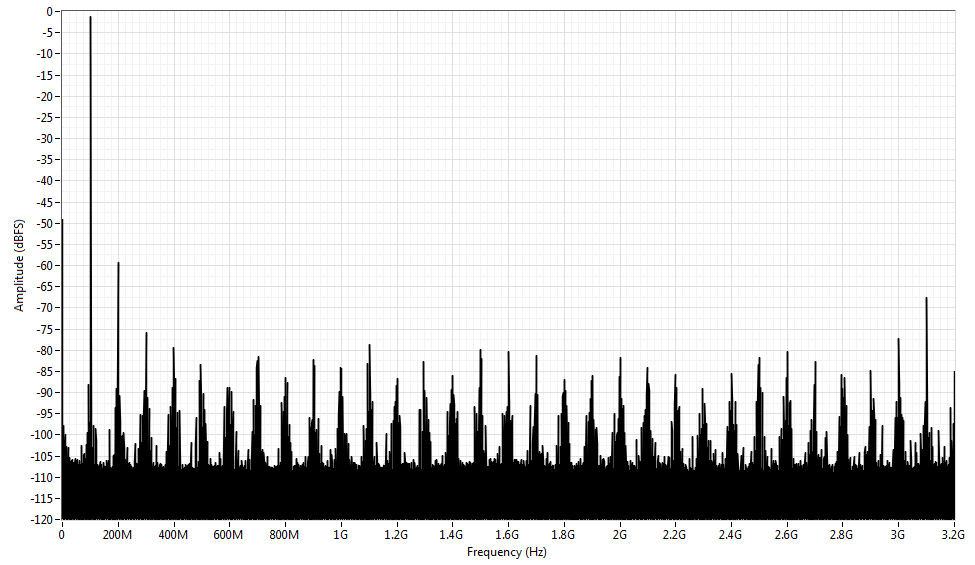

Typical Specifications

| Input Frequency | |||||

|---|---|---|---|---|---|

| 99.9 MHz | 399 MHz | 999 MHz | 1.999 GHz | 2.499 GHz | |

| SNR8 Measured with a -1 dBFS signal and corrected to full-scale. 3.2 kHz resolution bandwidth. [] (dBFS) | 56.0 | 55.6 | 54.7 | 52.9 | 51.6 |

| SINAD[] (dBFS) | 55.5 | 55.0 | 54.0 | 51.8 | 50.8 |

| SFDR (dBc) | -64.9 | -63.4 | -62.7 | -59.9 | -58.6 |

| ENOB9 Calculated from SINAD and corrected to full scale.[] (bits) | 8.9 | 8.8 | 8.7 | 8.3 | 8.1 |

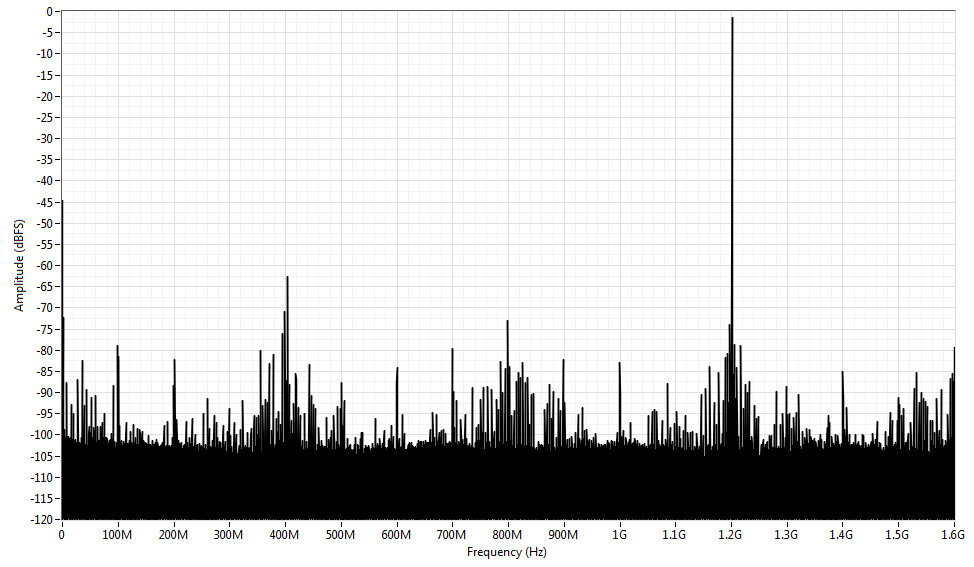

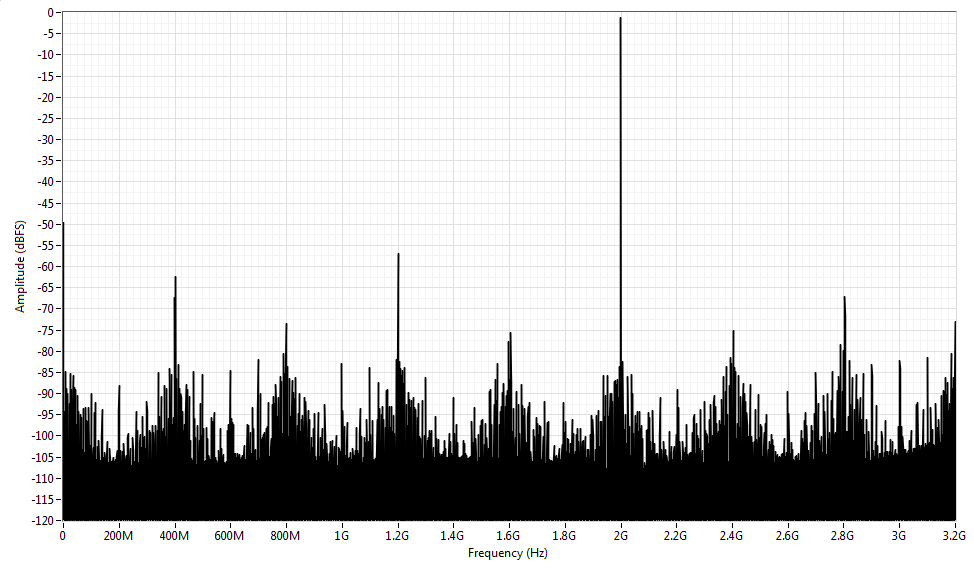

| Input Frequency | |||||

|---|---|---|---|---|---|

| 99.9 MHz | 399 MHz | 999 MHz | 1.999 GHz | 2.499 GHz | |

| SNR[] (dBFS) | 54.6 | 54.2 | 52.4 | 49.7 | 48.9 |

| SINAD[] (dBFS) | 54.4 | 53.9 | 52.1 | 49.4 | 48.6 |

| SFDR (dBc) | -61.7 | -60.4 | -56.1 | -51.7 | -51.1 |

| ENOB[] (bits) | 8.7 | 8.7 | 8.4 | 7.9 | 7.8 |

| Mode |

|

|

|

|---|---|---|---|

| Dual channel | 14.4 | -143.8 | -149.2 |

| Single channel | 9.8 | -147.2 | -152.6 |

| |||||||||||||

REF/CLK IN

General Characteristics

Connector type | SMA | ||||||

Input impedance | 50 Ω | ||||||

Input coupling | AC | ||||||

Input voltage range | 0.35 V pk-pk to 3.5 V pk-pk, nominal | ||||||

Absolute maximum voltage | ±12 V DC, 4 V pk-pk AC | ||||||

Duty cycle | 45% to 55% | ||||||

| |||||||

| Clock Configuration | External Clock Frequency | Description |

|---|---|---|

| Internal Baseboard Reference Clock[14]14 Default clock configuration. | 10 MHz | The internal Sample Clock locks to the 10 MHz Reference Clock provided from the FPGA baseboard. |

| External Reference Clock (REF/CLK IN) | 10 MHz [15]15 The external Reference Clock must be accurate to ±25 ppm. | The internal Sample Clock locks to an external Reference Clock, which is provided through the REF/CLK IN front panel connector. |

| External Sample Clock (REF/CLK IN) | 2.8 GHz to 3.2 GHz | An external Sample Clock can be provided through the REF/CLK IN front panel connector. |

Bus Interface

Card edge form factor | PCI Express Gen-3 x8 |

Slot compatibility | x8 and x16 PCI Express slots |

Maximum Power Requirements

+3.3 V | 4.5 A |

+12 V | 5 A |

Maximum total power | 75 W |

Physical

Dimensions (including I/O bracket, not including connectors) | 12.6 cm × 26.3 cm × 4 cm (5.0 in. × 10.4 in. × 1.6 in.) |

Weight | 990 g (35 oz) |

PCI Express mechanical form factor | Standard height, three-quarter length, double slot |

Integrated air mover (fan) | Yes |

Maximum rear panel exhaust airflow | 84 m3/h (50 CFM) (without any chassis impedance) |

Environment

Maximum altitude | 2,000 m (800 mbar) (at 25 °C ambient temperature) |

Pollution Degree | 2 |

Indoor use only.

Operating Environment

Operating temperature, local[16]16 For PCI Express adapter cards with integrated air movers, NI defines the local operational ambient environment to be at the fan inlet. For cards without integrated air movers, NI defines the local operational ambient environment to be 25 mm (1 in.) upstream of the leading edge of the card. | 0 °C to 45 °C |

Operating humidity | 10% to 90% RH, noncondensing |

Storage Environment

Ambient temperature range | -20 °C to 70 °C |

Relative humidity range | 5% to 95% RH, noncondensing |

1 Multi-gigabit transceiver (MGT) signals are available on devices with KU040 and KU060 FPGAs only.

2 Voltage levels are guaranteed by design through the digital buffer specifications.

3 For detailed FPGA and High-Speed Serial Link specifications, refer to Xilinx documentation.

4 For detailed FPGA and High-Speed Serial Link specifications, refer to Xilinx documentation.

5 800 mV pk-pk when transmitter output swing is set to the maximum setting.

6 SMA input to LabVIEW diagram

7 Normalized to 10 MHz.

8 Measured with a -1 dBFS signal and corrected to full-scale. 3.2 kHz resolution bandwidth.

9 Calculated from SINAD and corrected to full scale.

10 Measured using channel AI0. Spectral performance may be degraded using channel AI1.

11 Excludes fixed interleaving spur (Fs/2 spur).

12 Integrated from 3.2 kHz to 20 MHz. Includes the effects of the converter aperture uncertainty and the clock circuitry jitter. Excludes trigger jitter.

13 Integrated from 1 kHz to 30 MHz. Includes the effects of the converter aperture uncertainty, converter PLL circuitry, and the clock circuitry jitter. Excludes trigger jitter.

14 Default clock configuration.

15 The external Reference Clock must be accurate to ±25 ppm.

16 For PCI Express adapter cards with integrated air movers, NI defines the local operational ambient environment to be at the fan inlet. For cards without integrated air movers, NI defines the local operational ambient environment to be 25 mm (1 in.) upstream of the leading edge of the card.