Transferring Data between Clock Domains Using FIFOs

- Updated2023-02-17

- 3 minute(s) read

Transferring Data between Clock Domains Using FIFOs

Before completing this task, verify that FIFOs are the best data storage and transfer option for your application.

Use FIFOs to move data between Clock-Driven Loops to ensure that every data sample is valid and that every data sample written by one loop is read by the other loop.

What to Use

What to Do

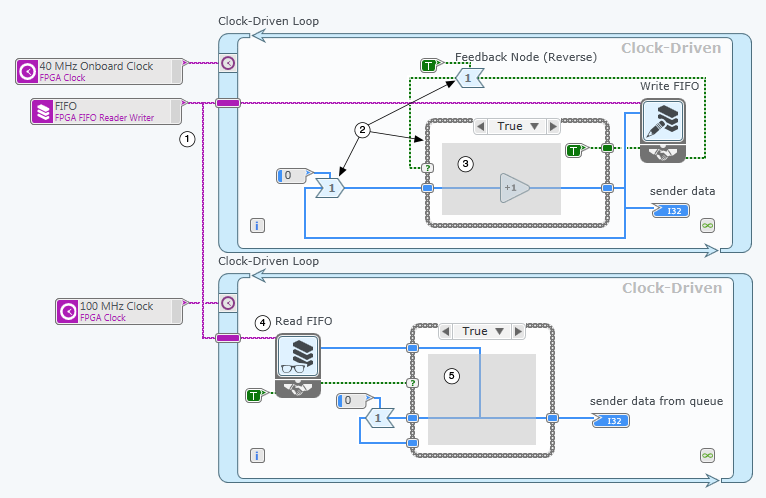

Create the following diagram to transfer data between clock domains without data loss.

Customize the gray sections for your unique programming goals.

|

|

Use a reference to a local FIFO implemented in block RAM or look-up tables to ensure that the Write FIFO and Read FIFO nodes in separate Clock-Driven Loops access the same FIFO. To implement a FIFO in block RAM or look-up tables, select the FIFO in the resource collection. In the Behavior section of the Item tab, ensure Storage is set to Block RAM or Look-up table. |

|

|

Use a Case Structure and Feedback Nodes to retain data samples for multiple clock cycles when the other Clock-Driven Loop is not ready for data. |

|

|

Perform operations inside the Case Structure on the data you write to the FIFO shared between clock domains. Wire the data from the Case Structure to both Write FIFO and the sender data indicator. For the False case, wire the data from the previous clock cycle through the Case Structure. Also, add a False constant to the Case Structure and wire the False constant to input valid of Write FIFO to communicate that the data is not valid. |

|

|

Use Read FIFO to read and remove the oldest element from the FPGA FIFO and determine whether the read operation is successful. Wire a True constant to ready for output of Read FIFO to communicate that the data from the other Clock-Driven Loop is ready to be read. Read FIFO reads every sample sent from the other Clock-Driven Loop. |

|

|

Perform operations on the data from the other clock domain. To preserve the last processed data sample produced by this Clock-Driven Loop when no new valid samples are available, use a Case Structure and a Feedback Node to retain a data sample for multiple clock cycles. The following image shows the False case of the Case Structure in this section. |

Examples

Search within the programming environment to access the following installed example: Multiple Clock Domains.

Related Information

- Data Transfer Using FIFOs

A FIFO is a data structure that holds elements in the order they are received and provides access to those elements using a first-in, first-out basis.

- Storing and Transferring Data

Store and transfer data on an FPGA using resource items like FIFOs, memory items, FPGA registers, or handshake items. You can also transfer data on an FPGA using panel controls or indicators.

- Transferring Data Using a Memory Item

- Transferring Data between Clock Domains Using Registers