Auswählen - Funktion

- Aktualisiert2025-07-30

- 3 Minute(n) Lesezeit

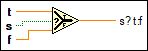

Gibt je nach dem Wert von s den Wert am Eingang t oder f aus. Wenn s TRUE ist, wird der Wert an t ausgegeben. Bei FALSE wird f ausgegeben.

Die Standarddatentypen für diese polymorphe Funktion sind im Anschlussfeld dargestellt.

Ein-/Ausgänge

t

—

t

—

t ist der Wert, den die Funktion ausgibt, wenn s TRUE ist. t and f must be of the same type, but they can have different numeric representations. s

—

s

—

s bestimmt, ob die Funktion den Wert von t oder f an s? t:f ausgibt. If you wire an error cluster to s and an error occurs, the error cluster passes a TRUE value to the function. Otherwise, the error cluster passes a FALSE value to the function. f

—

f

—

f ist der Wert, den die Funktion ausgibt, wenn s FALSE ist. t and f must be of the same type, but they can have different numeric representations. s? t:f

—

s? t:f

—

s? t:f hat den Wert t, wenn s TRUE ist. s? t:f hat den Wert f, wenn s FALSE ist. |

Details zum FPGA-Modul

Die folgenden Details gelten, wenn Sie dieses Objekt in einem FPGA-VI verwenden.

| SCTL (Single-Cycle Timed Loop) | Unterstützt. |

| Verwendung | Wenn Sie diese Funktion mit dem Fließkomma-Datentyp mit einfacher Genauigkeit verwenden, lesen Sie den Abschnitt Verwendung des Fließkomma-Datentyps mit einfacher Genauigkeit und Entscheidung Welcher Datentyp in FPGA-Entwürfen verwendet wird. |

| Timing | In Single-Cycle Timed Loop--Wenn Sie Vergleichsfunktionen in einer Single-Cycle Timed Loop verwenden, ist die kombinatorische Verzögerung proportional zur Breite der Datentypen, die Sie vergleichen. Außerhalb einer SCTL--Bei Verwendung von Vergleichsfunktionen außerhalb einer SCTL dauert jede Vergleichsfunktion eine Taktperiode. Wenn Sie die Vergleichsfunktionen mit dem Festkommadatentyp verwenden, können sich die Überlauf- und Rundungsmodi auf das Timing auswirken. |

| Ressourcen | Die Vergleichsfunktionen verwenden FPGA-Ressourcen proportional zur Breite der verglichenen Datentypen. |