Auf nächste ganze Zahl runden - Funktion

- Aktualisiert2025-07-30

- 2 Minute(n) Lesezeit

Rundet den Eingangswert auf die nächste ganze Zahl. Wenn der Wert der Eingabe genau zwischen zwei ganzen Zahlen liegt, gibt die Funktion den nächsten geraden ganzzahligen Wert aus.

Wenn Zahl beispielsweise 1,5 oder 2,5 lautet, ist Nächster ganzzahliger Wert 2.

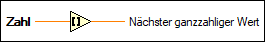

Die Standarddatentypen für diese polymorphe Funktion sind im Anschlussfeld dargestellt.

Ein-/Ausgänge

Zahl

—

Zahl

—

Zahl kann zum Beispiel ein Skalar, ein Array oder Cluster aus numerischen Werten oder ein Array aus Clustern mit numerischen Werten sein.  Nächster ganzzahliger Wert

—

Nächster ganzzahliger Wert

—

Nächster ganzzahliger Wert ist die dem Zahl nächstgelegene ganze Zahl. Bei Zeitangaben wird auf die nächste oder vorherige Sekunde gerundet. When Zahl is in the form of a + bi, that is, when Zahl is complex, the function returns a complex number defined by the nearest integer to the real and imaginary parts of Zahl. The following equation defines Nächster ganzzahliger Wert: Nächster ganzzahliger Wert(x) = nächster ganzzahliger Wert(a) + i * nächster ganzzahliger Wert(b) |

Details zum FPGA-Modul

Die folgenden Details gelten, wenn Sie dieses Objekt in einem FPGA-VI verwenden.

| SCTL (Single-Cycle Timed Loop) | Unterstützt. |

| Verwendung | Diese Funktion unterstützt den Single-Precision Floating-Point Data Type nicht. |

| Timing | In Single-Cycle Timed Loop--Wenn Sie diese Funktion in einer Single-Cycle Timed Loop verwenden, ist die Verzögerung der kombinatorischen Logik proportional zur Anzahl der Bits in Zahl. Außerhalb einer Single-Cycle Timed Loop--Wenn Sie diese Funktion außerhalb einer Single-Cycle Timed Loop verwenden, benötigt sie eine Taktperiode und verwendet ein Register. Die Überlauf- und Rundungsmodi können das Timing beeinflussen. |

| Ressourcen | Diese Funktion benötigt FPGA-Ressourcen proportional zur Anzahl der Bits. |

Beispiele

Die folgenden Beispieldateien sind in LabVIEW enthalten.

- labview\examples\Numerics\Numeric Functions.vi