Absoluter Wert - Funktion

- Aktualisiert2025-07-30

- 3 Minute(n) Lesezeit

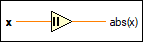

Gibt den Absolutwert des Eingangswerts aus.

Die Standarddatentypen für diese polymorphe Funktion sind im Anschlussfeld dargestellt.

Ein-/Ausgänge

x

—

x

—

x kann beispielsweise eine skalare Zahl, ein Festkommawert, ein Array oder Cluster aus Zahlen oder ein Array aus numerischen Clustern sein. x darf kein vorzeichenloser Integer sein, da dadurch ausschließlich nicht negative ganzzahlige Werte dargestellt werden.  abs(x)

—

abs(x)

—

abs(x) ist der absolute Wert von x. Wenn x die Form x = a + bi hat, also eine komplexe Zahl ist, wird abs(x) durch folgende Gleichung ermittelt:

|

Wenn Sie diese Funktion mit einer Matrix verbinden, wird die Funktion durch ein VI ersetzt, dessen SubVIs mit dem Datentyp "Matrix" arbeiten. Das resultierende VI hat das gleiche Symbol, enthält aber einen matrizenspezifischen Algorithmus. Wenn Sie die Matrizen von den Eingängen trennen, bleibt der Knoten weiterhin ein VI. Zum Wiederherstellen der Originalfunktion müssen am Eingang andere Datentypen anliegen. Wenn Sie einen Datentyp mit einer Funktion verbinden und aufgrund dieses Datentyps eine grundlegende mathematische Operation nicht funktioniert, gibt die Funktion NaN aus.

Wenn der absolute Wert von x außerhalb des Bereichs des Datentyps von x liegt, läuft abs(x) auf einen Wert innerhalb des Bereichs des Datentyps über. Wenn beispielsweise x ein 8-Bit Integer und der Wert von x -128 ist, gibt abs(x) -128 aus, da 128 außerhalb des Bereichs des 8-Bit-Integers liegt (-128 bis 127).

Details zum FPGA-Modul

Die folgenden Details gelten, wenn Sie dieses Objekt in einem FPGA-VI verwenden.

| SCTL (Single-Cycle Timed Loop) | Unterstützt. |

| Verwendung | Wenn Sie diese Funktion mit dem Fließkomma-Datentyp mit einfacher Genauigkeit verwenden, lesen Sie den Abschnitt Verwendung des Fließkomma-Datentyps mit einfacher Genauigkeit und Entscheidung Welcher Datentyp in FPGA-Entwürfen verwendet wird. |

| Timing | In Single-Cycle Timed Loop--Wenn Sie diese Funktion in einer Single-Cycle Timed Loop verwenden, ist die Verzögerung der kombinatorischen Logik proportional zur Anzahl der Bits in x. Außerhalb einer Single-Cycle Timed Loop--Wenn Sie diese Funktion außerhalb einer Single-Cycle Timed Loop verwenden, benötigt sie eine Taktperiode und verwendet ein Register. Wenn Sie diese Funktion mit dem Festkomma-Datentyp verwenden, können sich die Überlauf- und Rundungsmodi auf das Timing auswirken. |

| Ressourcen | Diese Funktion benötigt FPGA-Ressourcen proportional zur Anzahl der Bits in x. Wenn Sie diese Funktion mit dem Festkomma-Datentyp verwenden, können sich die Überlauf- und Rundungsmodi auf die Ressourcen auswirken. |

Beispiele

Die folgenden Beispieldateien sind in LabVIEW enthalten.

- labview\examples\Numerics\Numeric Functions.vi