Rotieren - Funktion

- Aktualisiert2026-02-04

- 3 Minute(n) Lesezeit

Verschiebt x um die durch y angegebene Bit-Anzahl.

Die Standarddatentypen für diese polymorphe Funktion sind im Anschlussfeld dargestellt.

Ein-/Ausgänge

y

—

y

—

y bestimmt die Zahl der Bits in x, die von der Funktion gedreht werden. If y is greater than 0, the function shifts the first y bits at the left end of x to the right end. If y is less than 0, the function shifts the first y bits at the right end of x to the left end. x

—

x

—

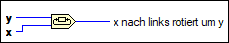

Wenn x ein 8-, 16-, 32- oder 64-Bit-Integer ist, so ergeben y, y ± 8, y ± 16, y ± 32 oder y ± 64 für jeden Wert jeweils den gleichen Ausgabewert wie y. For example, if x is an 8-bit integer, y = 1 and y = 9 yield the same result. x nach links rotiert um y

—

x nach links rotiert um y

—

x nach links rotiert um y ist das Ergebnis der Rotation. The data type of x nach links rotiert um y is determined by the data type of the x input. |

In der folgenden Tabelle wird dargestellt, wie x und y beeinflussen, wie x um y nach links gedreht wird:

| y | x | x nach links rotiert um y | Kommentare |

|---|---|---|---|

| 1 | 3 (00000011) | 6 (00000110) | Diese Funktion verschiebt das erste Bit am linken Ende (0) an das rechte Ende. |

| 2 | 3 (00000011) | 12 (00001100) | Diese Funktion verschiebt die ersten zwei Bits am linken Ende (00) an das rechte Ende. |

| –3 | 3 (00000011) | 96 (01100000) | Diese Funktion verschiebt die ersten drei Bits am rechten Ende (011) an das linke Ende. |

Details zum LabVIEW FPGA Module

Die folgenden Details gelten, wenn Sie dieses Objekt in einem FPGA-VI verwenden.

| SCTL (Single-Cycle Timed Loop) | Unterstützt. |

| Verwendung | k. A. |

| Timing | In Single-Cycle Timed Loop--Wenn Sie diese Funktion in einer Single-Cycle Timed Loop verwenden, ist die Verzögerung der kombinatorischen Logik proportional zur Anzahl der Bits in x. Außerhalb einer Single-Cycle Timed Loop--Wenn Sie diese Funktion außerhalb einer Single-Cycle Timed Loop verwenden, benötigt sie eine Taktperiode und verwendet ein Register. |

| Ressourcen | Diese Funktion benötigt FPGA-Ressourcen proportional zur Anzahl der Bits in x. |