1D-Arrays verflechten

- Aktualisiert2025-07-30

- 2 Minute(n) Lesezeit

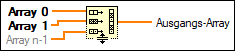

Verflechtet die einander entsprechenden Elemente der Eingangs-Arrays zu einem Ausgangs-Array.

Ein-/Ausgänge

Array

—

Array

—

Array 0..n-1 muss 1D sein. Wenn die Eingangs-Arrays nicht die gleiche Größe haben, ist die Anzahl der Elemente in Ausgangs-Array gleich der Anzahl der Elemente im kleinsten Eingangs-Array multipliziert mit der Anzahl der Eingangs-Arrays.  Array

—

Array

—

Ausgangs-Array

—

Ausgangs-Array

—

Ausgangs-Array[0] enthält Array0[0]; Ausgangs-Array[1] enthält Array1[0]; Ausgangs-Array[n-1] enthält Array n-1[0]; Ausgangs-Array[n] enthält Array0[1] und so weiter, wobei n der Anzahl der Eingangsanschlüsse entspricht. In der folgenden Tabelle sehen Sie, welche Auswirkung die Elemente im Eingangs-Array auf das Ausgangs-Array haben.

|

Details zum FPGA-Modul

Die folgenden Details gelten, wenn Sie dieses Objekt in einem FPGA-VI verwenden.

| SCTL (Single-Cycle Timed Loop) | Unterstützt. |

| Verwendung | Das LabVIEW FPGA Module unterstützt nur eindimensionale Arrays, die sich während der Kompilierung auf eine Größe auflösen. Sie können konstante oder nicht konstante Eingänge verwenden. |

| Timing | Diese Funktion erfordert keine Taktperioden, da sie kein internes Register enthält. |

| Ressourcen | Diese Funktion beansprucht keine FPGA-Ressourcen, da es sich um eine reine Verbindungsoperation handelt. |