Exklusiv-ODER - Funktion

- Aktualisiert2026-02-04

- 2 Minute(n) Lesezeit

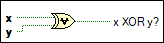

Wendet ein logisches Exklusiv-ODER (XOR) auf die Eingänge an. Die Eingangsgrößen müssen beide boolesche Werte, numerische Werte oder Fehler-Cluster sein. Wenn beide Eingänge TRUE oder beide Eingänge FALSE sind, gibt die Funktion ein FALSE aus. Ansonsten wird TRUE ausgegeben.

Die Standarddatentypen für diese polymorphe Funktion sind im Anschlussfeld dargestellt.

Ein-/Ausgänge

x

—

x

—

x muss ein boolescher Wert oder eine Zahl sein.x kann beispielsweise ein Skalarwert, ein Array oder Cluster aus Zahlen oder booleschen Werten, ein Array aus Clustern von booleschen Werten und so weiter sein. Wenn x ein Fehler-Cluster ist, wird nur der Status-Parameter des Fehler-Clusters an den Eingangsanschluss übergeben.  y

—

y

—

y muss ein boolescher Wert oder eine Zahl sein.y kann beispielsweise ein Skalarwert, ein Array oder Cluster aus Zahlen oder booleschen Werten oder ein Array aus Clustern von booleschen Werten sein. Wenn y ein Fehler-Cluster ist, wird nur der Status-Parameter des Fehler-Clusters an den Eingangsanschluss übergeben.  x XOR y?

—

x XOR y?

—

x XOR y? ist das logische Exklusiv-ODER von x und y. |

Wahrheitstabelle

| x | y | x XOR y? |

|---|---|---|

| T | T | F |

| T | F | T |

| F | T | T |

| F | F | F |

Details zum LabVIEW FPGA Module

Die folgenden Details gelten, wenn Sie dieses Objekt in einem FPGA-VI verwenden.

| SCTL (Single-Cycle Timed Loop) | Unterstützt. |

| Verwendung | Verwenden Sie für maximale Zeit- und Ressourceneffizienz boolesche Funktionen in einer SCTL. |

| Timing | In Single-Cycle Timed Loop--Wenn Sie boolesche Funktionen in einer Single-Cycle Timed Loop verwenden, trägt jede boolesche Operation geringfügig zur kombinatorischen Verzögerung der Single-Cycle Timed Loop bei. Außerhalb einer SCTL--Wenn Sie boolesche Funktionen außerhalb einer SCTL verwenden, erfordert jede boolesche Operation eine Taktperiode. |

| Ressourcen | Boolesche Funktionen verbrauchen nur dann erhebliche FPGA-Ressourcen, wenn Sie ein großes Array mit dem Eingang verbinden. Sie sollten Arrays begrenzen, um FPGA-Ressourcen zu schonen. |

Beispiele

Die folgenden Beispieldateien sind in LabVIEW enthalten.

- labview\examples\Booleans\Boolean Functions.vi