利用Xilinx内核生成器IP选板提高IP复用率

概览

要提高软件开发效率,有效的代码复用至关重要。在现场可编程门阵列(FPGA)硬件中,可重复使用的代码块通常被称为IP块。NI LabVIEW FPGA模块提供了多种方法来访问产品中的IP块。虽然LabVIEW FPGA模块为数学和信号处理提供了许多内置功能,但使用其他来源的现成IP库也很常见。 LabVIEW 2011 FPGA模块及更高版本包括一套由Xilinx创建并针对Xilinx FPGA硬件精心调试的高性能库。要提高您的FPGA项目生产力,请详细了解Xilinx内核生成器IP选板的功能以及使用方式。

内容

Xilinx内核生成器选板概览

基本功能

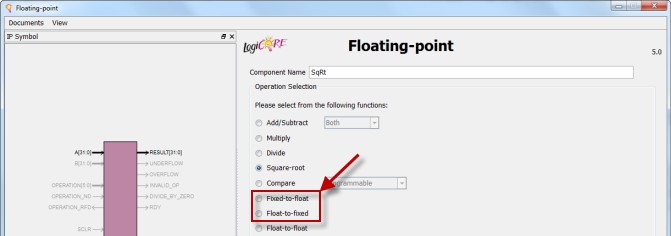

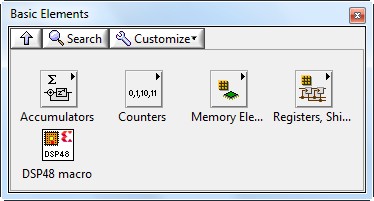

基础IP选板包括高度优化的累加器、计数器和存储器发生器函数。您还可以使用DSP48宏函数,通过配置向导生成自定义IP。宏向导通过指定指令、流水线配置和端口来指导您对DSP48进行自定义,这样一来,您无需手动配置这些复杂设置,即可利用DSP48的强大功能。

图1.使用DSP48宏函数,您可以快速配置和生成用于LabVIEW FPGA的自定义IP块。

| IP产品页面IP | |

图2.BaseIP LabVIEW FPGA选板 |

|

图3.基础元素(Basic Element)LabVIEW FPGA选板 |

数字信号处理(DSP)

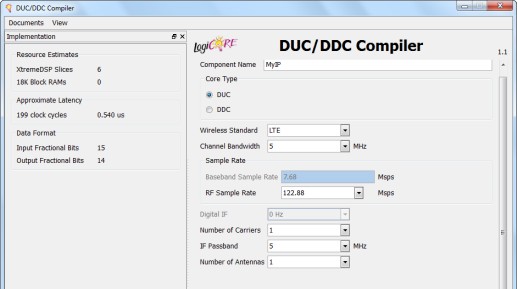

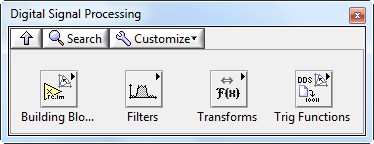

DSP内核生成器选板包括滤波器和变换库,可加快信号处理应用的开发。尽管基于配置,但内核生成器向导显示了各种各样的参数,其中包括资源使用估算和IP符号,可清楚地显示当前的端口利用率。通过这种高度参数化的方法,您可以在生成自定义IP时实现较大的灵活性和高效率。

图4.Xilinx内核生成器对话框显示了许多IP参数和规格,可帮助您根据特定的应用需求自定义内核。

图5.数字信号处理(Digital Signal Processing)选板 | IP产品页面 |

1您需要获得Xilinx许可证,才能使用该内核生成器IP内核。有关更多信息,请参阅IP产品页面。

数学函数

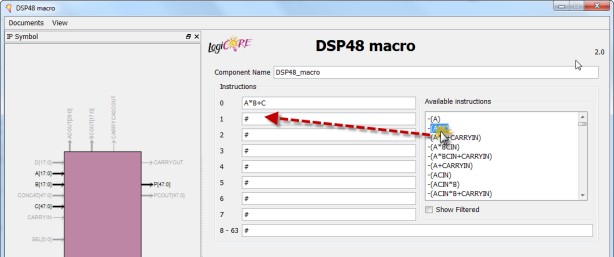

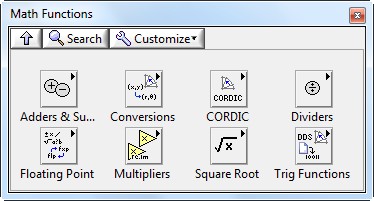

内核生成器选板提供从基本到高级的各种数学函数。例如,该选板包括一个用于生成IP的模块,可在FPGA上转换为浮点数并对其执行基本操作。如图6所示,您可以使用IP配置向导来轻松选择您想为之生成代码的浮点运算。

图6.Xilinx内核生成器浮点运算符IP内核为LabVIEW FPGA提供了浮点函数库。

图7.数学函数选板 | IP产品页面 |

|

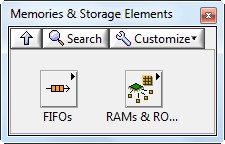

存储器和数据存储元素

图8.存储器和存储元素选板 | IP产品页面 |

高级行业特定选板

内核生成器IP选板包括两个通信和图像处理选板,可以重复使用,从而缩短FPGA设计时间。

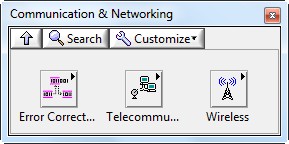

通信和网络

图9.通信和网络选板 | IP产品页面 |

错误修正IP 3GPP2 Turbo解码器1 Viterbi解码器1 LTE FFT 1 无线IP DPD1

|

1您需要获得Xilinx许可证,才能使用该内核生成器IP内核。有关更多信息,请参阅IP产品页面。

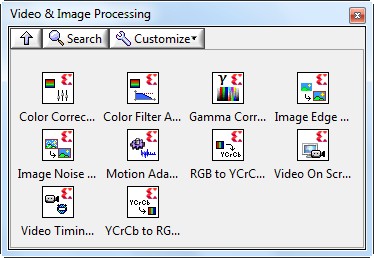

视觉和图像处理

| IP产品页面 |

|

Gamma校正1

|

1您需要获得Xilinx许可证,才能使用该内核生成器IP内核。有关更多信息,请参阅IP产品页面。

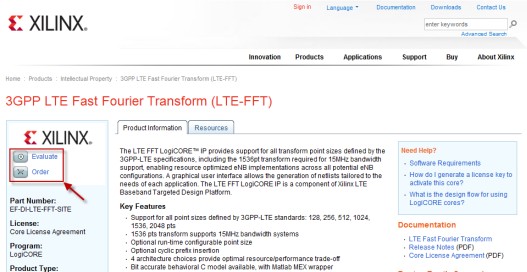

获取Xilinx内核生成器IP块许可

如前所述,有些Xilinx IP块需要许可证。要了解有关许可费用和流程的更多信息,请单击上面的IP块链接。

图11.Xilinx IP产品页面包括需要许可的内核生成器块的评估和订购信息。

使用内核生成器IP的开发注意事项

与LabVIEW FPGA中的其他高性能IP块类似,在应用中使用内核生成器库时,有一些开发注意事项需要谨记。内核生成器IP只能在单周期定时循环中执行。因为内核生成器IP通常包含内部流水线,类似于高性能数学函数,输出数据不是在每个时钟上验证的,您需要使用IP控制信号输出在数据得到验证时发出信号。

此外,Xilinx内核生成器库支持仅限于Xilinx Virtex-5和Spartan-6 FPGA,因此,请确保您使用的NI可重配置I/O硬件包括这些FPGA终端之一。

请查阅产品页面上的IP块数据表,了解更多详细注意事项。

将内核生成器IP块集成到LabVIEW

使用内核生成器选板上的浮点运算符IP内核来执行浮点平方根运算

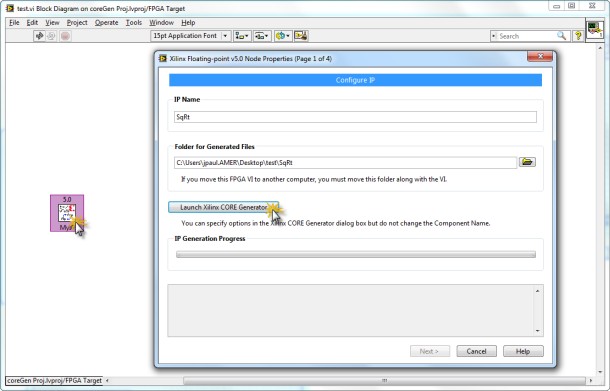

保存VI并双击IP块,打开“Xilinx浮点v5.0节点属性”(Xilinx Floating-point v5.0 Node Properties)窗口。要启动内核生成器IP配置向导,请单击“启动Xilinx内核生成器”(Launch Xilinx CORE Generator.)。

图12.启动Xilinx内核生成器。

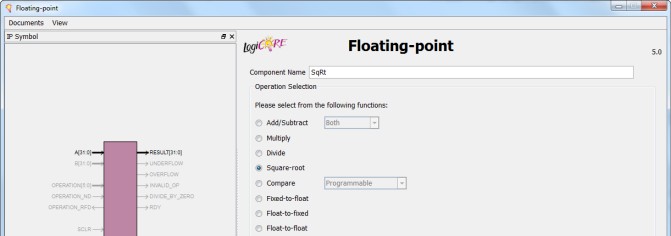

在对话窗口中,选择要执行的浮点函数(在本例中选择的是“平方根”(Square-root))。单击其余步骤,将其他向导设置保留默认状态,然后单击“生成”(Generate)按钮。IP内核的生成可能需要几分钟的时间才能完成。

图13.生成IP内核。

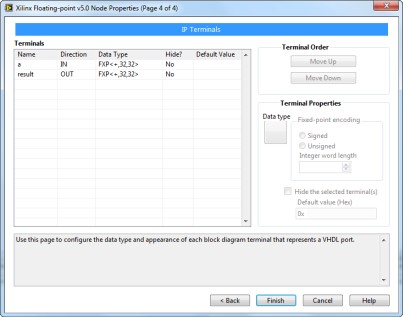

IP生成完成后,将“Xilinx浮点v5.0节点属性”(Xilinx Floating-point v5.0 Node Properties)窗口的后续两个属性保留为默认设置。您可以通过选择时钟信号和配置重置行为,来自定义IP块。单击“完成”(Finish),结束生成过程。

图14.完成生成过程。

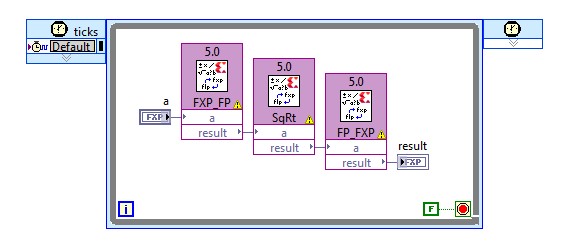

重复执行第二步至第五步,再生成两个IP块,一个用于定点转浮点数据类型,另一个用于浮点转定点数据类型。在浮点运算符内核生成器配置向导的第一步中选择该功能,如图15所示。

图15.浮点运算符内核生成器向导

图16.为IP块连线并将逻辑置于单周期定时循环内。

现在,您已经实现了浮点平方根运算,可以将其纳入新的或现有的LabVIEW FPGA应用中。

导入第三方IP的其他方法

如果您已经获得或创建了其他VHDL或Verilog IP,可以使用组件级IP(CLIP)节点或IP集成节点将其导入。

要了解更多信息,请参阅将外部IP导入LabVIEW FPGA。

适用于FPGA的先进、优化功能

您拥有的IP越多,就能越有效地完成LabVIEW FPGA应用。Xilinx内核生成器IP选板拥有50多个IP内核,为您提供了更多针对Xilinx FPGA进行了优化的高级功能。利用其中包含的基于配置的向导,您可以为特定应用轻松设置和自定义IP块。

图10.视频和图像处理(Video & Image Processing)选板

图10.视频和图像处理(Video & Image Processing)选板