为NI VeriStand创建基于FPGA的I/O特性

概览

内容

什么是基于FPGA的I/O接口?

现场可编程门阵列(FPGA)是一种可重复编程硅片,具有专用集成电路(ASIC)等硬件逻辑实现的卓越执行性能和可靠性,以及基于软件或固件实现的灵活性。利用可配置逻辑块和可编程连线资源,用户无需在物理层上更改设备,即可对FPGA进行配置,以实现自定义硬件功能。相反的,用户在软件中开发数字计算任务,并将其编译成比特流文件,其中包含FPGA逻辑和连线组件如何进行配置和连接等信息的。

为什么在实时测试应用中使用FPGA?

利用用户自定义的基于FPGA的I/O接口,可以创建自定义I/O设备,实现信号处理、仿真、触发和控制等任务,为用户提供I/O接口,很好地满足应用需要。此外,由于I/O接口基于FPGA,用户还可以轻松地重新配置接口特性,以满足新的要求,或者在不更改硬件设置的情况下创建能够用于多项应用的测试系统。

自定义I/O是在实时测试应用中使用FPGA的最主要原因之一。超过100款的C系列信号调理模块为用户应用提供专用接口。将信号调理模块的多样性与基于FPGA的I/O设备的灵活性相结合,用户可以快速创建具有自定义定时和触发功能的I/O接口,从而完全满足用户的实时测试要求。

另外,用户还可以使用FPGA完成数据预处理和后处理,从而减少执行实时测试应用程序的微处理器的负担。例如,FPGA可以采集来自编码器的数字信号,并根据此信号计算出速度和加速度,然后将这些信息传输给实时测试应用程序。

另外,在实时测试应用中使用FPGA还可以帮助你增加高速闭环控制功能。例如,用户可以在FPGA上运行一个运动控制器,同时由实时应用程序为控制器提供设定值。这样,闭环控制的响应速度能够大大提高,实现更加精确的系统控制。无刷直流电机的控制是此方法的一个应用实例。

此外,用户还可以在HIL测试系统的实现中用FPGA来仿真各种传感器。FPGA能够适应多种类型传感器的精确定时要求,因而是传感器仿真的理想选择。用户能够实现纳秒级分辨率的传感器仿真,更加真实地仿真传感器响应信号。在许多情况下,传感器以不同的响应速率独立运行。FPGA的物理并行性使其成为实现真实组件行为仿真的理想选择。用户可通过NI VeriStand附加软件社区下载FPGA XML生成器节点。

自定义FPGA特性与NI VeriStand的协作方式

在典型应用中,开发人员负责完成自定义FPGA逻辑的编程、FPGA逻辑与实时处理器上执行的应用程序之间的通信机制,以及实时应用程序中的数据预处理和后处理。NI VeriStand提供的框架实现了后面两个部分,即通信机制和数据处理,从而减少了实时测试应用程序使用FPGA所需的开发工作量。要在NI VeriStand上应用FPGA特性,用户只需开发FPGA特性,然后使用XML文件描述用户的FPGA特性与NI VeriStand实时测试应用程序之间的接口,从而减少了开发工作量。

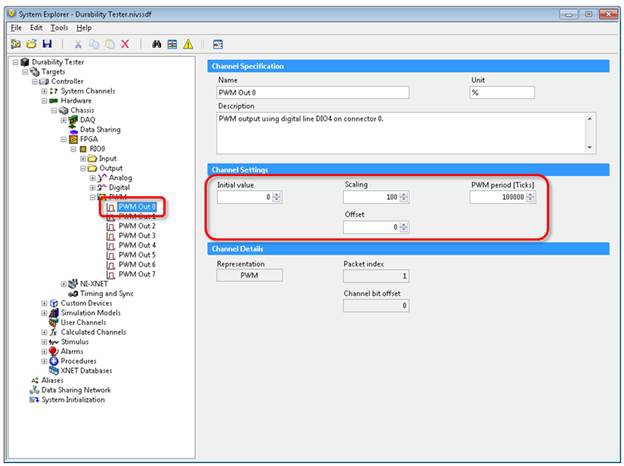

用户从NI LabVIEW软件中的模板项目开始着手创建NI VeriStand FPGA特性,此模板包含了与用户NI VeriStand应用程序接口所需要的代码。用户可以使用LabVIEW来定义此框架中的自定义FPGA功能,编译FPGA特性,为FPGA特性编辑XML文件。完成以上步骤以后,用户只需要选择XML文件即可将此特性添加到NI VeriStand系统定义中。XML文件告诉NI VeriStand如何与用户特性接口,以及自动提供它的输入、输出和在NI VeriStand系统浏览器中的参数,从而用户可以设置数值以及与其它实时任务的连接,就像对其他任何硬件接口进行操作一样。例如,如果用户定义了一个带PWM输出的FPGA特性,那么可以使用NI VeriStand系统浏览器来设置通道参数,例如周期和初始值等,并将占空比输入映射到用户实时测试应用程序中的另一个通道中,如图1所示。

图1: 在系统浏览器中配置NI VeriStand FPGA特性

用户在部署NI VeriStand实时应用程序时,NI VeriStand将用户编译的FPGA特性自动下载至硬件接口。

NI VeriStand FPGA特性架构

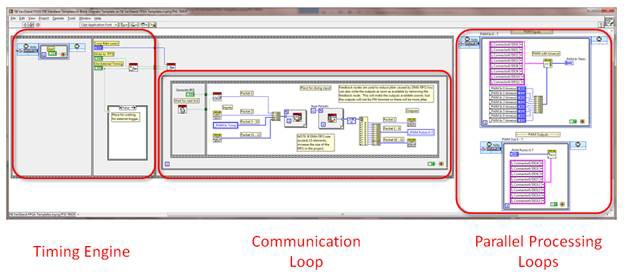

用户可以使用LabVIEW FPGA模块,修改其中的特性模板来创建NI VeriStand FPGA特性。此模板包含了与用户的NI VeriStand应用程序接口所需要的代码。NI VeriStand中的FPGA特性由定时引擎、通信循环和并行处理循环组成。

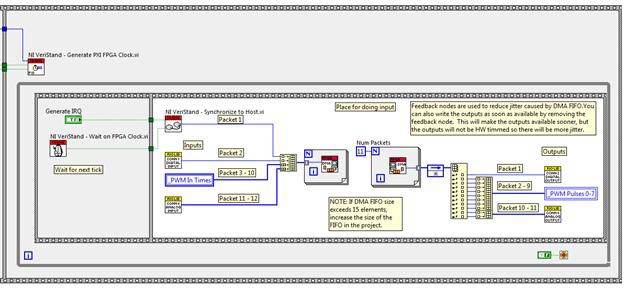

图2: NI VeriStand FPGA 特性模板

定时引擎

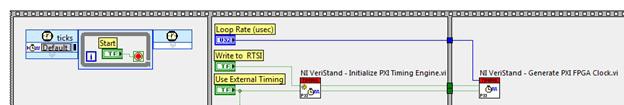

定时引擎通过NI VeriStand系统浏览器进行配置,使FPGA与NI VeriStand实时应用程序以及系统中的其它硬件I/O设备实现同步。在用户的NI VeriStand实时应用程序部署完成之后,加载用户的FPGA特性,同时定时引擎等待来自NI VeriStand的启动条件。

图3: 初始化定时引擎

在用户的实时应用程序确认启动触发之前,NI VeriStand设置循环速率(µs)、写入RTSI和使用外部定时参数。这三个参数完成定时引擎的同步模式(主、从或不同步)配置,并设置用户特性与NI VeriStand实时应用程序之间的通讯速率。

NI VeriStand – 生成PXI FPGA时钟子VI以生成时钟,此时钟用来为下文讨论的通信循环以及同步处理定时。在主模式下,FPGA利用在其上运行的循环计时器对通信循环进行计时,并将时钟导入到实时系统集成(RTSI)总线上,以便同步其它硬件设备。在从模式下,FPGA监控RTSI总线,并用RTSI0上获取的时钟对通信循环进行定时。在非同步模式下,FPGA用自带的循环计时器对通信循环进行计时,并且不向RTSI总线导出任何信号。

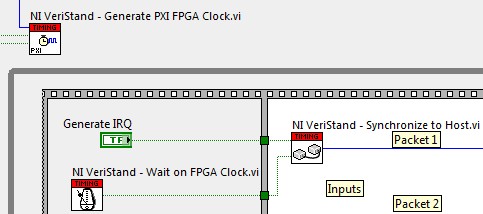

除了实现硬件同步,定时引擎还能实现与NI VeriStand实时应用程序的同步。图4所示为通信循环的一部分。

图4: NI VeriStand与FPGA同步

NI VeriStand – 等待FPGA时钟子VI用作通信循环的循环计时器,等待来自NI VeriStand – 生成PXI FPGA时钟子VI的时钟信号。另外,在主机模式下,NI VeriStand在确认启动控制之前,先确认产生IRQ。在确认产生IRQ之后,NI VeriStand – 与主机同步子VI在通信循环的每个迭代中确认一个中断。如果FPGA被设置为主机,NI VeriStand实时应用程序的执行将通过此IRQ信号由FPGA进行定时。

通信循环

通信循环负责发送和接收NI VeriStand实时应用程序的数据。由于NI VeriStand按照硬件计时单点方式更新通道,FPGA必须按照NI VeriStand引擎中的主控制循环所规定的速率运行通信循环。欲了解NI VeriStand引擎的更多信息,请参考NI VeriStand帮助。

通信循环的定时由NI VeriStand – 等待FPGA时钟子VI来实现,此子VI作为循环计时器,等待前述的NI VeriStand – 生成PXI FPGA时钟子VI来生成时钟。

图5: 数据通信循环

如图5所示,采取64位数据包格式的数据,通过DMA先入先出内存缓冲(FIFO),发送至NI VeriStand实时应用程序,另外,通过DMA FIFO来接收来自NI VeriStand实时应用程序的、采取64位数据包格式的数据。

发送至NI VeriStand的第一个数据包包含了来自NI VeriStand – 与主机同步子VI的信息,该信息解释了FPGA循环是否在此之后运行。发送至主机的其他数据包中包含了由FPGA执行的测量或计算数据。数据包通过写入到For循环中的NI VeriStand – 发送数据包至主机子VI进行发送,此VI负责写入到DMA_READ FIFO。DMA_READ FIFO在项目浏览器中进行定义,并且必须指定其深度,使其中的元素数目至少等于每次迭代传输的数据包大小。

数据通过DMA_WRITE FIFO发送至FPGA,DMA_WRITE FIFO也在项目浏览器中进行定义。另外,必须规定其深度,使其中的元素数目至少等于每次迭代传输的数据包大小。通过For循环中的NI VeriStand – 接收主机数据包子VI读取FPGA上的DMA_WRITE FIFO。配置For循环时,必须使其迭代次数与While循环的每次迭代所需读取的数据包数目相同。然后,分割数据包,并发送至用户FPGA的适当部分。在图5中,黄色标题的子VI代表I/O资源。此循环中采集或生成的所有I/O均与NI VeriStand以及系统中的其它硬件设备同步。

并行处理循环

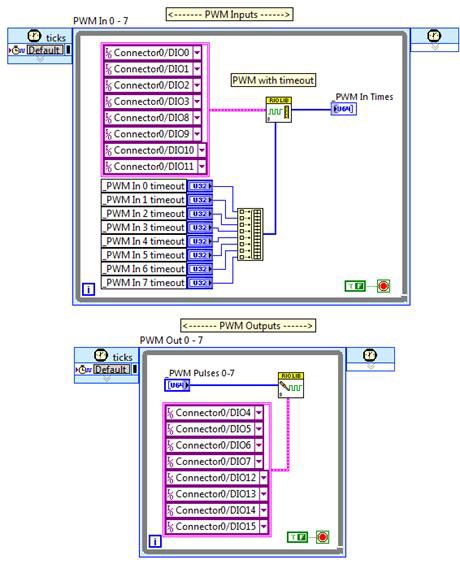

并行处理循环是NI VeriStand构架中的自定义FPGA特性的最后一部分。这些循环之所以称为并行,是因为它们所采用的时钟不是NI VeriStand通信循环以及系统中其它硬件的定时时钟。这些循环可以简单地从自定义定时I/O上采集或生成数据,或者负责完成自定义测量和生成,例如PWM I/O。另外,它们也可以用来协助处理从NI VeriStand发送至FPGA的数据。图6所示的模板实例包含了PWM输入和输出。

图6: 并行PWM循环

如图5和6所示,并行处理循环通过局部变量完成通信循环的数据发送/接收。通信循环只按照自己的运行速率更新这些本地变量,并且只将本地变量的当前值(无缓冲)发送至NI VeriStand主机。并行循环的数据被通信循环抽选,但是并行循环的定时并不受通信循环的影响。

后续步骤

对于实时测试应用,基于FPGA的I/O接口具有许多优势。利用这些接口,用户能够创建自定义I/O设备,实现信号处理、仿真、触发和控制等任务的合并,另外这些I/O设备可以方便地重新进行配置,以满足新的要求,或者创建能够用于多种应用程序的测试系统,而无需更改硬件设置。NI VeriStand提供了一个实现通信机制和数据处理的框架,从而降低了在实时测试应用中使用FPGA所需要的开发工作量,使用户能够集中于FPGA功能的开发。然后,用户可以像处理其它硬件I/O接口一样,将FPGA特性无缝地插入到NI VeriStand中,并使用基于配置的环境完成其余的实时测试应用。