了解直接數位合成 (DDS)

綜覽

了解直接數位合成的基本原理與理論,以及如何將其應用於函式產生器與任意函式產生器。

內容

介紹

《產生訊號》技術文章探討函式產生器和任意函式產生器 (AFG) 等訊號產生器如何輸出所需的類比訊號,以及某些訊號產生器如何使用直接數位合成 (DDS) 技術輸出頻率精確的訊號。這篇文章討論讓訊號源在訊號產生過程中能夠達到次赫茲精確度的元件與技術。

運作原理

使用 DDS 的訊號產生器透過一種獨特的記憶體存取與時脈機制,按精確的頻率產生訊號,有別於按波形儲存順序逐一輸出樣本的傳統方式。任意波形產生器 (AWG) 使用傳統的訊號產生方式。AWG 能產生複雜的使用者定義波形,但受限於產生波形時的頻率精確度。這是因為 AWG 記憶體必須逐點產生波形,而且控制各產生點間隔時間的取樣時脈頻率數有限,因此有其侷限。

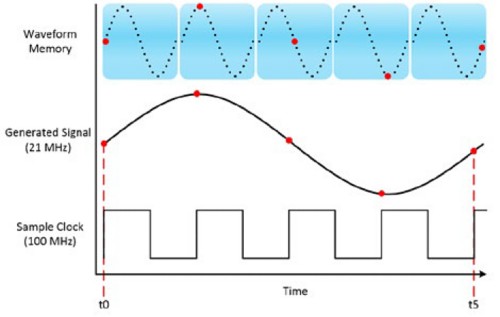

使用 DDS 的函式產生器與 AFG,會將週期波形一次週期所產生的大量點儲存在記憶體中。DDS 技術讓函式產生器或 AFG 能夠選擇從記憶體輸出的樣本。由於函式產生器或 AFG 選擇波形中的下一個樣本時不受限制,因此能產生頻率精準的訊號。圖 1 藉由圖形說明函式產生器或 AFG 產生 21 MHz 正弦波的方式,這個波形並非 100 MHz 取樣時脈的整數分頻。DAC 輸出更新率仍取決於 100 MHz 取樣時脈;因此,取樣時脈越快,就能建立形狀越準確的訊號。

圖 1:支援 DDS 功能的硬體未必會按照樣本儲存在記憶體中的順序選擇樣本。因此,100 MHz 取樣時脈能夠準確建立 21 MHz 正弦波

以上述範例來看,AFG 會使用 100 MHz 取樣時脈驅動 DAC,但產生訊號時,則是以從波形記憶體位置選擇樣本的方式建立頻率。以下各節討論選擇樣本時執行控制邏輯的各個元件。

功能概述

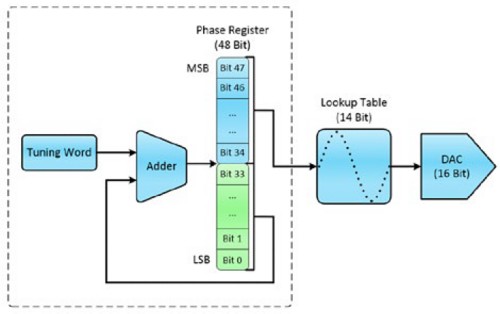

DDS 的執行結構必須包含三大硬體建構模組:(a) 樣本時脈、(b) 相位累加器,以及 (c) 檢索表,也就是執行可程式化的唯讀記憶體。圖 2 說明硬體模組到硬體模組之間的概要流程。

圖 2:DDS 架構的硬體方塊圖

a.取樣時脈

取樣或參考時脈用於建立頻率調整字、更新相位累加器數值,以及驅動數位轉類比。取樣時脈決定 DAC 何時輸出樣本,但並不會直接決定輸出訊號的頻率。

b.相位累加器

相位累加器是一組元件,能讓函式產生器或 AFG 按精準的頻率輸出。為建立頻率精準的訊號,相位累加器會使用三個通用元件。首先,相位累加器會使用調整字彙指定訊號頻率。調整字是 24 到 48 位元的數位訊號字,用於指定在波形記憶體中跳轉的樣本數。第二個元件是加法器,它會擷取調整字,再將調整字與相位暫存器餘數相加。接下來會將這個新的數位訊號值輸出到相位暫存器。相位暫存器是相位累加器的最後一個元件,會擷取新的數位訊號字,用於在檢索表中指定下一個待輸出取樣點的記憶體位址。相位暫存器會擷取檢索表記憶體位址中未使用的其餘最高位元,再將這些位元傳回加法器,確保頻率能長時間保持精確。

c. 檢索表

記憶體位址會隨著時間增加,改變的速度由調整字指定,因此相位暫存器的輸出看起來就像是個數位斜坡。因此,為輸出所需的波形,相位暫存器的輸出在檢索表中會指向所需的波形樣本位址。之後,檢索表會在所提供的記憶體位址提供數位訊號字,也就是 DAC 應產生之正確振幅和相位的數位訊號字。

DDS 架構的主要優點之一,就是頻率敏捷度高,也就是能迅速改變波形頻率,且相位會連續。使用 DDS 的 AFG 能迅速改變波形頻率,因為只要改變調整字就能改變波形的頻率。

常見用途

如前所述,DDS 技術有兩項主要優點。DDS 技術的主要優點之一,就是能產生頻率準確的訊號。由於具備這樣的功能,因此能夠進行準確度極高的元件測試,因為您可以相信函式產生器或 AFG 建立之訊號的頻率準確度。

DDS 技術的第二項主要優點是能夠極其迅速地改變產生訊號的頻率,且相位能夠連續。由於具備這項優點,您就可以快速執行頻率變更,在特定範圍內進行更有效率的元件測試,也能針對測試元件提供給受測裝置設限,進行壓力測試。

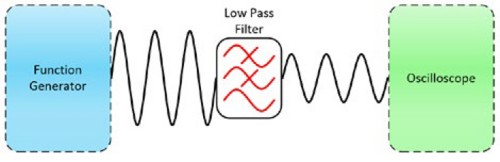

採用 DDS 技術的 AFG 相當重要,能準確分析濾波器的特性就是一個具體的例子。濾波器特性分析要準確,就必須符合兩項條件,其一是提供給濾波器的訊號必須是由 AFG 精確產生,第二則是必須以示波器準確量測過濾後的訊號。圖 3 是典型的濾波器特性分析測試。

圖 3:濾波器特性測試應用方塊圖,含支援 DDS 技術的函式產生器、低通濾波器以及示波器

摘要

- 不採用 DDS 技術的訊號產生器若要產生波形,會以取樣時脈的頻率逐點輸出預存的波形。

- 採用 DDS 技術的訊號產生器能產生多個頻率的週期波形,且頻率準確度極高。原因在於獨一無二的記憶體存取與時脈機制。

- 執行 DDS 技術要有三種高階硬體模組:取樣時脈、相位累加器與檢索表。

- 取樣時脈會建立頻率調整字、更新相位累加器值,以及驅動 DAC 輸出速率。

- 相位累加器會取頻率調整字用於輸入,並提供檢索表中下一個待輸出樣本的數位記憶體位址。

- 檢索表會將週期波形儲存成數位樣本。檢索表會從相位累加器取得記憶體位址,並將該記憶體位址的數位波形樣本提供給 DAC。

- 採用 DDS 技術的訊號產生器應當用於必須產生精準頻率或要求頻率敏捷度的用途。

- 若應用需要極大、極複雜的使用者定義波形,最好改用任意波形產生器,而不選擇採用 DDS 技術的任意函式產生器。