高速序列說明

綜覽

高速序列是一項越來越流行的技術,可減少裝置的體積並提升資料通訊速率。此篇技術文件探討高速序列通訊連結的基本概念。

內容

高速序列的需求

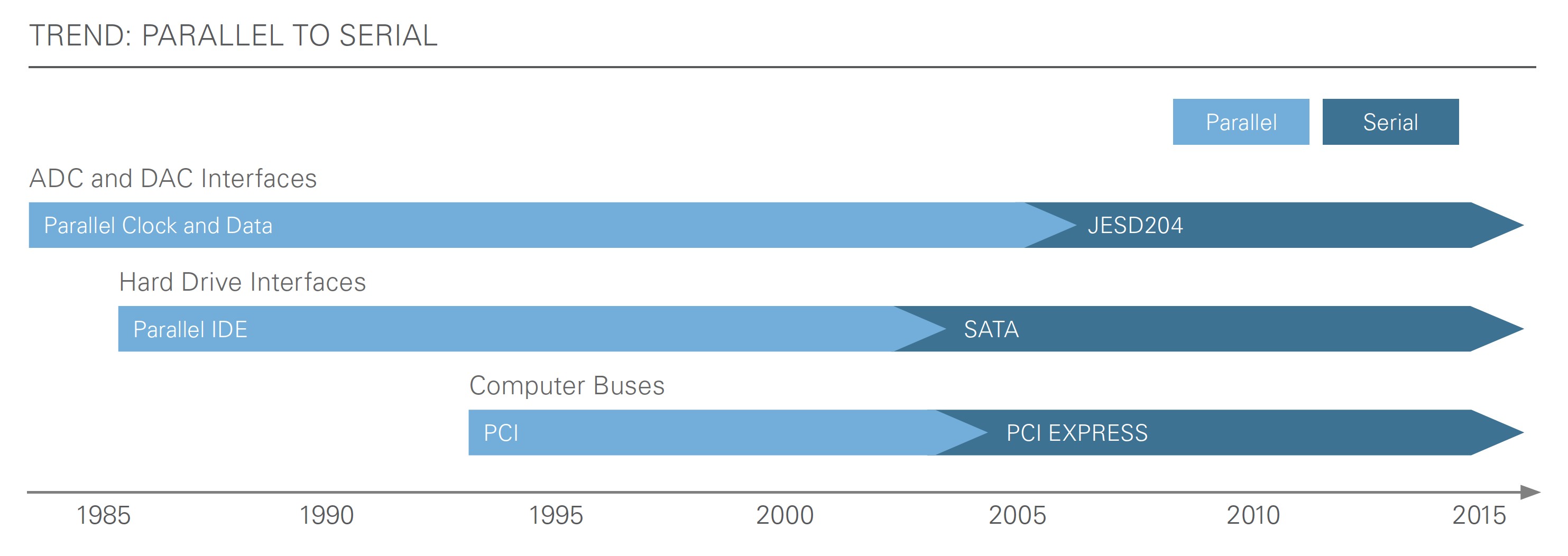

消費者對以更小體積、更低耗電達到更高效能的需求持續不斷成長。在 2000 年代初期,這些需求在大數據時代中,引發一道從平行到高速序列數位通訊匯流排的巨大轉變。如此轉而對裝置產生體積要更小、資料傳輸率要更高,且耗電要更低的需求。這些特性讓消費者在今天得以運用多項技術,例如 SATA、USB 與 PCI Express。

圖 1:2000 年代初期,市場開始從常見的平行通訊標準轉移到序列標準。

優點

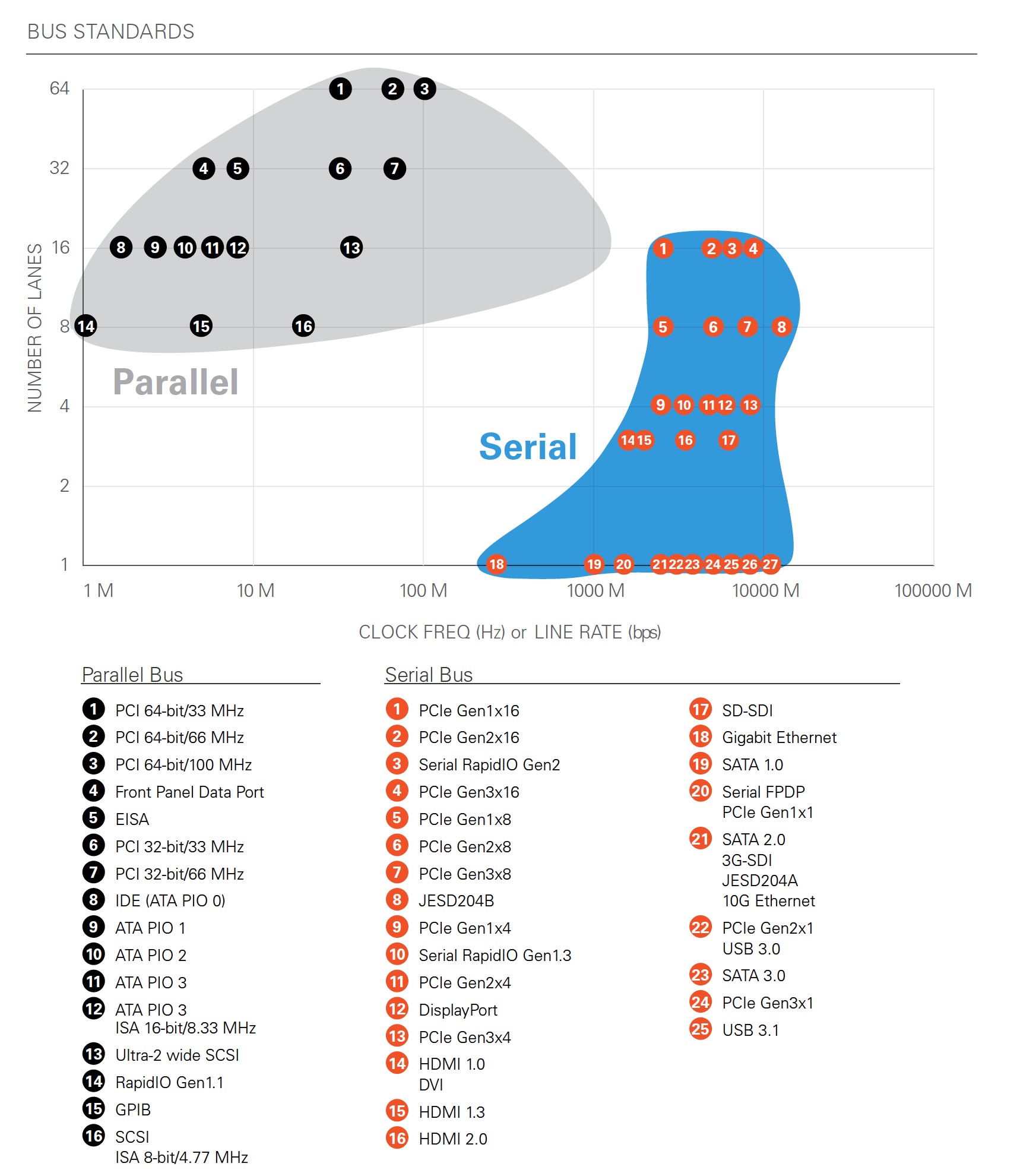

平行匯流排時脈率的物理限制大約是 1 GHz 至 2 GHz,因為個別時脈與資料通道所引入的歪曲,較快的速率會造成位元錯誤。高速序列匯流排所發送的編碼資料,在單一差動訊號中包含資料與時脈資訊,因此工程師可避免平行匯流排的速度限制。今日,以 10 Gbps 高速序列連結的資料通道已很常見。此外,多條序列連結通道可協調地結合在一起,形成具有較高資料傳輸率的通訊連結。

只要將資料序列化並以更快的速度傳送,就可減少積體電路 (IC) 中的針腳數,進而有助於縮小裝置尺寸。此外,因為序列通道能以更快的時脈速度操作,所以相較於平行匯流排,可以獲得更高的資料傳輸率。

圖 2: 下圖為常見的匯流排標準,以及對應的通道數與通道速率。序列標準可執行比平行標準更高的通道傳輸率,因此使傳輸率更高。

缺點

雖然減少針腳數可降低設計的複雜度,但所需的速度要更快,因此會面臨額外的設計挑戰。隨著設計達到 RF 頻率,必須做出與 RF 應用類似的類比考量,才能確保訊號完整度。為緩解這些訊號完整性問題,可使用高速序列連結來執行編碼、預加強與等化等技術。

高速序列連結層級

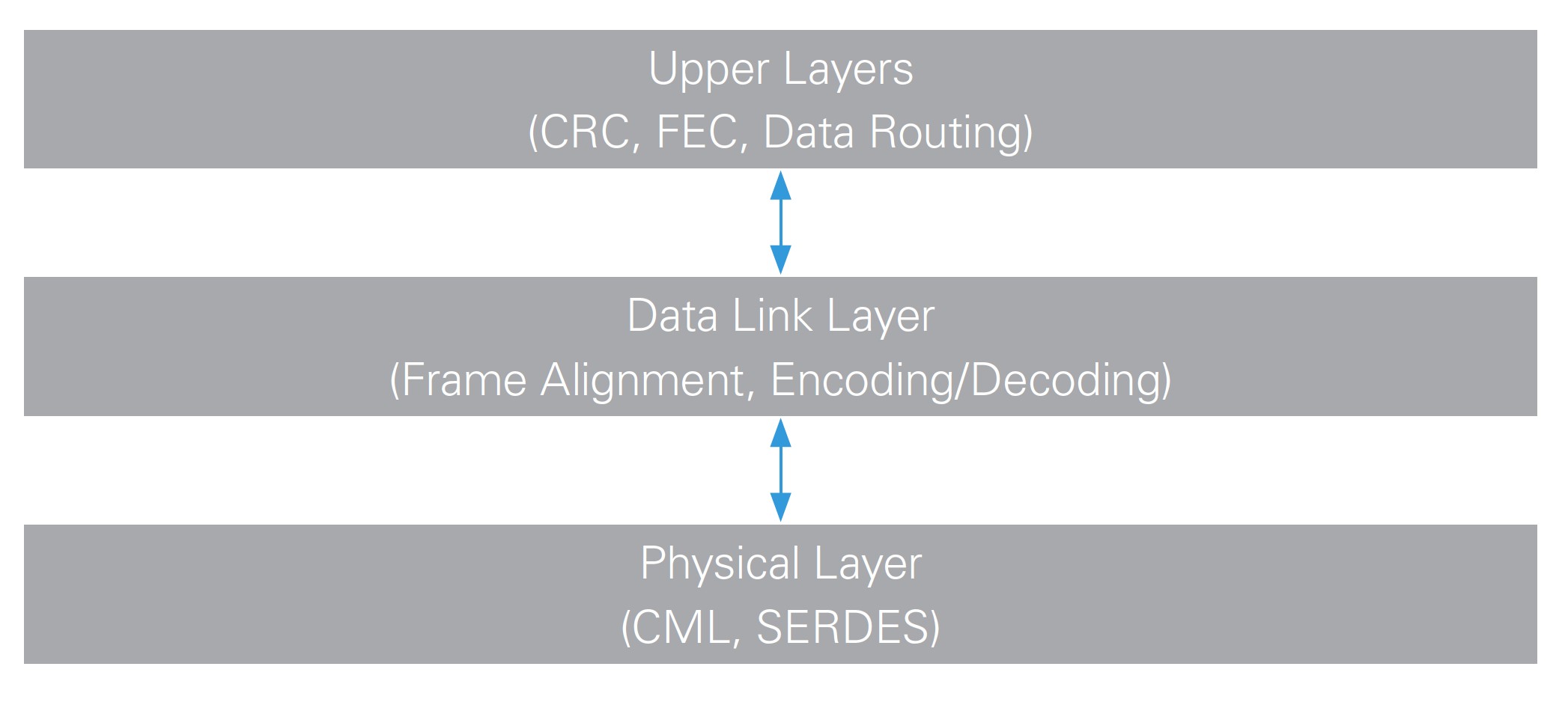

若要讓序列連結產生作用,各端點必須對特定參數操作作業保持一致。可將這些參數涵蓋到多道功能層。

圖 3: 可在實體與資料連結層之上增加層數。這些層級會因通訊協定與應用而有所不同,且往往是最需要客製化的共同層級。

實體層

實體層可確保裝置之間的電子相容性,並將時脈位元同步提供至資料連結層。

電子介面

不同的高速序列協定對傳輸器與接收器的電子介面,定義不同的需求。如此可確保傳輸器裝置連接至接收器時的電子相容性。高速序列連結的電子訊號難以達到,以超過 1 Gbps 速度進行通訊所需的極快上升時間和下降時間,進而儘量減少電磁輻射,並透過抑制共模雜訊來提高雜訊抗擾性。此外,在這樣的速度下,峰值對峰值電壓很少超過 1 V,而且電子標準通常是:低電壓差動訊號傳輸 (LVDS)、射極偶合邏輯 (ECL) 或電流模式邏輯 (CML)。

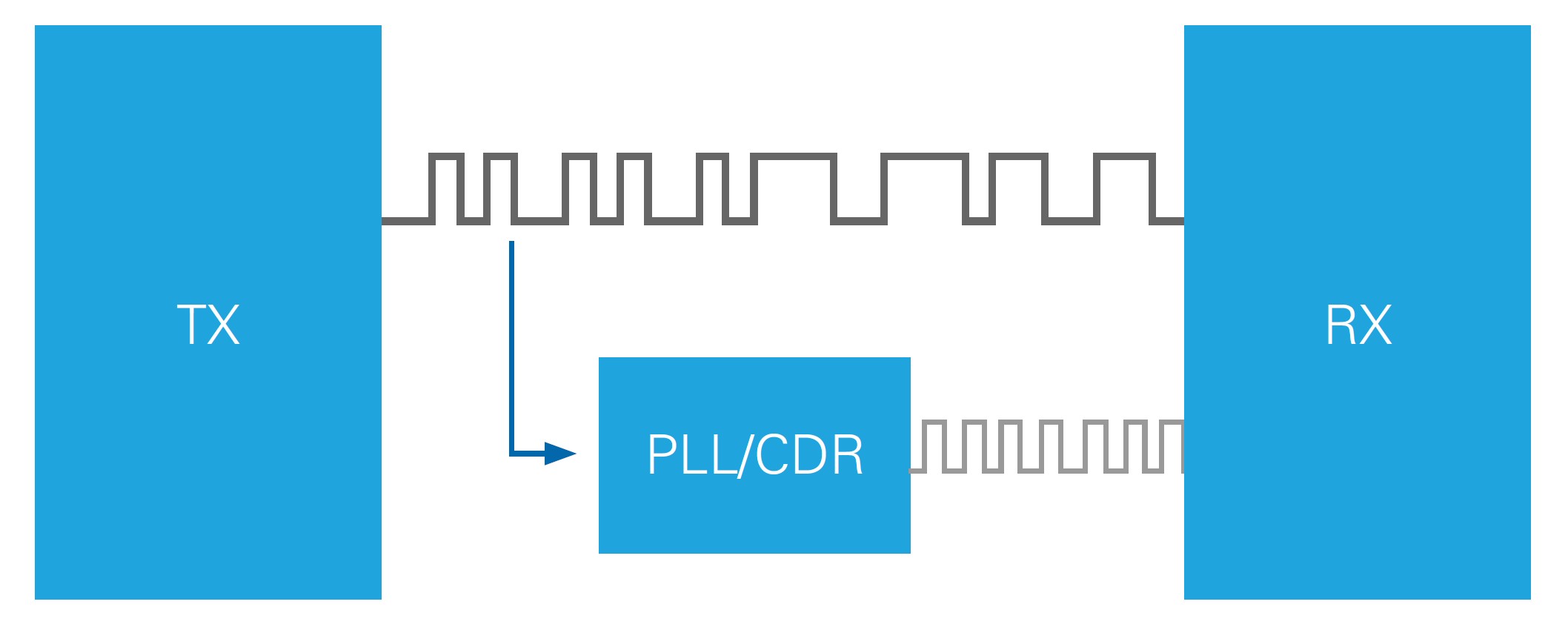

時脈與資料還原

適用於高速序列連結的實體層還有另一項重要特色,即為時脈與資料還原 (CDR)。CDR 是指接收裝置在不需要實際時脈訊號的情況下,即可為傳入的資料串流提供時脈功能。資料連結層可確保編碼時位元頻繁移轉,以助達到此目的。如此可讓相位鎖定迴圈 (PLL) 與相位插補器 (PI) 電路重新建立傳輸時脈,並使用此時脈以最小的時序錯誤來擷取傳入的資料串流。

圖 4: 由於在資料連結層編碼可確保在 0 與 1 之間頻繁移轉,CDR 電路可使相位鎖定迴圈至輸入的位元串流,並同步取樣已編碼的資料位元。

訊號完整性考量

如要以 5 GHz 或以上的速度傳輸位元資料,就會對類比設計構成挑戰。由於傳輸速度目前已達到 RF 設計的常見頻率範圍,因此便出現訊號完整性問題。必須使用高品質的 PCB、接頭,與連接線,才能以高資料傳輸率成功進行通訊。此外,PCB 設計師在設計高速序列連結時,必須了解傳輸通道理論。設計師需避免短截線、阻抗失配,與軌跡長度失配的情況,並使用合適的技術,以儘量減少訊號失真。

等化

等化是抵消通道的電子行為,以增加其頻率響應的過程。這可能會發生在通訊連結的傳輸器或接收器端,以改善連結邊限。但提到接收器時,通常會使用等化一詞。當高速序列訊號穿梭在 PCB 軌跡、接頭與連接線之間,並進入接收器時,衰減不會對訊號中的所有頻率元件產生相同的影響,反而會造成訊號失真。多 Gigabit 收發器 (MGT) 的等化設定,可在取樣前將增益或衰減套用至訊號的不同頻率,進而提升訊號與連結邊限。很多 MGT 都具備自動等化功能,可自動偵測並持續更新等化器,使其達到理想設定。

預加強

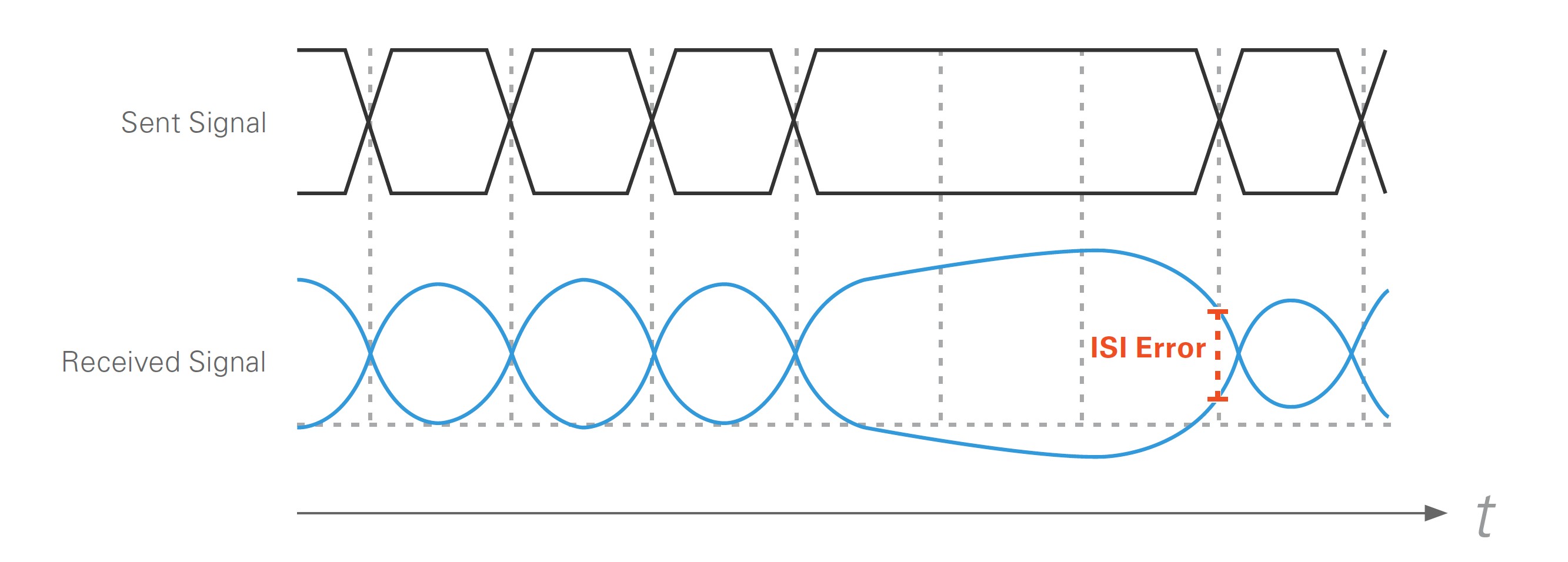

預加強通常是指高速序列連結傳輸器端的等化作業。其主要是用來克服符際干擾 (ISI) 所帶來的類比挑戰。在快速通道速率下,資料位元從傳輸時就開始互相影響。舉例來說,如連續傳輸 3 個 1,再跟隨一個單一的 0,則因資料通道已建置正偏壓,而難以快速驅低 0。

圖 5: ISI 造成的訊號降級是由於缺少位元移轉,導致通道產生偏壓,而難以迅速產生首次轉換到相反位元的移轉。

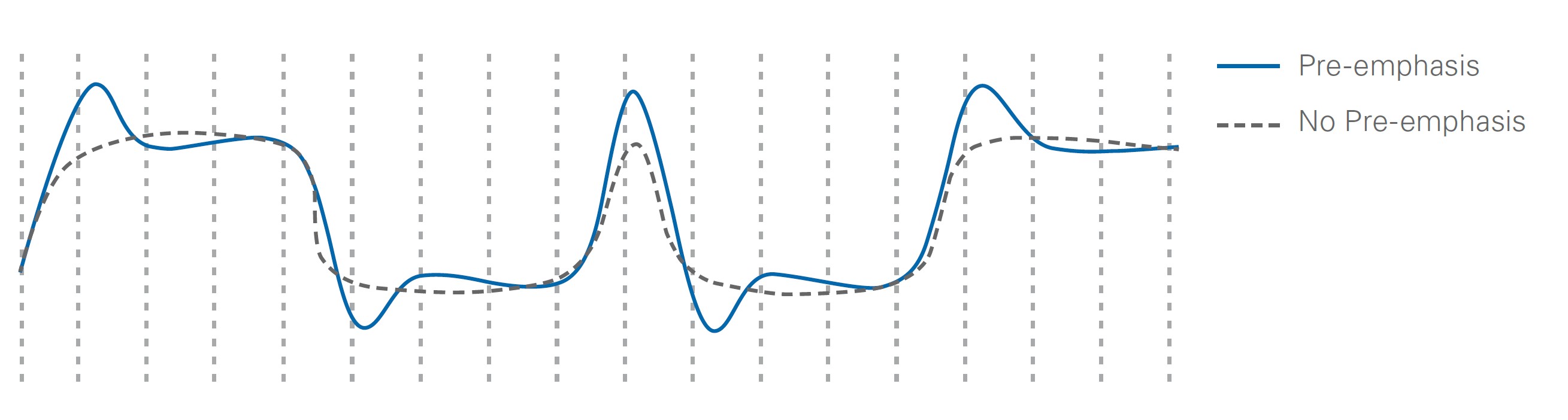

有 2 種方式可克服 ISI。如已知在從低到高或從高到低的移轉後,只有首位元有問題,則僅放大移轉後的首位元即可。如此會產生圖 6 所示的訊號。

圖 6: 預加強的目的在於放大訊號移轉後的第一位元。此有助於緩解 ISI 這樣的問題。

若要達到類似的波形,更常見的做法是在首次移轉後衰減位元,而不是放大首位元。高通濾波可完成此作業,因為移轉位元 (較高頻率) 的衰退比非移轉位元較少。

資料連結層

資料連結層負責處理資料,以提升訊號完整度、確保通訊成功,並將實體位元對應至資料。可用於此的功能包括:對齊、時脈修正和通道彙整的編碼方案及控制字元。

編碼方案

編碼的目的是透過頻繁的字元移轉,以確保 CDR 順利進行,以及資料達到 DC 平衡。若要 CDR 成功,則編碼方案必須確保資料訊號移轉充足,以便 CDR 電路至資料串流能夠保持相位鎖定。如 CDR 電路內部的 PLL 因缺乏移轉而無法保持鎖定狀態,則接收器將無法確保資料位元時脈同步化,進而發生位元錯誤或連結故障。實現 CDR 的做法是確保傳輸有頻繁位元移轉的符碼,此會導致將額外字元加入資料中。

DC 平衡對於維持序列連結的正常運作也很重要。若不調整 DC 的平衡量,則訊號可能會偏離其理想的高低階邏輯,進而發生位元錯誤。若要確保 DC 的平衡,可藉由平衡傳輸符碼中的 1 與 0 統計量。在 DC 平衡訊號中,隨時間傳輸的 0 與 1 數量,對統計來說隨時間而過都是相同的。

8b/10b 編碼

8b/10b 是一種常見的編碼方案。每 8 位元的資料,就會另增 2 位元的額外編碼。這 2 個額外的位元可提供的位元呈現 (符碼) 是 8 位元資料的四倍。8b/10b 編碼器會選取具有最多移轉與最佳 DC 平衡的預定義符碼,並對應到特定的資料字詞與控制符碼,以縮減數量眾多的符碼選項。此編碼器將這些符碼儲存到查找表中,並用來編碼和解碼資料。

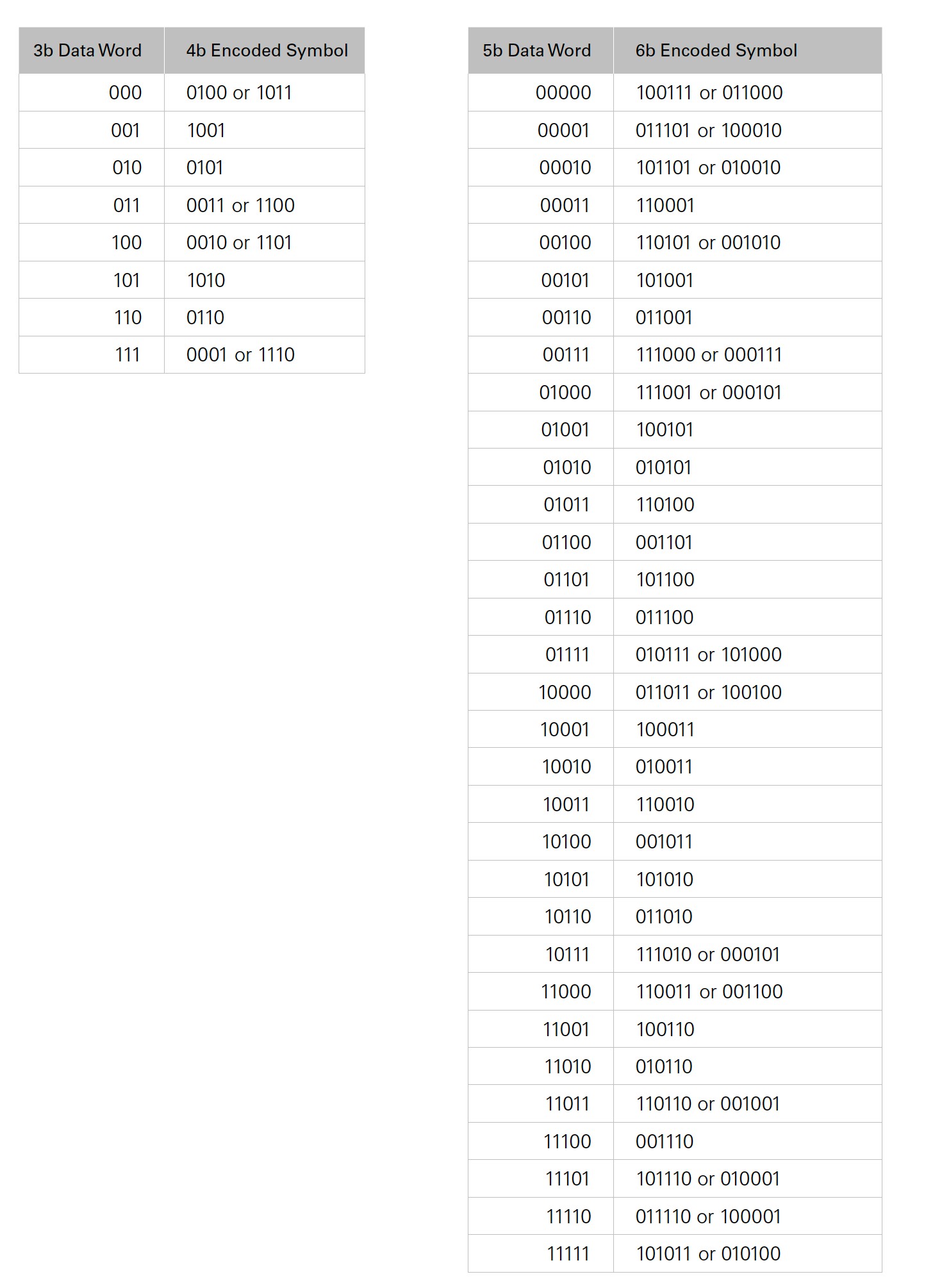

當 8 位元的資料字詞開始編碼時,編碼器會將資料字詞分為 5 位元與 3 位元,並對資料字詞分別執行 5b/6b 與 3b/4b 編碼。編碼器將最後 5 個位元傳送至 5b/6b 表,並將 3 個最高有效位元傳送至 3b/4b 表。

表 1: 編碼器將 3 個最高有效位元傳送至 3b/4b 表,並將 5 個最低有效位元傳送至 5b/6b 表,以位 8b 的資料字詞編碼。接著編碼器會根據運行落差來結合兩者,以形成一個 10b 的符碼,並針對 CDR 電路進行頻繁移轉。

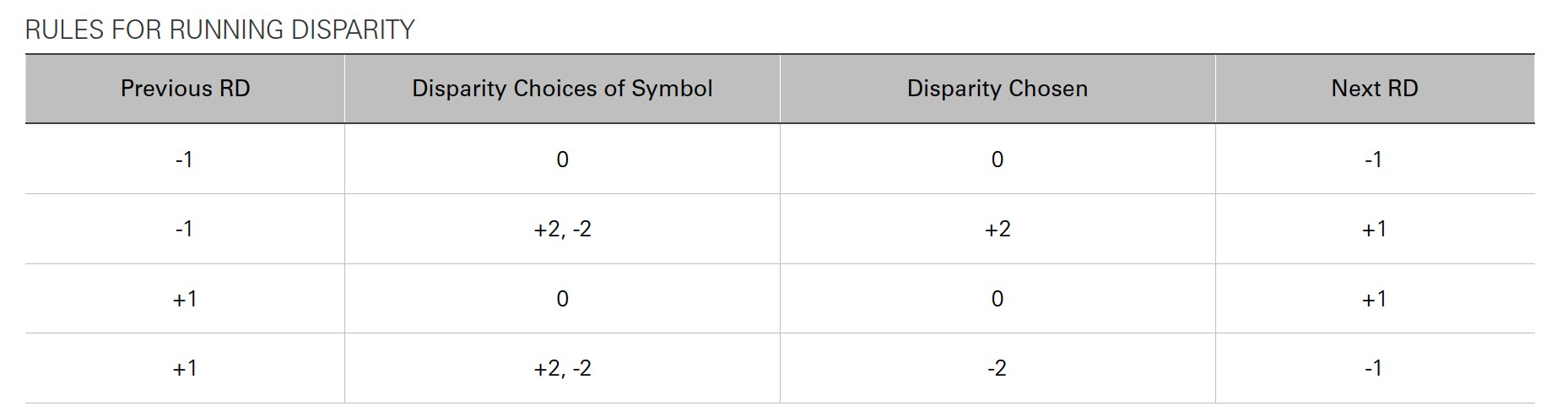

在理想情況下,所有符碼都具有相同的 0 與 1 數,以維持 DC 平衡。但 5b/6b 與 3b/4b 表的符碼則非如此,因此必須執行規則,並根據「運行落差」概念來決定。 此為根據已傳輸的 1 與 0 數,在兩者間的累加差異。由於沒有足夠的符碼可擁有相同數量的 1 和 0 來呈現八位元,因此某些資料字詞會用兩個符碼來表示:一個符碼的 0 多於 1,另一個符碼的 1 則多於 0。舉例來說,3b/4b 表中 1101 的符碼也可呈現為 0010。在選擇要使用的符碼版本時,編碼器總會嘗試平衡運行落差。完整的 8b/10b 符碼落差始終是 0、+2 或 -2。表 2 顯示編碼器用來決定應使用哪個符碼的流程。

表 2:運行落差規則會決定使用哪一個版本的程式碼字詞,以確保 DC 平衡。

試想以為資料字詞 10010001 編碼為例。3 個最高有效位元 (100) 會傳送至 3b/4b 表,5 個最低有效位元 (10001) 則會傳送至 5b/6b 表。如這是通道上第一個被傳送的字詞,則編碼器會假設 -1 落差;因此,此範例假設運行落差為 -1。5b/6b 部分無法進行選擇,而 3b/4b 部分則會決定落差是 +2 還是 -2。由於運行落差為 -1,因此會選取落差為 +2 (1101) 的 3b/4b 程式碼。結合 3b/4b 與 5b/6b 程式碼時,編碼後的總符碼會是 1101100011。傳輸此符碼後的運行落差即成為 +1 = -1 + 2。

64b/66b 編碼

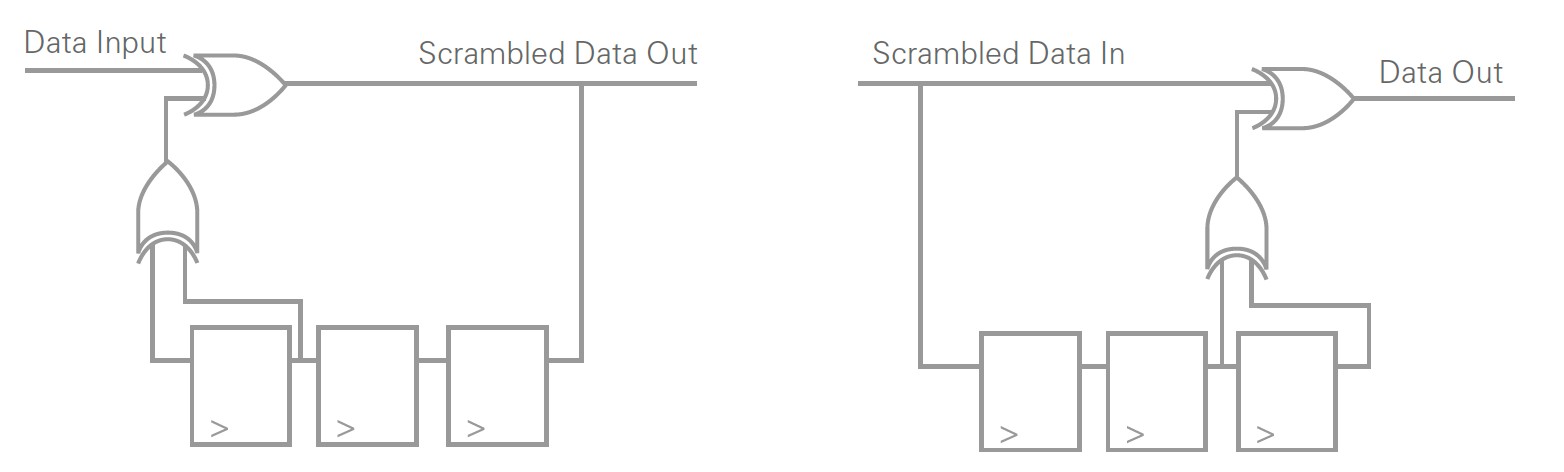

64b/66b 編碼使用不同於 8b/10b 的編碼方式,一樣可完成類似的作業。此編碼不使用程式碼表,而是使用擾碼。加擾需要一個硬體電路,其可提供多個高機率,相間或多或少平均的 0 與 1。加擾功能讓編碼資料顯得隨機且頻繁移轉,但仍可在接收器端進行解擾。

圖 7:加擾電路使輸出資料顯得隨機且 DC 平衡,但資料仍可在接收器上解擾。加擾是使用查找表為資料編碼的另一種方式。

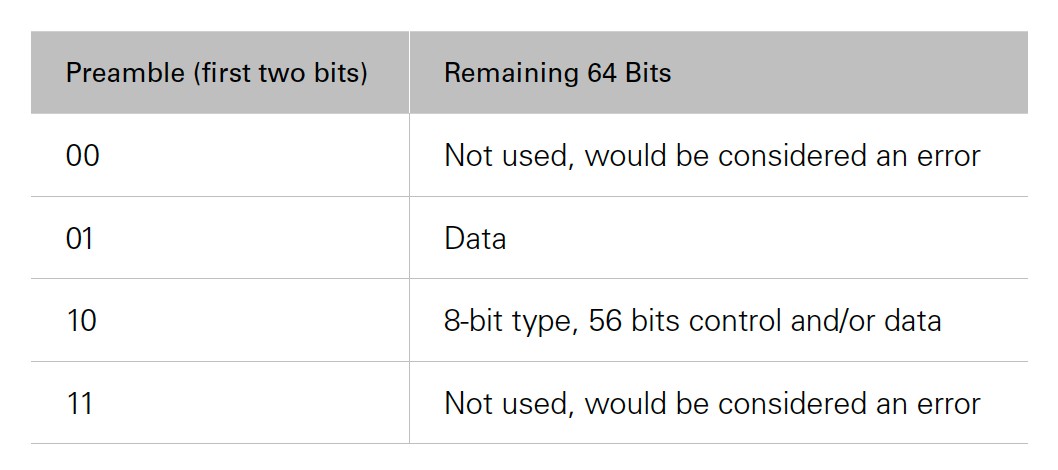

66 位元中的前 2 位元為前序編碼,並提供有關其餘 64 位元的資訊。與 8b/10b 相比,64b/66b 的主要優點在於系統負載較低。64b/66b 的系統負載比 3% 稍多,而 8b/10b 的系統負載則為 20%。64b/66b 編碼的一個缺點是,它不像 8b/10b 編碼那樣會對 DC 平衡造成限制。雖然加擾電路已備受肯定非常適合顯示隨機,且 DC 失衡在統計上不顯著,但 64b/66b 編碼並不像 8b/10b 那樣受約束。

表 3:64b/66b 符碼的前 2 位元均視為前序編碼。前序編碼將遵循前序編碼的 64 位元資訊提供給解碼器。表 3 的前序編碼意義應用於 10 Gigabit 乙太網路。

64b/67b

某些電子產品在一段時間後對 DC 偏移變得極敏感。64b/66b 編碼方案可能就是這種情況。由於 DC 偏移不受約束,因此設計人員可能不感興趣。在這些情況下,工程師對於 8b/10b 方案只能使用較高的負載 (20%)。64b/67b 方案會額外增加 1 位元的系統負載,由此將運行落差限制在 ±96 內。

傳輸器監控運行落差,並計算新的加擾程式碼字詞落差。如新程式碼字詞要降低落差數,就會傳輸該符碼。如新程式碼字詞要增加落差數,則編碼器會翻轉 64 加擾位元 (無需翻轉 0 落差的前序編碼)。額外的位元稱為逆轉位元,可通知解碼器是否需要逆轉資料。此讓對 DC 偏移敏感的晶片電子也能從負載低的編碼方案中受益,此方案本身也會呈現受約束的 DC 偏移。

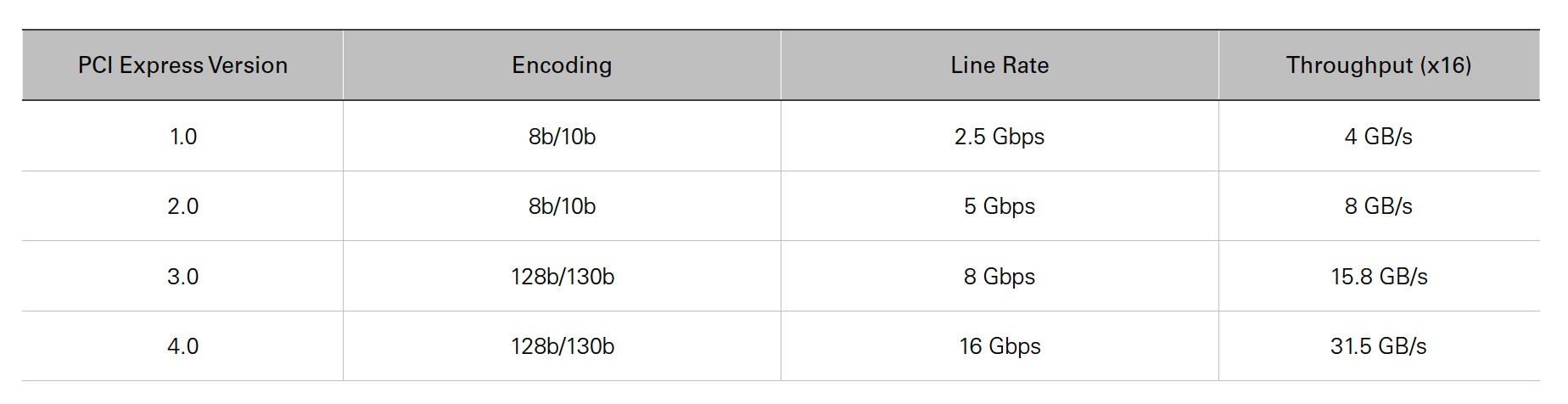

128b/130b

PCI Express 1.0 與 2.0 均使用 8b/10b,而 PCI Express 3.0 與 4.0 則升級至 128b/130b,以達到較高的資料傳輸率與通道速率。試想將 128b/130b 方案設為 64b/66b,其承載增加一倍,但仍只有 2 位前序編碼位元。表 4 顯示 PCI Express 規格。

表 4:下表顯示 4 代 PCI Express 規格。PCI Express 3.0 和 4.0 移轉至 128b/130b,以提高資料傳輸率,同時將通道速率維持在更易管理的速度。

控制符碼 (K 字元)

控制符碼 (在 8b/10b 編碼中也稱為 k 字元),是高速序列連結的重要功能。這些符碼可與資料區分開來,因此接收器可使用來執行不同的控制作業,例如解碼前的位元邊界校準、時脈修正技術,以及在多通道間確認資料一致性的通道彙整。

對齊與逗號偵測

為正確進行解碼作業,接收器必須知道編碼資料的正確字詞邊界。接收器針對控制字元掃描輸入資料,此字元在 8b/10b 方案用於對齊時也稱為逗號。控制字元為編碼資料的邊界下定義。一旦接收器識別出對齊字元,對於編碼資料則具備了字詞邊界概念,因此可將編碼資料傳送至解碼邏輯。

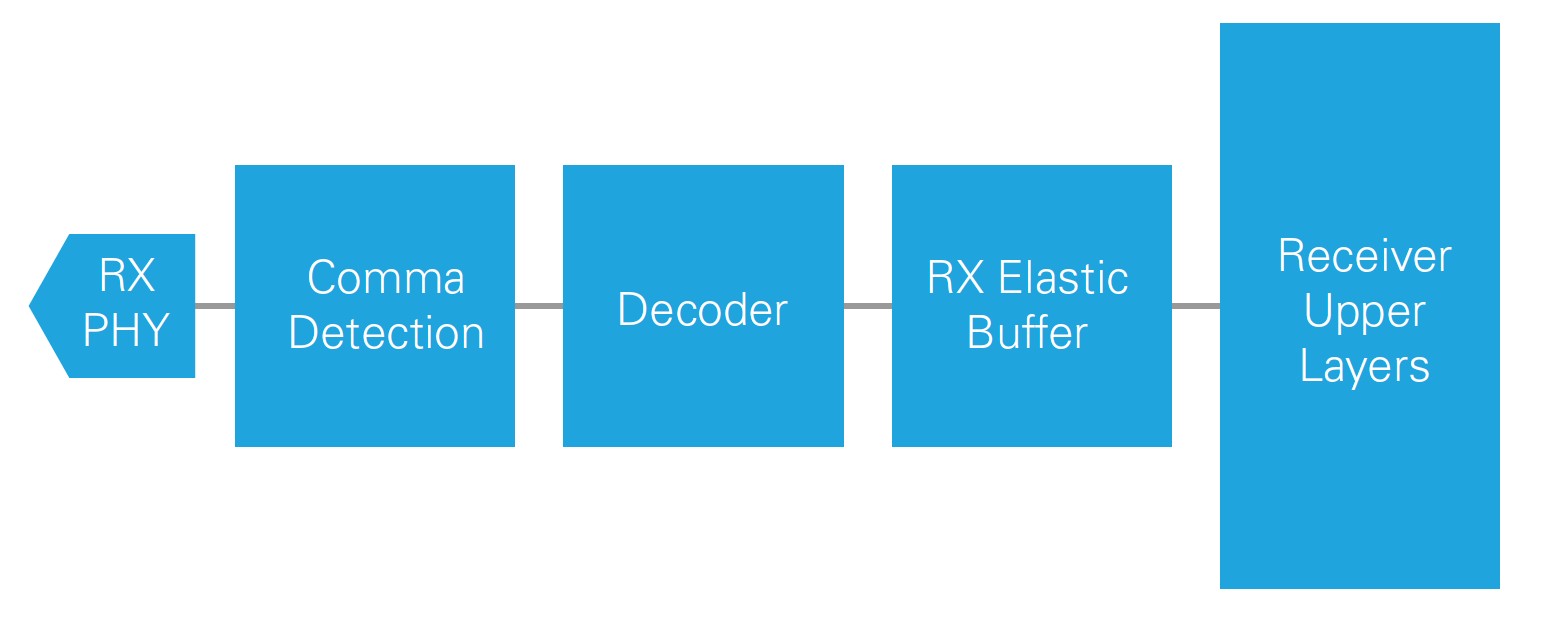

時脈修正字元

只要傳輸時脈未鎖定在與接收時脈相同的來源,就必須進行時脈修正。即使這些時脈屬於相同的額定頻率,也會因為小量不準確的時脈頻率而緩慢漂移。先進先出 (FIFO) 記憶體緩衝有時也稱為彈性緩衝,可讓接收器計算存在傳輸器與接收器之間的微小時脈差異,並執行時脈修正。

圖 8:需要有解碼器與接收器上層之間的 RX 彈性緩衝,才能執行時脈修正作業。其可緩衝資料,防止因時脈未鎖定彼此漂移而造成錯誤,並可在不共用參考時脈的情況下,於 2 組裝置之間進行通訊。

時脈修正邏輯可確保彈性緩衝絕不會發生溢位或虧位。如傳輸時脈運行的速度略快於接收時脈從彈性緩衝讀取的速度,且沒有時脈修正技術,就會發生溢位。當傳輸時脈的運行速度略慢於接收器上的讀取邏輯,且未進行時脈修正,就會發生虧位。

控制字元被選做為時脈修正字元。傳輸器傳送此一定期與實際資料疊插的時脈修正字元,而時脈修正字元的頻率則視應用與硬體設計的時脈修正需求而定。如接收器上的時脈修正邏輯偵測到接收器上的彈性緩衝即將虧位,則接收器修正邏輯會插入額外的時脈修正字元,以確保緩衝不會發生虧位。若時脈修正邏輯偵測到彈性緩衝越來越滿且即將溢位,則邏輯會捨棄緩衝中的時脈修正序列,好為資料建立額外的空間。

通道彙整

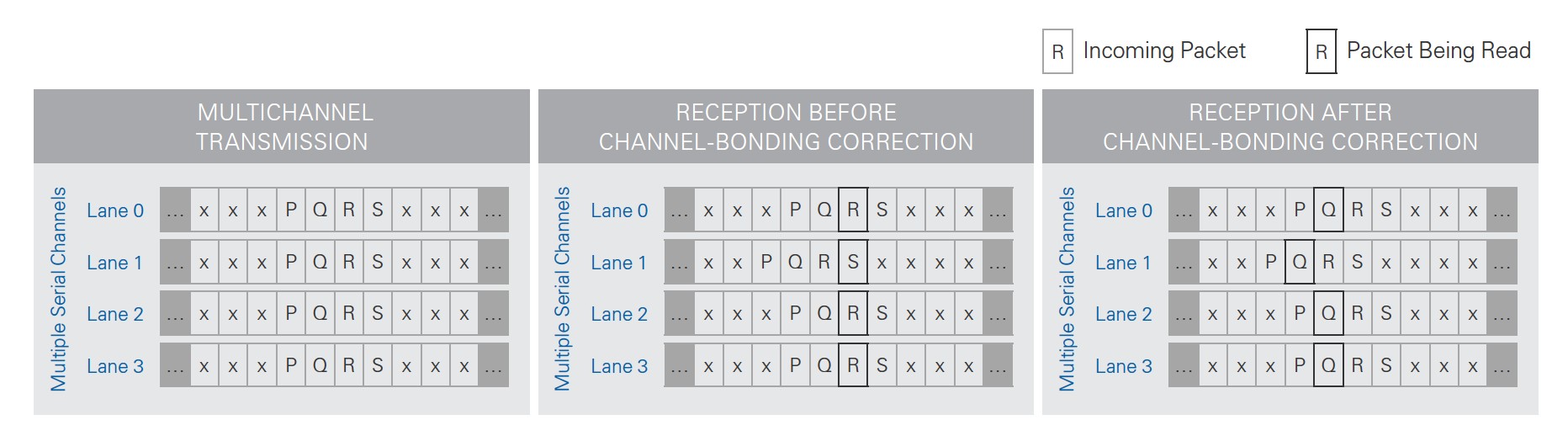

如通道速率與編碼方案無法在單一序列通道上達到所需的資料傳輸率,則可使用多個通道。舉例來說,HDMI 標準使用 3 組序列資料通道,以達到整體的資料頻寬。當在多個通道間傳送資料時,傳播延遲會導致資料在不同時間抵達接收器的各個接收通道。接收器可能需要在所有通道間對齊資料,視應用而定,此過程即稱為通道彙整。接收器各接收通道中的彈性緩衝可用於時脈修正作業,亦可用於通道彙整。

如要達成通道彙整,必須選擇特殊控制字元,並保留用於通道彙整。序列連結有 1 個主通道,其他通道則被視為附屬通道。主通道和所有附屬通道會同時從傳輸器傳送通道彙整字元。當主接收器看到彈性緩衝特定位置的通道彙整序列時,就會指示所有附屬接收器找出自己的彙整序列,並對通道彙整序列位置的偏移,調整所有彈性緩衝的讀取指針。由於各資料通道的彈性緩衝均各有偏移量,因此接收器可從每一個彈性緩衝的不同位置進行讀取,因此讀取的資料是對齊的。

圖 9:通道彙整會改變各接收通道上彈性緩衝的讀取指針,使接收器能在多個資料通道間讀取同步資料。

閒置字元

控制字元的另一個重要使用案例是閒置字元。若要讓時脈與資料還原功能保持相位鎖定,則傳輸器必須持續傳送位元。當沒有資料可傳送時,就必須傳送一個閒置字元。這是由協定所決定的另一個控制字元,接收器知道此控制字元並非真實資料。

額外的上層

額外的上層位於資料連結層之上,可根據特定需求來客製化通訊方式。有些協定對上層功能設立特定標準,而其他協定則讓使用者自行決定。常見的通訊客製化功能包含錯誤檢查/修正、封包架構通訊的表頭資訊,甚或是連結狀態資訊。

資料連結層與實體層之上的層級,往往是針對特定應用需求而客製化的層級。常見的上層客製化範例如:循環備援檢查 (CRC) 與前向錯誤修正 (FEC) 所提供的錯誤偵測與修正。如要以資料傳輸效率為代價,則可使用錯誤偵測或修正方案。CRC 執行規則以偵測傳輸中的位元錯誤,但無法修正錯誤。可客制化應用,以重新索取資料。相反地,FEC 在傳輸資料中包含額外的錯誤修正資訊,可讓接收器從數量有限的位元錯誤中復原。此功能適用於高雜訊通道或高通訊速率,以致因訊號完整性而導致的位元錯誤更常見。包含 FEC 的設計決定會犧牲資料傳輸效率,以滿足放寬的訊號完整性需求。

結論

必須克服高速序列連結多個層級的眾多挑戰,才能成功進行通訊。了解每個層級的不同概念,有助於執行並測試不同的層級。若要讓每一個層級發揮作用,必須讓其下方的層級正確發揮功能。使用者可透過從為實體與資料連結層所定義的眾多規格中擇一使用,無需要自己決定初階細節。使用標準實體與資料連結層的另一項優點是,網際網路協定 (IP) 可執行所有這些初階的詳細內容。Xilinx Aurora 協定即為最佳範例,這款免費 IP 可執行輕量級資料連結層協定,適用於點對點序列通訊。如此將有助於涵蓋小細節,例如時脈修正、通道彙整、閒置字元、編碼/解碼等,讓使用者可專心處理與應用相關的較高層級。

高速序列連結以較小的體積、耗電量和較高的效能,越來越受到人們的愛戴。通訊產業持續改良高速序列技術,使通道速率更快速,以適應大數據時代。