數位狀態、電壓準位與邏輯族

綜覽

了解數位訊號的數位狀態、電壓邏輯準位以及邏輯準位族。此教學文件屬於「儀器基本原理」系列的一部分。

內容

數位狀態

數位裝置中只有兩種狀態:開和關。裝置只需要使用這兩種狀態,就能傳輸大量資料,也能控制各類其他裝置。二進位制以 1 或 0 表示這兩種狀態。一般認定二進位 1 是邏輯高,0 則是邏輯低。

電壓準位

不過,驅動數位裝置的,通常是有著無數種類型的類比裝置。如何將無數種狀態轉換成單純 2 種狀態?方法就是建立電壓邏輯準位,用於定義代表邏輯高或邏輯低的電壓。

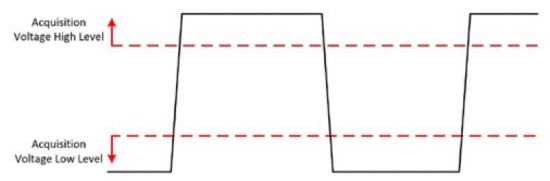

圖 1: 電壓準位定義代表邏輯高或邏輯低的類比電壓。

系統可將電壓邏輯準位定義在系統所選的任何值,但許多電路是以 +5 V 或 +3.3 V 到接地代表邏輯高,以接地或 0 V 代表邏輯低。這類系統稱為正系統或高活動系統。這類系統說明針腳啟動方式:高活動針腳要接高電壓。

負系統或低活動系統則相反。電壓較高代表邏輯低,而電壓較低則代表邏輯高。若是低活動針腳,必須將針腳接地,將針腳拉低。資料表通常會在針腳名稱上方加註一條線,表示這是低活動針腳,比方說 EN。

儘管指定了高低,大多數系統其實是有範圍的,這是為了提高實用性。舉例來說,邏輯高可以是 2 V 到 5 V 之間的任何值,邏輯低則可以是 0 V 到 1 V 之間的任何值。超出這些範圍的電壓視同無效電壓,唯有在發生故障或進行邏輯準位轉換的階段,才會出現無效電壓。

Z 與 X 狀態

數位訊號只能有開和關兩種狀態,但您可以使用其他狀態輔助擷取及產生數位訊號。以三態邏輯來說,就會出現第三種可能的條件:輸出與線路中斷的高阻抗狀態。這種狀態不分高低,而是浮動或高阻抗狀態。其代號是 Z,用途通常是啟動線。

Z 狀態最普遍的用途是測試一或多條可由多個傳輸器驅動的數位線路。記憶體晶片上的資料埠就是一個很好的例子。電腦寫入記憶體裝置時,需在記憶體裝置的資料針腳 (0 或 1) 上驅動欲寫入至記憶體晶片中的資料。之後,當電腦處理器需要讀取記憶體中的內容時,記憶體裝置必須將先前預存的資料值驅動回電腦處理器 (通常是資料針腳上的 Z 狀態)。

第四種狀態是代號 X 所代表的「保持」狀態。產生數位訊號時,可以讓裝置將通道保持在目前的狀態,不論任何狀態皆可。設定初始或閒置狀態時,這個狀態就能派上用場。

擷取資料時,X 狀態會有不同的代號,就是「無關」。比較擷取到的數位訊號與預期的訊號時,這個狀態可以派上用場。舉例來說,在一個由 10 個值組成的訊號中,您只在意前四個值。此時您可以用 X 代表最後六個值,只比較前四個值即可。

| 狀態 | 代號 |

|---|---|

| 0 | 邏輯低 |

| 1 | 邏輯高 |

| Z | 高阻抗 |

| X | 保持狀態或無關 |

表 1: 數位訊號的狀態只能是高或低;不過,若是需要產生或擷取數位訊號的用途,Z 與 X 狀態仍然可以發揮輔助作用。

邏輯族

標準化的邏輯族可以簡化電路與元件的處理流程。這類邏輯族提供構成邏輯高或邏輯低的標準化電壓準位。邏輯族內的電路全數與同一族當中的其他電路相容,這是因為這些電路有著相同的特性。

單端點邏輯族

單端點邏輯族指定相對於接地的電壓準位。四個準位的定義如下:

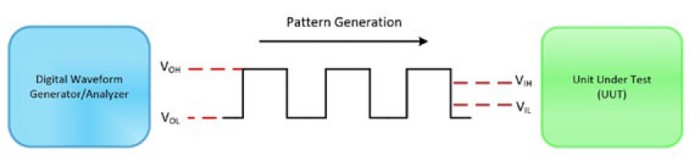

- VOH (輸出高準位電壓) – 又稱為產生電壓高準位。設定產生主動驅動時,這就是裝置產生邏輯高時所產生的電壓。設定產生集電極開路產生時,等於將資料通道設定為高阻抗狀態。

- VOL (輸出低準位電壓) – 又稱產生電壓低準位。這是裝置產生邏輯低時所產生的電壓。

- VIH (輸入高準位) – 又稱為擷取電壓高準位。這是必須傳送到裝置才能讓裝置讀取邏輯高的電壓準位。

- VIL (輸入低準位電壓) – 又稱為擷取電壓低準位。這是必須傳送到裝置才能讓裝置讀取邏輯低的電壓準位。

圖 2: 指定輸出和輸入的單端點邏輯準位。

為了能與裝置準確通訊,設定數位裝置時,一定要符合下列條件:

- VOH ≥ DUT VIH

- VOL ≤ DUT VIL

- VIH ≤ DUT VOH

- VIL ≥ DUT VOL

- VIH > VIL

裝置的輸出電壓與其他裝置的輸入電壓之間,通常會有緩衝,這就稱為雜訊邊限或雜訊抗擾準位 (NIM)。如果您所在的環境雜訊較高,而且難以處理不正確的資料位元,不妨考慮提高這個值。

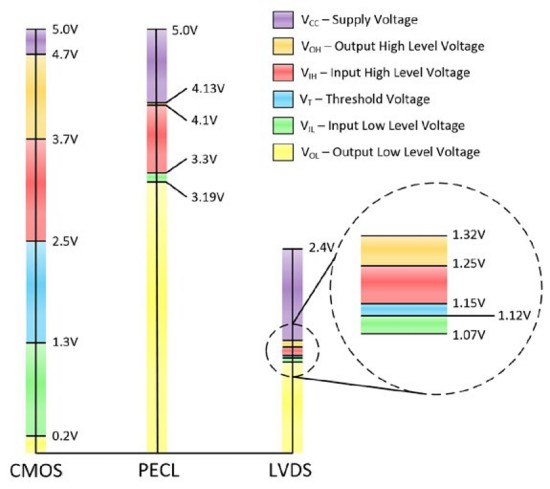

單端點邏輯族分為數種。電晶體-電晶體邏輯 (Transistor-transistor logic, TTL) 常見於積體電路,用途相當廣,例如電腦、消費性電子產品以及測試設備。以雙極性電晶體製作的電路會進行切換並保持邏輯狀態。TTL 還必須符合特定的電流規格,以及上升/下降時間,請參閱 TTL 相容訊號的定義是什麼?。

圖 3: 標準 5 V TTL 電壓準位

另一種常見的 IC 族是 CMOS。這些裝置的雜訊抗擾度高,耗電量低,基礎電壓也較低。大部分的電壓準位皆與 TTL 裝置相似,相容性更好。由於如此,從 TTL 改為 CMOS 裝置會比較容易,但反過來就未必了。CMOS 電壓過高可能會損壞晶片。在這種情況下,可以使用分壓器降低電壓。

圖 4: 標準 CMOS 電壓準位

差動邏輯族

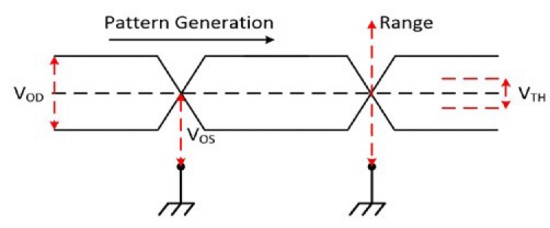

單端點邏輯族使用與接地相關的固定電壓準位;而差動邏輯族則使用兩個數值的差,不是接地參考。要將差動訊號解析為邏輯低,訊號必須小於其互補訊號,且兩者的差要高出特定的值,這就是所謂的臨界值 (VTH)。由於會同時參考及傳輸這些訊號,因此,相較於使用單端點邏輯族,這種方式較能夠提高訊號的抗擾度。指定差動邏輯族的電壓準位時通常是以差動為準,而不以絕對電壓為準。四個準位的定義如下:

- VOD (輸出差動電壓) –這是訊號之間的電壓差。

- VOS (偏移電壓) – 這是差動訊號的共模。您可以將它想成這兩個訊號的平均值。這是接地參考。

- VTH (臨界電壓) - 這是裝置記錄有效邏輯狀態所需的電壓差。

- VRANGE (輸入電壓範圍) – 這是絕對電壓,其參考值是裝置允許的接地電壓。

摘要

- 電壓邏輯準位定義電壓代表的是邏輯高或邏輯低。

- 許多電路以 +5 V 或 +3.3 到接地代表邏輯高,以接地或 0 V 代表邏輯低。這類系統稱為正系統或高活動系統。

- 在三態邏輯中,Z 狀態是高阻抗狀態,其用途通常是啟動線。

- 於數位產生中,X 狀態會維持目前的邏輯準位。在數位擷取中,這個狀態代表「無關」狀態。

- 邏輯族提供構成邏輯高或邏輯低的標準化電壓準位。

- TTL 以 VCC = 5 V 為準。

- CMOS 以 VCC = 3.3 V 為準。

- 差動邏輯族使用兩個數值之間的差,不是接地參考。

- LVDS 是低雜訊、低功率且低振幅的差動方式,其 VCC= 3.3 V。

- LVPECL 電路是其中一種 ECL 電路,其每個通道各需要一對訊號線 (VCC= 3 或 3.3 V)。