在NI FlexRIO中使用DRAM

概述

内容

使用DRAM

本地LabVIEW FPGA接口通过内存连接DRAM。该接口简化了与模块上物理DRAM通信、DRAM资源的竞争请求仲裁以及内存分段(以最大化使用灵活性)的底层复杂性。因此,该接口可帮助用户轻松地读写DRAM。

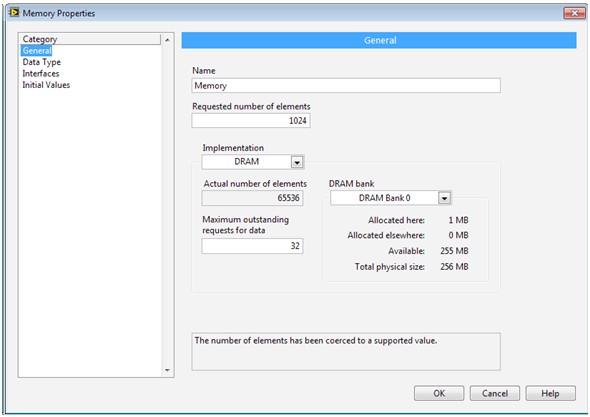

DRAM内存项可在全局项目视图中以与块内存或查询表相同的方式创建。如要创建DRAM内存项,请右击您希望为其创建新内存项的目标,然后选择“新建»内存”。接着选择“DRAM”。每个内存项对应一个DRAM库(bank),如果没有其他内存项分配给选定的DRAM库(bank),该内存项可以覆盖整个库(bank)。

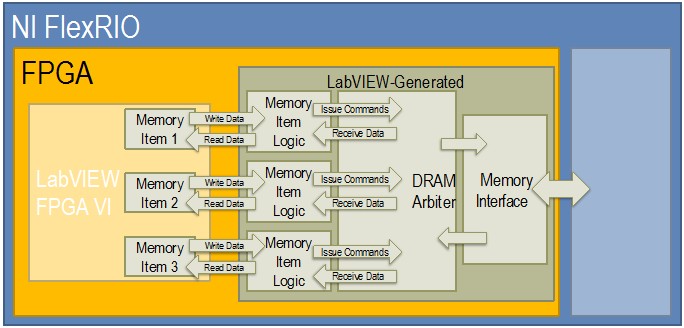

通过内存项,您可以将完整的DRAM空间分割成多个小内存块,这样每个小内存块可以通过LabVIEW FPGA代码的不同部分进行独立访问。 LabVIEW创建仲裁代码,使所有对应接口可均等地访问DRAM。下图是LabVIEW生成的逻辑,提供了特定DRAM库的访问。

写入方法

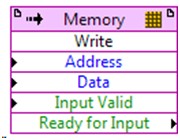

下图中的写入方法非常直接明了。写入时需要指定一个地址以便输入数据。当Input Valid的输入为真时,写入命令便会进入接口。Ready for Input端口指示接口是否准备就绪,如果端口的值为假,则数据将被忽略。为了避免信息损失,只有在确保Ready for Input的值为真时才能将数据添加到写入方法中。

读取方法

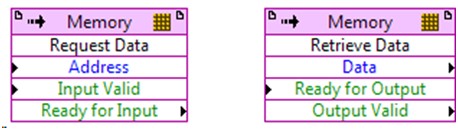

内存读取接口采用两种方法:请求数据和检索数据。第一种方法—请求数据首先接收目标数据的地址,然后通过内存控制器请求该地址上的数据。但请记住DRAM接受仲裁和非确定性事件(如DRAM刷新)请求后会存在较长的延迟。因此,数据并不是立即可用的。相反,所有请求根据接收的顺序排队和进行处理。经过一定时间后,检索数据方法显示接下来要请求的数据,并确定Output Valid的输出值以指示该数据是否可用。只有当Ready for Output端口的值设置为真时,数据才会显示,这向内存接口传递的信息是:将使用该数据的逻辑已经准备好接收数据。