簡介:NI FlexRIO 的 DRAM 使用方式

概觀

內容

使用 DRAM

LabVIEW FPGA 原本是透過記憶體物件來銜接 DRAM。 此介面有助於簡化某些初階的複雜作業,比如說與模組上的實體 DRAM 通訊、調停 DRAM 資源的競爭需求、劃分記憶體以便充分發揮使用彈性等。 因此使用者可享有簡易的 DRAM 讀寫介面。

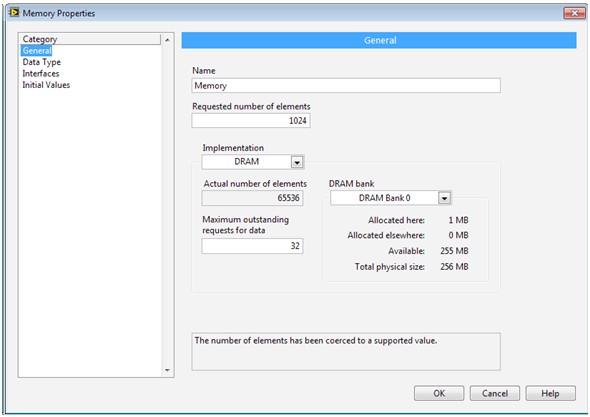

一旦建立 DRAM 記憶體物件,就會出現在整個專案畫面中,就像區塊記憶體或查找表 (Look-Up Table) 一樣。 如要建立 DRAM 記憶體物件,請用右鍵點選要建立新記憶體物件的目標,然後選取 New»Memory。 接著選取「DRAM」即可實作。 記憶體物件會指向一個 DRAM 組,而且如果沒有其他的記憶體物件分配到特定的 DRAM 組,此記憶體物件的大小可能會等同於整個 DRAM 組。

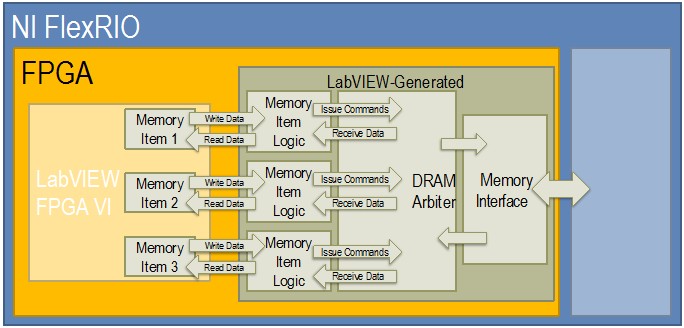

有了記憶體物件,即可把整個 DRAM 空間區分成較小的記憶體,並且可由不同的 LabVIEW FPGA 程式碼段落獨立存取。 LabVIEW 會建立調停程式碼,讓後續產生的介面都可以公平使用 DRAM。 下圖為 LabVIEW 所產生的邏輯,以便存取特定的 DRAM 組。

撰寫方式 (Write Method)

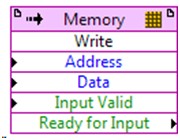

下圖所示的撰寫方式相當簡潔明瞭。 其中必須包含寫入位址,以及要寫入此位址的資料。 只要 Input Valid 的輸入值為 True,撰寫指令就會推入該介面。 Ready for Input 端點代表如果介面已就緒,資料值為 False 時就會被略過。 如要避免遺失資訊,請確保只有在 Ready for Input 為 True 時,才可以把資料推進撰寫方式。

讀取方式 (Read Method)

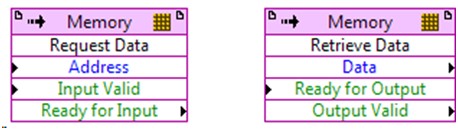

記憶體讀取介面分成兩個方式: 索取資料 (request data) 與擷取資料 (retrieve data)。 第一個索取資料方式會接收所需的資料位址,並且從記憶體控制器來索取該位址上的資料。 但是請記得,如果出現調停需求或 DRAM 更新等非精確事件時,DRAM 的延遲時間就會變長, 所以無法立即取得資料, 而且還要按照接收順序來處理這些需求。 經過一段時間之後,擷取資料方式就會顯示下一筆所需的資料,而且輸入會顯示為 Output Valid,代表已經可以取得資料。 只有在 Ready for Output 端點設為 True 時才會呈現資料,並且會通知記憶體介面,要消耗資料的邏輯已準備好接收這筆資料。