衛星通訊匯流排介面選擇

綜覽

通訊匯流排或數位航電介面是衛星和發射載具的功能測試系統中不可或缺的部分,但選擇合適的儀器並不簡單。某些標準介面匯流排可透過現成可用 (COTS) 裝置來處理,而其他介面匯流排具有獨特的需求,或僅適用於專屬的儀器。NI、PXI 儀器廠商的社群,可以透過各種產品選項滿足常見、不常見、甚至是客制介面的需求。本文討論測試通訊匯流排的基礎技術需求和選擇模組化系統方法的優勢。

內容

介紹

測試工程師大多認同「工欲善其事,必先利其器」的道理。 這是因為選錯工具不僅浪費時間,還會影響品質。反之,只要選用對的工具,便能在短時間內得到令人滿意的成果。

針對整合、檢查和大量製造測試,建立電子地面支援設備 (EGSE) 或特殊檢查 STE (SCOS,STE 代表特殊測試設備) 時,主要會運用量測和激發儀器等工具。這些儀器的商品除了多功能數位電錶 (DMM)、示波器與波形產生器等現有的產品之外,也不斷推陳出新其他商品,例如向量訊號收發儀與多合一示波器。「工欲善其事,必先利其器」看似簡單,實踐起來卻非如此。在遍覽與評估各項產品的優劣時,箇中難處更是令人苦不堪言。同樣的道理也能套用到商品化和專用的同類型儀器,然而,在考量衛星通訊匯流排介面時,團隊通常並未抱持同樣嚴格的態度。

在考慮用於驗證和整合測試的 EGSE 儀器清單時,測試工程師慣於查閱其測試計畫,並評估市面上的儀器,確保安裝合適的儀器,提供完整量測範圍,以滿足測試計畫的需求。

通常,特定受測裝置 (DUT) 的測試計畫需要額外的步驟,才能使 DUT 進入特定的狀態,或傳送指令,並接聽預期的回應。此情況在測試飛行和系統控制器時尤為如此。這些步驟包含執行品質保證檢查、執行一部分航電匯流排本身上的設計驗證步驟,或是記錄回應以供稍後分析或播放。為了確保 EGSE 內建這種功能,測試工程師通常會考慮 DUT 用於通訊的協定,以及商用現成 (COTS) 市場上符合其需求的儀器。

選擇最佳匯流排介面儀器

根據測試資產平台和特定 DUT 的組合,特定航電匯流排介面儀器有多種選擇。考慮到最常見的協定時,例如 MIL-STD-1553、ARINC-429 和 SpaceWire,市面上數個儀器提供者有現成可用的選項,可滿足需求。然而,考量到高速或骨幹匯流排,例如光纖通道 (特別是 SpaceFibre)、Serial RapidIO (SRIO)、AFDX、高速資料匯流排 (HSDB) 和 IEEE-1394b,或應用程式特定的匯流排,例如 ARINC-708、ARINC-717 或 ARINC-818 時,選項變得越來越複雜,並涉及到更多考量。

SpaceWire 等許多匯流排介面已變得如此普遍,以至於介面儀器都已商品化。對於測試設備廠商而言,將實體資料連結和網路層整合至固定式功能的裝置是更具經濟效益的做法。例如,STAR-Dundee 提供多個 PXI 模組,可用來介接和切換 SpaceWire 匯流排訊號。如同採用其他廣為使用之通訊協定 (例如 GPIB) 的硬體層級儀器一樣,這些儀器在不同的廠商之間都具有類似的架構,可符合特定的標準。

測試設備廠商可能在開放系統互連 (OSI) 模組 (其中運用了特定特色或功能來支援協定) 的更高資料層,將產品與其他產品區分開來。這些包含錯誤偵測、排程靈活性、時間戳記、資料記錄和故障植入等。某些製造商也提供在每個個別 OSI 層的資料存取權,以供監控或除錯。對於系統層級的驗證和整合測試需求,許多更細微的特色往往對應用程式的成功沒有太大影響,因此通常會根據工程師的偏好來做決策。

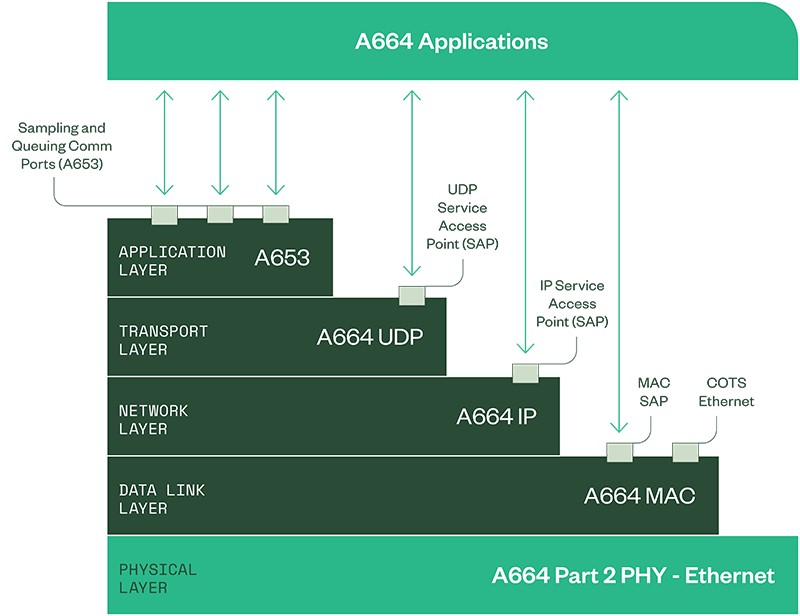

圖 1.ARINC-664p7/AFDX OSI 層的簡化檢視

當測試系統需要高速/骨幹或應用特定的協定介面時,以往並不困難的選擇決策就變得更具有挑戰性。在將這些協定整合至其測試系統時,測試工程師經常忽略相關的複雜性。這些更高效能協定帶來的主要挑戰之一,就是將資料傳輸從平行轉為序列。

序列標準越來越受到歡迎,因為平行匯流排時脈速率的實體限制約為 1 GHz 到 2 GHz,個別時脈和資料通道帶來的偏移會以更快的速率造成位元錯誤。高速序列匯流排傳送的編碼資訊會將資料與時脈資訊包含在一或多個差動訊號中,可讓您擺脫平行匯流排受到的速度限制。此外,使用具有進階功能 (例如時脈還原、預先強調和等化) 的特殊高速序列硬體收發儀,可以進一步推動這些優勢。

高速序列協定介面的設計可讓收發儀在最新的 FPGA 技術上順暢地執行。例如,最新 Xilinx FPGA 的多 Gigabit 收發儀的執行速度可以超越 30 Gb/s,使其成為做為通訊協定資料處理器的理想候選項目。除了這些儀器硬體設計的複雜性,協定 IP 本身也較商品儀器更複雜,因為協定的功能往往更齊全,且因為處理資料速率的次方增加所需的複雜性,對資料的需求也更嚴格。

提到將特定高速/骨幹或應用特定協定介面整合至 EGSE 時,工程師通常會面臨許多選項。

- 選項 1 是查看 COTS 市場,並尋找提供相關介面的廠商。此外,由於硬體設計和 IP 的複雜性,工程師通常必須與兩家廠商合作,一家負責高速序列硬體,另一家則負責協定 IP 核心。

- 選項 2 是利用內部驗證團隊對於相關 DUT 的設計,將 IP 核心與客制或現成可用的 FPGA 評估機板結合,並整合至 EGSE。雖然利用內部客制設計看起來很吸引人,但往往會有看不見的風險,可能會隨著時間大大提高支援負擔。

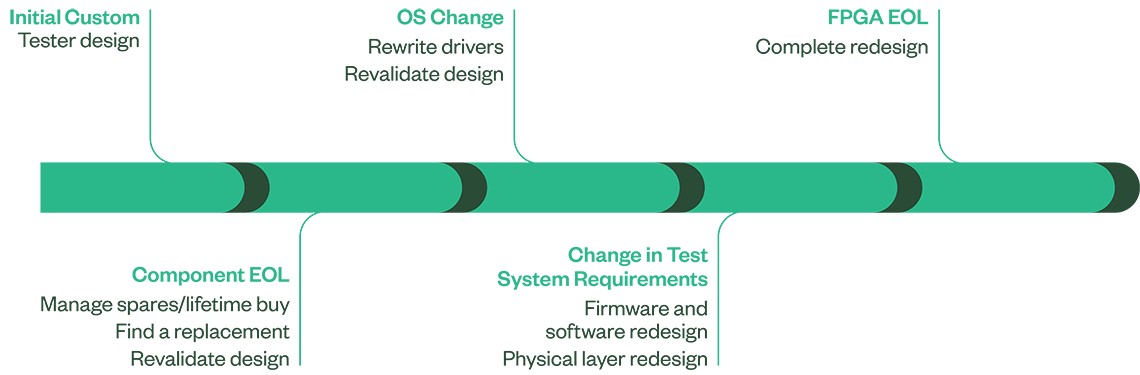

圖 2.「內部開發」測試系統的生命週期管理

若要說明這一點,圖 2 描繪了測試系統使用週期的範例,以及隨著時間影響該系統維護成本的事件。在完整設計 EGSE 後,請考量結束 (EOL) 客制機板上的元件。這畢竟是預期的狀況,因為半導體技術的更新週期往往反映了商業市場。如果設計的採用是來自驗證團隊,就特別有可能發生這種情況,因為生命週期考量很可能未包含在設計需求中。

像這樣的情況,基本上如果不想要終生購買該元件並管理備品,就必須尋找替代品並重新驗證硬體設計。試想需要強制進行 OS 升級 (例如 Windows 版本變更),或可能要移動到 Linux 的情況。接著就必須重新撰寫驅動程式和重新驗證軟體設計。如果需要增加測試機隨著時間變更的需求或是全新特色,那該怎麼辦?這可能需要重新設計韌體或軟體,或根據 DUT 的需求,甚至可能要重新設計實體層。最終,當 FPGA 邁向 EOL 時會發生什麼事?團隊無法透過簡單的途徑將這些元件升級,因此通常需要完整的重新設計。

對於在航太與國防產業中很可能需要維持數十年的測試系統來說,這是非常現實的情況。許多時候,當這些停產的挑戰發生時,設計原始 EGSE 與相對應測試軟體程式的人員已不在,無法協助任何維護作業。最後,前期設計成本僅占測試系統整個使用壽命中一小部分的成本

工程師應該盡可能考慮選項 1:COTS 架構的解決方案,特別是設計用於測試和量測應用的解決方案。即使具有內部能力,可設計和管理與衛星通訊協定介接所需的複雜軟體 IP,但考量到客制硬體的額外維護和維護負擔,COTS 方法仍會降低測試總成本。

NI 在衛星通訊匯流排介面中的角色

數十年來,航太和國防產業使用 NI 的模組化儀器和應用程式軟體,降低與其產品的測試和支援相關的整體成本和風險。在該期間,NI 開創了 PXI 平台,自該時期以來發佈範圍從 DC 到 mmWave 超過 600 個不同的 PXI 模組。除了傳統的儀器以外,NI、我們的合作夥伴網路,以及提供 PXI 平台元件 (例如 STAR-Dundee) 的 70 多個 PXISA 成員,也提供了整合、檢查和大量製造測試解決方案,讓您能夠同時保有靈活性,選擇「最適合工作的工具」,並涵蓋最完整的 PXI 架構匯流排介面範圍。

適用於製造和維修站測試的數位航電介面

一般介面:

- MIL-STD-1553

- RS-232/422/485

- ARINC-429

- CANbus

高速/骨幹介面:

- 光纖通道 (特別是 SpaceFibre)

- Serial RapidIO

- ARINC-664p7/AFDX

- 1394b FireWire

- 乙太網路 (最高達 40 GigE)

應用特定介面:

- ARINC-708

- ARINC-717

- ARINC-818

- SpaceWire

- DVI

必須採用客制設計的情況

在某些情況下,測試工程師可能會認為 COTS 方法不可行,且需要客制工程。最常被引用的範例是,測試透過特定客制版本協定進行通訊的 DUT。然而,即使是這類案例,也建議避免客制設計,以便降低測試 EGSE 的排程風險和未來的維護負擔。若要深入了解建立完整的太空電子測試系統,包含將 COTS 通訊匯流排介面硬體整合至測試系統來解決客制設計挑戰,請閱讀應用備註。