NI LabVIEW FPGA Compilation Options

Overview

Contents

- FPGAs Are Getting More Difficult (Not Easier) to Compile

- LabVIEW FPGA Compile System Overview

- LabVIEW FPGA Compile System Out-of-Box Options

- Offload FPGA Compilation

- Reduce Compile Time With Linux

- Next Steps

FPGAs Are Getting More Difficult (Not Easier) to Compile

The FPGA compiler is not one big monolithic algorithm. Instead, it is a collection of large, complex algorithms. The computational challenge takes your design through a flow that generates an optimized layout on a chip with millions of processing elements that you can configure in any way. The compiler uses synthesis to create a system of logical connections between processing elements. The compiler then maps, places, and routes in an iterative process to find the best solution and hooks everything up on the physical chip while attempting to stay within user constraints. As you can imagine, the mathematics behind finding a globally optimized solution to a problem that has infinite possibilities is nontrivial. As a result, FPGA compiles can take hours or even longer with higher density silicon.

To improve compilation time, you can offload your compile to a separate, high-end, dedicated Windows machine with a lot of RAM and a good processor. To further reduce compile time, you can install the Xilinx compilation tools on a Linux system to take advantage of compile tool performance optimization. NI architected the LabVIEW FPGA compile system to make it easy for you to set up either of these options within your own company, or even target your compilations to zero-maintenance, high-end computers in the cloud.

LabVIEW FPGA Compile System Overview

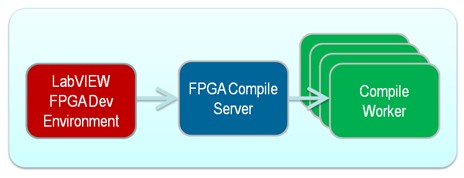

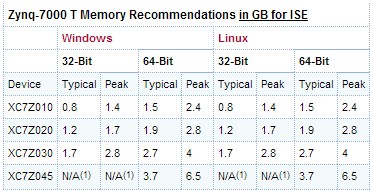

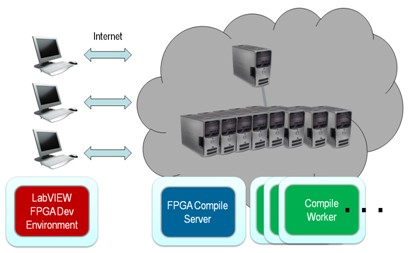

NI architected the LabVIEW FPGA compile system with three fundamental software components, which results in a modular, scalable compile solution. The compile system is split into three parts: the development computer, the compile server, and any number of compile workers.

LabVIEW FPGA Module Development Environment —The LabVIEW development environment that you are familiar with is where you create your application. Clicking Run on your FPGA VI completes the generating intermediate files step (see LabVIEW FPGA Compilation Process for more information). After generation, the development computer sends the intermediate files through web services communication to the compile server.

Compile Server—The compile server accepts compile jobs from one or many LabVIEW FPGA development systems and looks for available compile workers to farm out compile jobs to. If no compile workers are available, the compile server holds the compile job in a queue until a compile worker becomes available.

Compile Worker—The compile worker has the Xilinx compilation tools installed for FPGA design synthesis, mapping, placing, and routing. With these tools, a compile worker implements the design and generates a bitfile. The compile worker sends the bitfile back to the compile server, which, in turn, sends the bitfile back to the development computer.

Figure 1: The LabVIEW FPGA compile system architecture includes three parts: the development computer, the compile server, and the compile worker(s).

The benefit of this compile system architecture is that it supports multiple compile workers and the automatic farming of compile jobs. The compile server handles the queuing and farming, and is fault-tolerant to compile workers dropping in and out. In fact, if a compile worker drops out during a compilation job, the compile server detects this and farms the compilation to another available compile worker. Although the compile job has to start over, it finishes without any action on your part. Because the communication lines between the development environment and the compile server are all robust web services, the compile system is fault-tolerant to a number of development-side issues as well, like a development computer restart.

LabVIEW FPGA Compile System Out-of-Box Options

Out-of-box, the LabVIEW FPGA Module includes two compile system options. You can compile directly on your development computer or transfer the compile to a single, remote, dedicated compile machine.

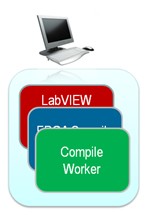

By default, LabVIEW installs one compile server and one compile worker on the development computer along with the LabVIEW FPGA Module. If you use LabVIEW 2009 FPGA Module or earlier, this setup behaves exactly the same way, with the compilation implementing on the development computer. To the compile server, it is as though the compilation were on a separate computer called “localhost,” because the system is designed from the ground up to support distributed compilation.

Figure 2: By default, the LabVIEW FPGA Module installs both the compile server and compile worker on the development computer and executes the compile job using the resources on the development computer.

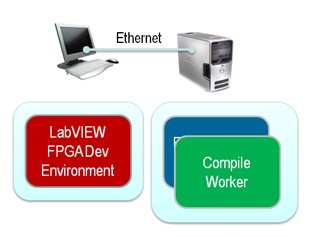

If you want to set up a more sophisticated compile system structure, you can install the compile server and a compile worker on another computer. To set up the remote compile server, install only the Xilinx compilation tools. For step-by-step instructions on this process, refer to the Installing and Activating the LabVIEW FPGA Compile Server on a Remote Computer article.

Figure 3: LabVIEW FPGA supports a simple, single-machine, offloaded compile server without any add-ons.

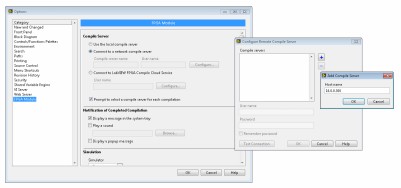

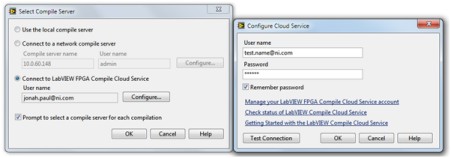

Once you install the Xilinx compilation tools on the remote computer, you can point the development machine to this new compile server by selecting Connect to a network compile server when you click the Run button. Alternatively, you can set this compile option from the Tools»Options»FPGA Module page.

Figure 4: Target the remote FPGA compile machine by selecting the compile system option and specifying where the server resides.

Offload FPGA Compilation

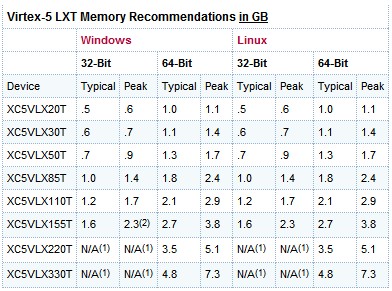

FPGA compilation grows computationally more complex and, as a result, longer, as developers use more sophisticated FPGA technology. To conserve resources on your development computer, the LabVIEW FPGA compile system architecture includes options to offload the compilation to dedicated computers. These should be high-end computers with good processors and high levels of RAM. Table 1 shows the minimum RAM needs for various Xilinx Virtex-5 FPGAs.

Table 1: Follow these recommended RAM guidelines for Xilinx Virtex-5 and Zynq-700 FPGAs. (Source: Xilinx Memory Recommendations Using the ISE Design Suite)

Performance for a compile job is most negatively impacted when the process is starved for system memory and has to page on the hard drive or, in some cases, quit. Follow the recommendations in Table 1 for the best results. For a 32-bit server, you should have 4 GB of RAM and only the Xilinx compilation tools installed. You can use the 3 GB Windows switch to maximize the amount of RAM the OS can allocate to the compilation. As you can see from the table, 64-bit systems should have more RAM installed. Of course, those systems can address much more than 4 GB of RAM, so, in this case, the more the better—up to 16 GB.

Offload to a Single Computer

You can use the LabVIEW FPGA Module to install the compile server and compile worker on a separate computer and target compilation. To do this, follow the steps in the Installing and Activating the LabVIEW FPGA Compile Server on a Remote Computer article.

Figure 5: A simple, single-machine, offloaded compile server is supported by the LabVIEW FPGA Module without any add-ons.

Offload to a Compile Farm

With the FPGA Compile Farm Server, you can create an on-site compile farm that includes multiple compile workers that may be targeted by multiple developers. Note: With LabVIEW 2013 FPGA Module and earlier, use the NI LabVIEW FPGA Compile Farm Toolkit.

The compile server is responsible for farming out compile jobs to all available compile workers. Compiles run in parallel because there are multiple compile workers. If there are no available compile workers, the compile server queues the requests, using FIFOs, and farms them out when a compile worker becomes available.

Figure 6: On-site compile farm architecture with one compile server and multiple compile workers.

Offload to an Online Compile Cloud Server

The final FPGA compile option uses the compile servers and compile workers that NI makes available online in the cloud. For ease of use, NI has added hooks directly from LabVIEW FPGA to enter a login, and with no additional installation, you can offload your compiles to the cloud. Compared to a standard Windows desktop, FPGA VIs experience a substantial reduction in compile times because the LabVIEW FPGA Compile Cloud Service runs the Xilinx compilation tools on Linux with the latest dedicated high-RAM high-end computers. When you compile in the cloud, you also can compile many VIs in parallel.

To target the cloud service, use the dialog box for the LabVIEW FPGA compile server, select the online cloud service, and enter your user name and password.

Figure 7: Connect to the cloud through LabVIEW to reduce compile time and offload compilations.

Once you have the compile cloud set up, the service compiles to the cloud rather than your local computer or local compile farm. The connection uses the latest IT industry security measures, which are similar to those used by other Internet services, such as banking.

Figure 8: Cloud architecture for offloading compilations.

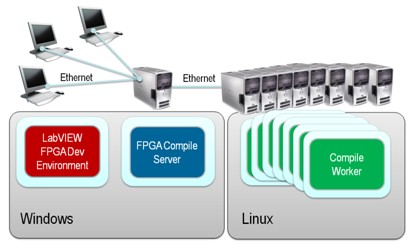

Reduce Compile Time With Linux

NI invests in supporting the FPGA compile worker on the Linux OS. Depending on your FPGA VI complexity and logic, you can expect the Linux compile worker to reduce compile times by approximately 20 to 50 percent, compared to a Windows compile worker. Xilinx originally designed and optimized the compilation tools for the Linux OS, which explains this substantial reduction in compile time.

Figure 9. LabVIEW 2012 FPGA and later support the Xilinx compilation tool installation on Linux machines, resulting in reduced compile times.

>> Explore the benefits of using the Linux FPGA compile worker in the cloud.

>> Learn more details on how to step up your own Linux FPGA compile worker.

Next Steps

The LabVIEW FPGA compile system provides flexibility through the compile server and compile worker architecture to offload the processor-intensive FPGA compilation process from your LabVIEW development computer. The LabVIEW FPGA compile system also reduces compile times by using a compile worker based on Linux. Once you have selected the FPGA compile option that is appropriate for your team, follow the links below to learn more about how to set it up.