NI FPGAデバイスでのDRAM使用方法

概要

内容

DRAMを使用する

DRAMへのネイティブLabVIEW FPGAインターフェースは、メモリ項目を介して行われます。このインターフェースは、デバイス上の物理的なDRAMとの通信に伴う低レベルの複雑さを巧みに抽象化し、DRAMリソースへの競合する要求を調整・制御し、メモリを最大限柔軟に利用できるようにセグメント化します。その結果、DRAMへの書き込みとDRAMからの読み出しを行うシンプルなインターフェースが実現されます。

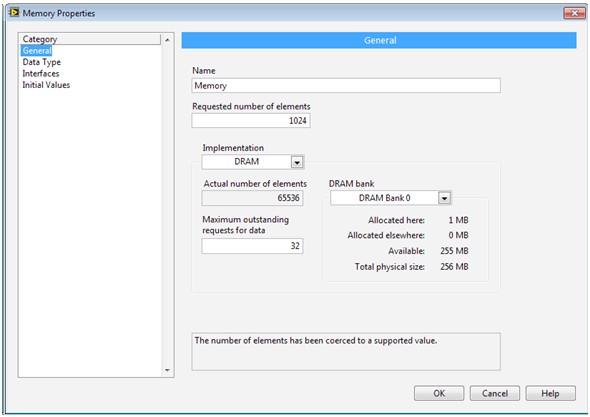

DRAMメモリ項目は、プロジェクトエクスプローラでグローバルに作成されます。DRAMメモリ項目を作成するには、FPGAターゲットを右クリックし、「新規作成」→「メモリ」を選択します。次に、実装に「DRAM」を選択します。メモリ項目は1つのDRAMバンクを対象とし、選択されたDRAMバンクに他のメモリ項目が割り当てられていない場合、そのバンク全体の容量になる可能性があります。

図1.「メモリのプロパティ」ウィンドウを使用して、DRAMメモリ項目の容量、データ型、およびDRAMバンクを設定

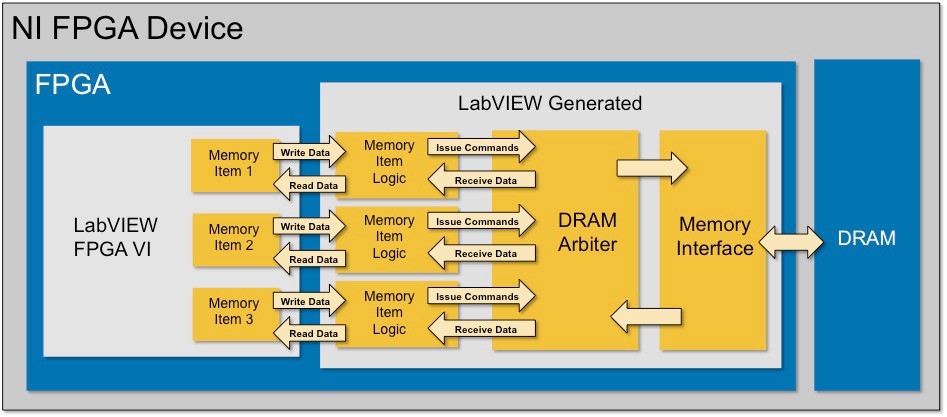

また、同じDRAMバンクを使用する複数のメモリ項目を作成することにより、DRAM領域全体を小さなメモリにセグメント化し、LabVIEW FPGAコードの異なるセクションから独立してアクセスすることもできます。LabVIEWは自動的にアービトレーションコードを処理し、生成されるすべてのインターフェースにDRAMへの平等なアクセス権を提供します。以下の図は、所定のDRAMバンクへのアクセスを提供するLabVIEWが生成するロジックを示しています。

図2.LabVIEWには、DRAMへの複数のインターフェースを処理するためのアービトレーションスキームが組み込まれている

書き込みメソッド

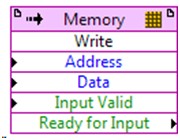

DRAMにデータを保存するには、以下の「書き込み」メソッドを使用します。書き込み先のアドレスと、そこに格納するデータが必要です。ハンドシェイク端子である「Input Valid」と「Ready for Input」は、有効なデータのみがメモリに書き込まれるようにするために使用されます。「Input Valid」入力にTRUEの値が書き込まれると、書き込みコマンドがインターフェースに送られます。「Ready for Input」端子は、インターフェースが新規データを受信できる状態かどうかを示します。「Ready for Input」がFALSEの場合、データは無視され、書き込みコマンドは実行されません。情報の損失を防ぐには、「Ready for Input」がTRUEの場合にのみ、書き込みメソッドにデータを送信します。

注:範囲外アクセスを回避するためのベストプラクティスに従ってください。メモリブロックのサイズを超えるアドレスへの読み書きは、非常に混乱を招く可能性があります。メモリブロックにどれだけの要素が割り当てられているかを常に意識してください。メモリメソッドのエラー端子を有効にすることで、メモリ領域外へのアクセスを検出できます。

図3.メモリ項目書き込みメソッドを用いて、データをDRAMに書き込む

読み取りメソッド

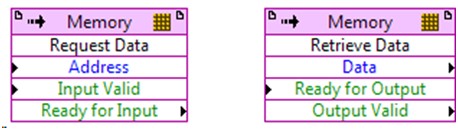

DRAMからデータを取得するには、2つのメソッドノードを使用します:「データを要求」と「データを取得」。最初のメソッドノード「データを要求」は、対象となるデータのアドレスを使用して、そのアドレスのデータをメモリコントローラに要求します。ただし、アービトレーションやDRAM更新などの非確定的発生の要件に加えて、DRAMのレイテンシは比較的長くなります。したがって、データは即座には利用できません。代わりに、要求はキューに入り、受信した順に処理されます。一定時間が経過すると、「データを取得」メソッドは、要求された次のデータを出力し、「Output Valid」をアサートしてデータが使用可能であることを示します。データは、「Ready for Output」端子がTRUEに設定されている場合にのみ返されます。これは、下流のロジックがデータを受信する準備が整っていることをメモリインターフェースに示すためです。

注:範囲外アクセスを回避するためのベストプラクティスに従ってください。メモリブロックのサイズを超えるアドレスへの読み書きは、非常に混乱を招く可能性があります。メモリブロックにどれだけの要素が割り当てられているかを常に意識してください。メモリメソッドのエラー端子を有効にすることで、メモリ領域外へのアクセスを検出できます。

図4.「データを要求」を使用してデータの要求を開始し、「データを取得」メソッドを使用してデータを取得

サポートされているデバイス

| DRAMバンク数 | サイズ/バンク | 帯域幅/バンク | ||

|---|---|---|---|---|

| Rシリーズデバイス | ||||

| PXIe-7821R | 1 | 512 MB | 800 MB/s | |

| PXIe-7822R | 1 | 512 MB | 800 MB/s | |

| FlexRIO FPGAモジュール | ||||

| PXI-7952R | 2 | 64 MB | 800 MB/s | |

| PXI-7953R | 2 | 64 MB | 800 MB/s | |

| PXI-7954R | 2 | 64 MB | 800 MB/s | |

| PXIe-7962R | 2 | 256 MB | 1.6 GB/s | |

| PXIe-7965R | 2 | 256 MB | 1.6 GB/s | |

| PXIe-7966R | 2 | 256 MB | 1.6 GB/s | |

| PXIe-7972R | 1 | 2 GB | 10.5 GB/s | |

| PXIe-7975R | 1 | 2 GB | 10.5 GB/s | |

| PXIe-7976R | 1 | 2 GB | 10.5 GB/s | |

| PXIe-7912* | 2 | 2 GB | 8.5 GB/s | |

| PXIe-7915* | 2 | 2 GB | 8.5 GB/s |

* これらの値は、対応するコプロセッサと同じFPGAを搭載したFlexRIO統合I/Oモジュールに適用されます。たとえば、PXIe-7915の値は、KU060 FPGAを搭載したすべての統合I/Oモジュールに適用されます。