NI-DAQmxによるPXI Expressモジュールの同期

概要

センサ計測システムの重要な側面の一つに、複数のチャンネルから集録したデータをどの程度時間的に相関させることができるかというものがあります。データが適切に時間的に相関されていない、つまり同期されていないと、テストデータから正確な解析結果や結論を得ることができなくなります。NIでは、確実な高性能同期が可能なNI SC Expressデバイスを提供しています。以降のセクションでは、同期の概念について説明するとともに、その活用方法を紹介します。

内容

PXIプラットフォームとSC Expressの同期に関する概要

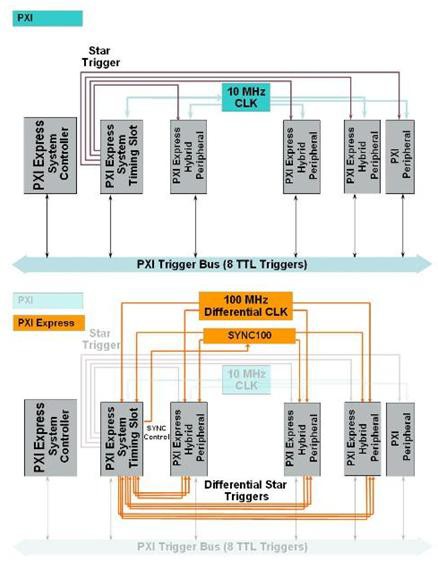

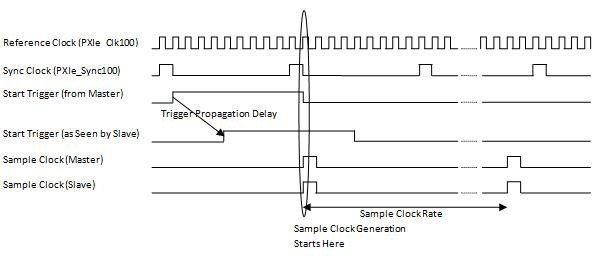

PXIプラットフォームの進化形であるPXI Expressは、下位互換性を保ちながら、計測I/Oデバイスで高度な同期性能を実現できるよう設計されています。PXI Expressでは、10 MHzのバックプレーンクロックに加え、本来のPXI仕様と同様にシングルエンド型PXIトリガバスおよびPXIスタートリガ信号に対応しています。また、100 MHzの差動クロックや差動トリガがバックプレーンに搭載されているため、耐ノイズ性が向上しているほか、業界最高水準の同期確度を実現しています。

PXI Expressバックプレーンには100 MHzの差動クロックが搭載されているため、複数のデバイスのサンプリングクロックが同じ基準クロックを共有することができます。バックプレーンのトリガラインにより、同じ100 MHzのクロックエッジでシャーシ内のすべてのデバイスを同期してトリガを行うことが可能となります。

図1.PXI Expressタイミング/トリガバスにより、バックプレーンで差動システムクロック、差動信号、差動スタートリガが利用可能

PXIシャーシの場合と同様、タイミング/同期モジュールを使用することで、1台のPXI Expressシャーシではバックプレーンクロックの代わりに精度の高いタイムベースを使用でき、複数台のPXI Expressシャーシでは計測デバイスの同期に使用できます。複数台のシャーシを長距離にわたって同期する必要のあるアプリケーションでは、GPSまたはIRIG-B PXIタイミングモジュールを使用することで、共通のクロック信号によりシャーシを同期することが可能です。

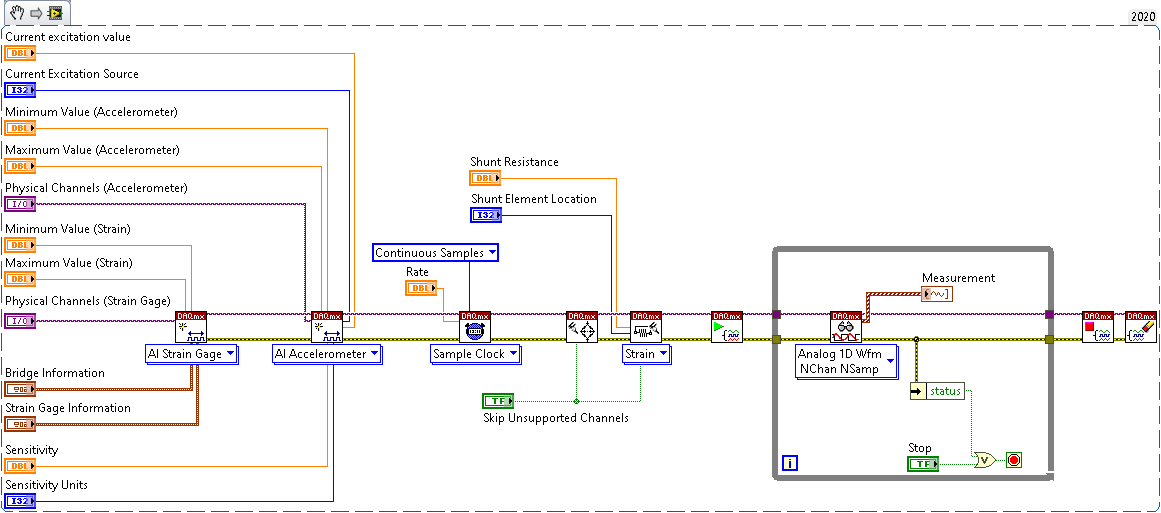

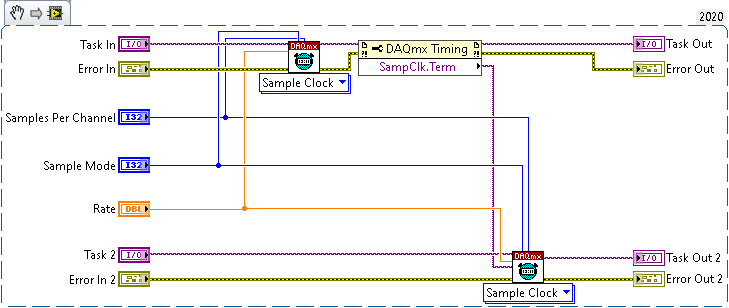

NIは、複数のSC Expressモジュールを同期するよう構成できる画期的な機能をDAQmxドライバに追加しました。単一タイプのSC Expressモジュールで構成されたシャーシ全体を、1つのマルチデバイスタスクでプログラミングできます。マルチデバイスタスクを利用すると、同じDAQmxコードを使用して、アプリケーションを1チャンネルから544チャンネルまで拡張できます。また、図2に示すように、単一のDAQmxタスクを使って、測定タイプの異なる複数のボード間でチャンネルを自動的に同期することができます。

図2.測定タイプの異なる複数のモジュールを集録するためのサンプルLabVIEWコード

このようにプログラミングした場合、SC Expressモジュールでは、PXI Expressシャーシの100 MHz差動クロックが基準クロックとして用いられ、バックプレーンのトリガラインが同期集録の開始の調整に用いられます。サポートされているマルチデバイスタスク構成の例を表1に示します。このように、SC Expressモジュールは強力な同期性能を発揮します。NI-DAQmxの特定のリリースでサポートされている、DSA、SC Express、Xシリーズでのマルチデバイスタスクの組み合わせについては、NI-DAQmxヘルプの「DSA, SC Express, and X Series Multidevice Tasks」トピック (英語) を参照してください。

SC Expressによるマルチデバイスタスクのサポート | モジュール間スキュー |

|---|---|

NI PXIe-4300:高電圧アナログ入力モジュール | 50 ns未満 |

NI PXIe-433x:ブリッジ入力モジュール | 150 ns未満 |

表1.マルチデバイスタスクでの同期性能

同期に関する一般的概念

このセクションでは、同期の背景にある概念について解説します。同期計測アプリケーションの設計前に、それらの概念を理解しておくことをお勧めします。

同期に関する用語

トリガ:トリガとは、集録を制御するコマンドです。トリガを使用して、集録の開始、停止、中断を行うことができます。トリガ信号のソースは、ソフトウェアとハードウェアのどちらでも可能です。

クロック:クロックとは、データの集録のタイミングを取るのに使用される周期的なデジタル信号です。状況によっては、クロック信号を使用してデータ集録を直接制御したり、基準タイムベースとして使用して別のクロックを生成したりできます。

非同期入力:非同期入力とは、デバイスのオンボードクロックで受信される外部デジタルトリガなど、入力の受信に使用されるクロック信号に対するタイミングの関連性が不明な入力を指します。他にも、ソフトウェアコマンドやアナログトリガイベントなどが挙げられます。非同期入力は、クロックエッジの前後で検出されます。クロックエッジに近すぎると、クロックエッジの前で検出されたか後で検出されたかを識別できなくなります。

単一のデバイスで入力を受信する場合、これは問題にはなりません。ただし、同じ非同期入力が複数のデバイスに送信される場合は、別のクロックエッジでの入力の変化が検出される可能性があります。したがって、複数のデバイスが同じクロックを共有していても、その動作は非同期となります。この問題を解決するには、マスタスレーブ同期を利用します。

マスタスレーブ同期:マスタスレーブ同期は、NI-DAQmxのドキュメントではトリガのスキュー補正とも呼ばれています。この方式では、1つのマスタデバイスで非同期トリガ入力を受信するよう指定します。 その後、このマスタデバイスから、すべてのスレーブデバイスに対してトリガが同期的に送信されます。マスタデバイスから各スレーブデバイスに送信されるトリガは、共通のタイミング基準クロックと同期しています。そのため、すべてのデバイスでは、基準クロックの次のエッジで確実にトリガイベントを検出できます。

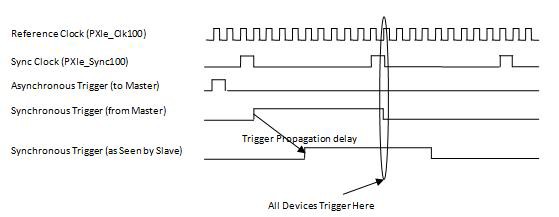

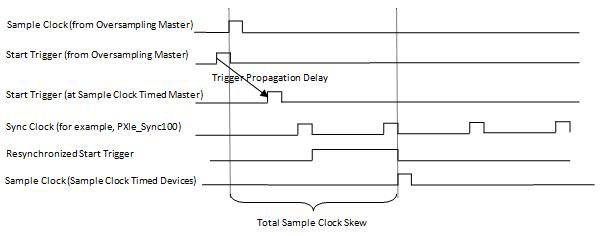

以下の波形は、この概念を表しています。

図3.マスタスレーブ同期

その結果、マスタデバイスでもスレーブデバイスでも正確な同期が実現できます。この方式における副作用の1つは、再同期化してトリガを送信するために1つから2つの基準クロック周期の遅延が生じることです。

マスタスレーブ同期に使用される基準クロックは、アプリケーションによって異なりますのでご注意ください。場合によっては、バックプレーンのPXIe_Sync100信号がこの目的に使用されます。また他の場合には、同期中のすべてのデバイスで共有している別の基準クロックが使用されることもあります (たとえばサンプリングクロックなど)。

同期信号接続

PXI Expressシャーシ内のデバイス間でクロック信号やトリガ信号を共有する場合は、多くの方法から選ぶことができます。信号の共有は、外部配線 (多くのデバイスにはそのための入力ピンが用意されています) またはPXI Expressバックプレーンのトリガバスを介して行うことができます。クロック信号とトリガ信号を共有するために用いるメカニズムは、同期確度にも影響を及ぼします。

| 信号 | PXI Expressのみ? | システムタイミングコントローラモジュールが必要? | デバイス間スキュー | 信号整合性 |

|---|---|---|---|---|

| PXIe_Clk100 | はい | いいえ | 250 ps未満 | 最適 |

| PXIe_DStar<A..C> | はい | はい | 500 ps未満 | 最適 |

| PXI_Clk10 | いいえ | いいえ | 1 ns未満1 | 適 |

| PXI_Star | いいえ | はい | 10 ns未満 | 適 |

| PXI_Trig<0..7> | いいえ | いいえ | 80 ns未満 | 普通 |

| 外部配線 | いいえ | いいえ | 可変 | 可変 |

1PXI_Clk10とPXIe_Clk100の間に最大6.5 nsのスキューが見られることがあります。そのため、PXI_Clk10を基準クロックとして使用する一連のデバイス間ではほとんどスキューは生じませんが、PXIe_Clk100を基準クロックとして使用する他のデバイスと比較すると、最大6.5 nsのスキューが存在する可能性があります。

表2.PXI Express差動Clk100およびDStarのトリガ信号は、同期レベルと信号整合性が最も優れています。

クロック信号をPXIe_Clk100、PXIe_DStar<A..C>、PXI_Clk10またはPXI_Star経由で分散して使用した場合、最高レベルの同期性能を達成できます。 PXI_Trig<0..7>バスは、バックプレーンで各モジュールに接続された共有バスです。 この共有バスによって、デバイス間でトリガを目的とした多くの接続が可能となり、非常に便利です。ただし、その結果として信号には大きな負荷がかかるため、長い伝搬遅延が生じます。伝搬遅延は、バックプレーン内のデバイスの位置によって異なります。さらに、信号整合性 (クロックの立ち上がりエッジと立ち下がりエッジの品質) も、バックプレーンに接続されたモジュールの数とタイプや、モジュールの位置、モジュールからPXI_Trigバスを駆動するのに使用する特定のハードウェアなどによってかなり変動します。信号の整合性が低いと、信号のノイズやジッタが多くなります。極端な例では、信号の1つのエッジが2つの別個のエッジのようになり、ダブルクロックとなります。 そのため、NIではPXI_Trig<0..7>ラインをトリガ信号のルーティング専用に使用することをお勧めしています。

同期の方法とオプション

さまざまなPXI Expressデバイスの同期方法を理解するには、各デバイスの基本となるアーキテクチャについて知る必要があります。広義で、デバイスは同期の観点から大きく2つのクラスに分けることができます。

- サンプリングクロックタイミングデバイス

- オーバーサンプリングクロックタイミングデバイス

サンプリングクロックタイミングデバイス

サンプリングクロックとは、サンプルを集録するタイミングを制御する信号です。サンプリングクロックタイミングデバイスでは、クロックエッジに応答していつでも変換を即座に開始できるA/D変換器 (ADC) を使用します。例としては、トグルによって即座に変換をトリガできる専用の変換ラインを通常備えている逐次比較レジスタ (SAR) ADCが挙げられます。そのため、このようなタイプのデバイスはクロック制御において高い柔軟性を誇ります。ADCは、可変周波数や非周期信号など、デバイスがサポートする最高レートまで事実上すべてのクロック信号での変換処理が可能です。

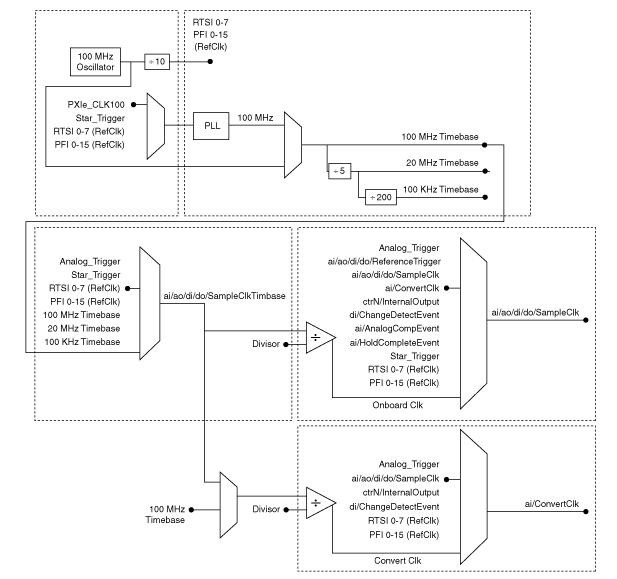

このクラスのNIデバイスは、ADCの変換ラインをさまざまなソースから駆動できる柔軟なタイミングエンジンを搭載しています。たとえば、以下のブロックダイアグラムはNI XシリーズデバイスのAIサンプリングクロックと変換クロックに供給できるさまざまなソースを示しています。

図4.NIのサンプリングクロックタイミングデバイスは、ADCの変換ラインをさまざまなソースから駆動できる柔軟なタイミングエンジンを搭載しています。

図4に表示されている主な信号は以下のとおりです。

- サンプリングクロック:この信号は、タスクに含まれるすべてのチャンネルで、一連の計測を直接的に開始します。各サンプリングクロックエッジにより、それらのチャンネルがすべて同時に変換されます。

- 変換クロック:この信号は、1つのADCが複数のチャンネルで共有されるマルチプレクスデバイスにのみ適用されます。変換クロック信号は、1つのチャンネルで1つのADC変換を開始します。集録しているチャンネル数によっては、変換クロック信号はサンプリングクロックエッジごとに1回または複数回アサートする必要があります。

- サンプリングクロックタイムベース:分周してサンプリングクロックを作成できるクロック信号です。

- 変換クロックタイムベース:分周して変換クロックを作成できるクロック信号です。

図4では、これらのデバイスでの集録タイミングが如何に柔軟に制御できるかがわかります。集録は、オンボードタイムベース (100 MHzオシレータなど)、バックプレーンクロックおよびトリガ (PXIe_Clk100、スタートリガ、RTSI<0..7>など)、他のオンボードサブシステム (たとえば、AO、DI、DO、またはカウンタ操作からAIサンプリングクロックを生成可能)、アナログコンパレータ、または外部デジタル入力 (PFIラインなど) から行うことができます。

クロックタイミングによりサンプリングされるNIデータ集録デバイスの例は、以下のとおりです。

- すべてのNI Eシリーズ、Mシリーズ、Xシリーズデバイス

- NI PXIe-4300およびPXIe-4353 SC Expressデバイス

サンプリングクロックの同期方法

これらのデバイスを同期するには、サンプリングクロック信号がすべてのデバイス間で同期している必要があります。サンプリングクロック同期にはさまざまな方法があり、いずれの方法にも長所と短所があります。

サンプリングクロックを直接共有する (サンプリングクロック同期)

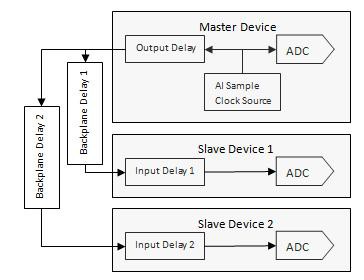

サンプリングクロック信号を同期する際の最も基本的な方法は、いずれかのデバイス (マスタデバイス) のサンプリングクロックを、他のデバイス (スレーブデバイス) へ直接ルーティングする方法です。この同期方法でスキューが生じる原因となる遅延には、いくつかの種類があります。

図5.サンプリングクロック同期は最も基本的な方法ですが、数種類の遅延が発生する可能性があります。

マスタがサンプリングクロックをバックプレーンに出力すると、出力のサンプリングクロックと内部サンプリングクロックの間に出力遅延によるわずかなスキューが生じます。その後、出力のサンプリングクロック信号は、バックプレーンのトリガライン経由でスレーブデバイスにルーティングされます。このルーティングに伴う遅延は、信号がバックプレーン上で通る経路によって決まります。サンプリングクロックがPXI_Trigラインを介してルーティングされた場合、遅延は最大80 ns程度になります。PXI_DStarライン経由の場合は、遅延ははるかに少なくなる可能性があります。スレーブデバイスでサンプリングクロックを受信すると、各デバイスの入力遅延値次第で、さらにスキューが大きくなります。

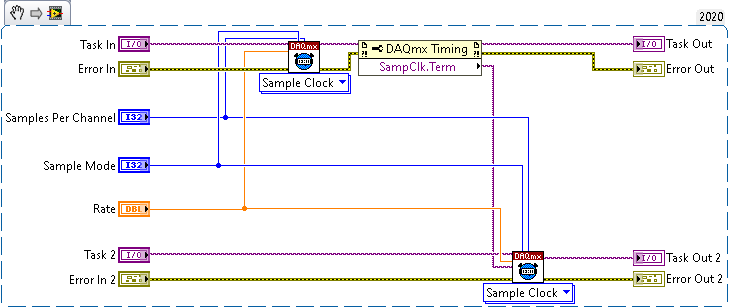

図6.マスタデバイスのサンプリングクロックを使用して複数のスレーブデバイスを同期することができます。

「端子の完全名を取得」VIのディレクトリは、<LabVIEW>\examples\DAQmx\Synchronization\SubVIs\Get Full Terminal Name.viです。また、この記事のダウンロードファイルとしても提供されています。

サンプリングクロック同期を行うには、以下の内容を実行します。

- サンプリングクロックタイミングを使用するようすべてのデバイスを構成する。

- すべてのスレーブデバイス上のサンプリングクロックのソースを、マスタデバイスからの内部サンプリングクロック端子に設定する。

| 長所 | 短所 |

|---|---|

|

|

表3.サンプリングクロック同期方法の長所と短所

共通の基準クロックからサンプリングクロックを導出する (基準クロック同期)

この方法では、すべてのデバイスに共通の基準クロックを提供します。その後、各デバイスでこの基準クロックを分周してサンプリングクロックを生成します。 基準クロック同期は、サポートされているデバイス間で最高確度の同期を実現します。

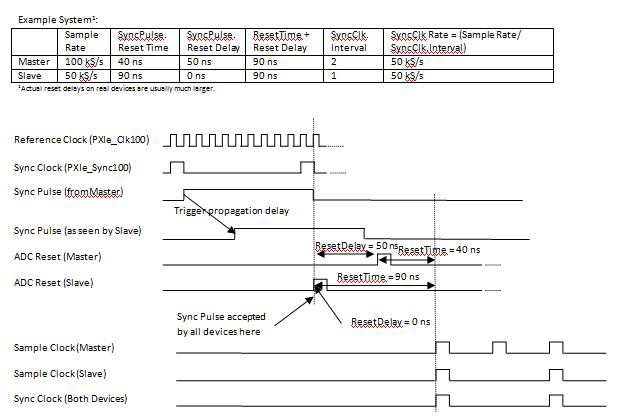

PXI Expressでは、基準クロックは通常PXIe_Clk100です。 これは、バックプレーンの各スロットで利用できるサブナノ秒単位のスキューの共通の差動100 MHzクロックです。サンプリングクロックを同期するため、サンプリングクロックの生成を開始するよう指示するトリガ信号がマスタデバイスからスレーブデバイスに送信されます。ただし、PXIe_Clk100の1周期10 ns内にマスタデバイスからスレーブデバイスまでトリガを伝搬させることは不可能です。この制約を克服するため、トリガは10 MHz (100 ns) のクロック信号より低速のPXIe_Sync100と同期して送受信されます。マスタは開始トリガ信号をPXIe_Sync100の1パルスと同期して出力します。その後、すべてのデバイスがトリガの受信後に次のPXIe_Sync100パルスで開始します。これは、NI-DAQmxヘルプではトリガのスキュー補正と呼ばれています。

図7.マスタは開始トリガ信号をPXIe_Sync100の1パルスと同期して出力します。その後、すべてのデバイスがトリガの受信後に次のPXIe_Sync100パルスで開始します。

基準クロック同期の詳細な仕組みは複雑ですが、NI-DAQmxを使用すると高度な同期テクニックも簡単に利用できるようになります。NI-DAQmxは、ユーザがマルチデバイスタスクを作成すると、サポートされているデバイス上で基準クロック同期を (トリガのスキュー補正とともに) 自動で実行します。つまり、1つのデバイスからデータを集録するのと同じシンプルさで、複数のデバイスから同期データを集録することが可能です。

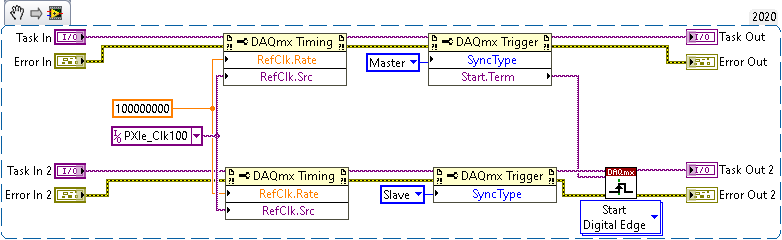

さらに、このプロセスは手作業で行うこともできます。PXIe_Clk100を両方のデバイスの基準クロックとして指定し、マスタデバイスによって生成された開始トリガを使用するようスレーブデバイスを構成します。

図8.このプロセスは手作業で行うこともできます。PXIe_Clk100を両方のデバイスの基準クロックとして指定し、マスタデバイスによって生成された開始トリガを使用するようスレーブデバイスを構成します。

| 長所 | 短所 |

|---|---|

|

|

表4.基準クロック同期は、サポートされているデバイス間で最高確度の同期を実現します。

トリガ信号のみを共有

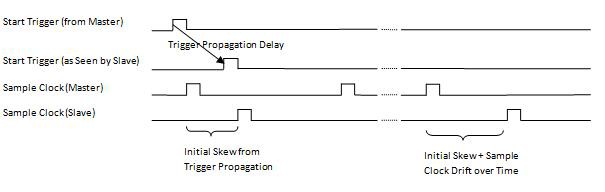

共通のサンプリングクロックや基準クロックを共有せず、トリガ信号のみを共有することで、デバイスを緩く同期させることができます。この場合、共通のトリガ信号によってすべてのデバイスがほぼ同時に開始されます。ただし、それぞれのサンプリングクロックは互いに固定されていないため、デバイスは集録中にドリフトします。

図9は、共通のトリガ信号による同期を示したものです。トリガ信号がデバイス間で伝搬する際に一定の時間がかかるため、2つのデバイスによって生成されたサンプリングクロック信号は、互いにスキューのある状態で開始されます。また、サンプリングクロックを共通の基準クロックから導出していない場合、サンプリングクロック信号は時間の経過とともにさらにドリフトしていきます。

図9.トリガ信号のみを共有することでデバイスを緩く同期させることができます。

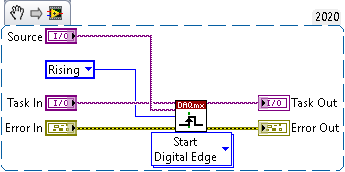

NI-DAQmxでトリガ信号を共有するには、目的のトリガ信号を「NI-DAQmxトリガ」VIへの「ソース」入力として指定します。

図10.NI-DAQmxドライバソフトウェアでトリガ信号を共有できます。

| 長所 | 短所 |

|---|---|

|

|

表5.トリガ信号のみによる同期は、短時間の集録では問題ない場合もあります。

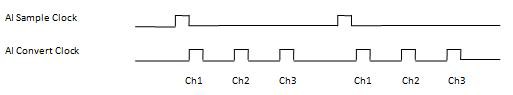

マルチプレクスデバイスで変換クロックを制御する

マルチプレクスデバイスは、1つのチャンネルから各サンプルに対してADC変換を開始するAI変換クロックを搭載しています。 たとえば、マルチプレクスデバイス上の3チャンネルで2サンプルを集録すると、図11のようなタイミングになります。

図11.AI変換クロックはマルチプレクスデバイスの各サンプルのADC変換を開始します。

一部のマルチプレクスデバイス (Eシリーズ、Mシリーズ、マルチプレクスのXシリーズなど) では、AI変換クロックのタイミングを直接制御することができます。それらのデバイスでは、AI変換クロックの制御でも、AIサンプリングクロックの制御の場合と同様の柔軟性を確保することができます。この信号のインポートまたはエクスポートを実行することも、内部または外部のタイミングソースからAI変換クロックを制御することも可能です。

他のマルチプレクスデバイス (NI PXIe-4353など) では、AI変換クロックのタイミングを直接制御することができません。それらのデバイスでは、AI変換クロック信号のインポートやエクスポートは不可能です。この信号は常に内部タイムベースによって駆動されます。ただし、それらのデバイスを使用して別のADCタイミングモードを選択することは可能です。別のタイミングモードでは、AI変換クロックのタイミングを間接的に変更できます。たとえば、高分解能タイミングモードを使用すると、AIデータの確度は向上しますが、AI変換クロックは低速化します。高速タイミングモードの場合、AI変換クロックは高速化しますが、データの確度は低下します。

AI変換クロックのタイミング制御に関する詳細な情報については、各ハードウェアのドキュメントを参照してください。

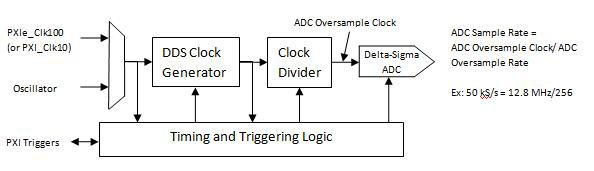

オーバーサンプリングクロックタイミングデバイス

このカテゴリのデバイスでは、自走式のオーバーサンプリングクロックを使用して、ADC変換プロセスを駆動します。このクロック信号は、ADCを動作状態に保つために、常に実行している必要があります。ADC自体は、オーバーサンプリングクロックの分周されたレートでのサンプルを生成します。このタイプのデバイスでは、通常、高速デルタシグマコンバータが使用されます。

一部のデバイス (NI PXIe-4353など) では、デルタシグマADCが使用されますが、各変換の前にADCが外部変換ラインによってリセットされるモードで使用されます。そのため、これらのデバイスはデルタシグマADCを使用しているにもかかわらず、サンプリングクロックタイミングデバイスのクラスに分類されます。

オーバーサンプリングクロックタイミングデバイスは、クロック動作の点では柔軟性が劣ります。ADCには自走式のオーバーサンプリングクロックが必要であるため、これらのデバイスをエンコーダなどの外部信号によって直接実行することはできません。また、任意のサンプリングクロック信号を受信するスレーブデバイスとして動作させることもできません。

オーバーサンプリングクロックタイミングデバイスの例は、以下のとおりです。

- すべてのダイナミック信号解析 (DSA) デバイス (NI 446x、NI 447 x、NI 449x)

- NI PXIe-433xブリッジ入力モジュール

オーバーサンプリングクロックタイミングデバイスは、基準クロックによる同期とサンプリングクロックタイムベースによる同期のどちらかを用いて、相互に同期します。

基準クロック同期

オーバーサンプリングクロックタイミングデバイスでの基準クロック同期について理解するには、これらのデバイスのタイミング/同期回路に関する知識が必要です。

これらのデバイスに使用されるデルタシグマADCには、ADC変換プロセスを駆動するための自走式オーバーサンプリングクロックが必要です。ADCは一定数のオーバーサンプリングクロック周期が経過した後、新しいサンプルを生成します。新しいサンプルを生成するのに必要となるクロック周期数が、オーバーサンプリングレートです。たとえば、オーバーサンプリングレートが256のADCは、12.8 MHzのクロックが供給された場合、50 kS/sでデータを生成します。30 kS/sでデータを集録するには、7.68 MHzのクロックを搭載したADCを使用する必要があります。

図12.オーバーサンプリングクロックタイミングデバイスの図

ユーザが自由にサンプリングレートを選べるようにするため、これらのデバイスにはアジャイルなダイレクトデジタルシンセシス (DDS) クロック発生器回路が搭載されており、広範囲のサンプリングレートで必要なADCオーバーサンプリングクロックを生成することができます。

このタイプのデバイスの基準クロック同期は、2段階で実行されます。

- ステージ1.すべてのデバイスのDDSクロック発生器、クロック分周器、ADCをリセットし、すべてのデバイスのサンプリングクロックを同期させます。

- ステージ2.すべてのデバイスのサンプリングクロックに同期した集録を開始します。

複雑な仕組みの全容を把握するには、まず、以下の点に留意するようにしてください。

- NI-DAQmxでは、ユーザがマルチデバイスタスクを作成するたびに、サポートされているデバイスで基準クロック同期を実行するために必要なすべての内容が自動で処理されます。

- 上級ユーザでこの同期プロセスを手作業で制御しようとしている場合でも、アプリケーションの開始時にはNI-DAQmxのプログラミングサンプルを利用することをお勧めします。

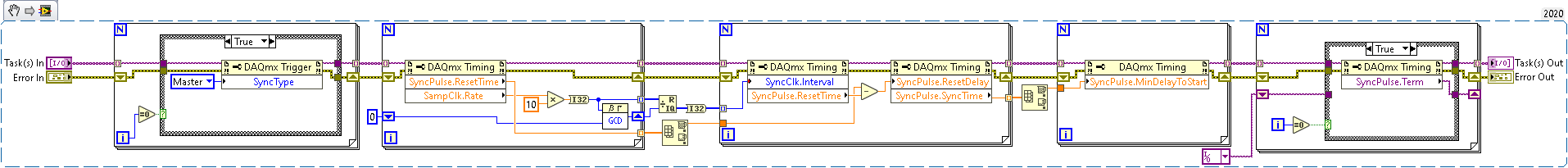

図13は、基準クロック同期のステージ1の実行の仕組みを示しています。このスキームでは、すべてのデバイスが共通の基準クロック (PXIe_CLK100) に固定されます。その後、同期パルスがPXIe_Sync100信号に同期し、マスタデバイスからすべてのスレーブデバイスに送信されます。同期パルスを受信した後、すべてのデバイスはPXIe_Sync100の次のエッジを待機します。この時点で、すべてのデバイスで、DDSクロック発生器回路とクロック分周器回路とADCをリセットするプロセスが同時に開始されます。リセットプロセスの完了にはしばらく時間がかかります。具体的な時間は、NI-DAQmxのSyncPulse.ResetTimeプロパティでレポートされます。リセット時間の異なる複数のデバイスを並べて処理するには、SyncPulse.ResetDelay値を速い方のデバイスに追加して、遅いデバイスと揃えます。これにより、すべてのデバイスのResetTime+ResetDelay値が共通化され、すべてのデバイスで最初のサンプリングクロックパルスが同時に生成されます。

さらに、SyncClk.Intervalプロパティを変更することで、異なるレートで動作するデバイスも同期させることができます。SyncClkは、デバイス間でトリガを送るために使用するクロック信号です。トリガは、1つのSyncClkエッジで送信され、次のSyncClkエッジで受信されます。SyncClkは、サンプリングクロックレートが異なるデバイスも、すべて同じレートで動作するよう設定されています。すべてのデバイスが同じレートで動作している場合、SyncClk.Interval = 1となり、SyncClkのレートはサンプリングクロックレートと同じになります。

図13.すべてのデバイスを共通の基準クロックに固定し、すべてのスレーブデバイスに同期パルスを送信します。

以下のブロックダイアグラムは、PXIe-433xのためにこれらのパラメータをNI-DAQmxでプログラミングしている例です。この例では、さらにMinDelayToStartというパラメータを設定していることにも注目してください。これは、マスタデバイスが同期パルスを送信後、集録を開始するまで、一定の時間必ず待機させるためのソフトウェア機能です。

この例は、DAQmxのすべてのバージョンで利用できるとは限らないことにご注意ください。また、使用するドライバのバージョンおよびデバイスでは、どのような機能が利用可能であるかを確認することが重要です。詳細については、次の記事を参照してください。

図14.SyncClk.Intervalプロパティを変更することで、異なるレートで動作するデバイスも同期することができます。

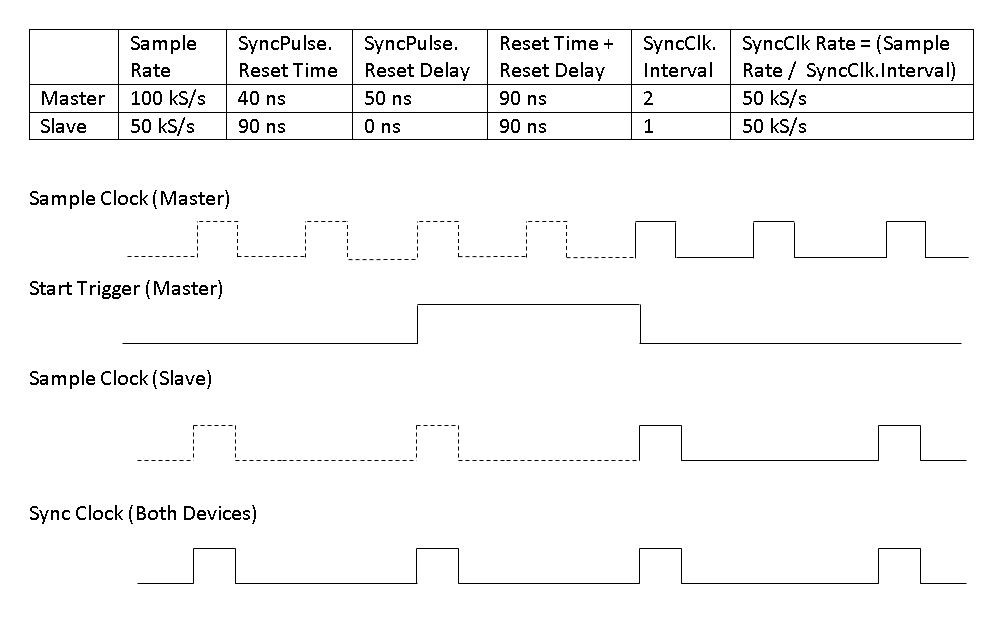

これでステージ1 (サンプリングクロック同期) は完了です。ステージ2 (集録の開始) では、すべてのデバイスの同期クロックに同期した開始トリガを送信するのみです。

ステージ2では、まずマスタが開始トリガを送信します。この開始トリガは、すべてのデバイスに事前に同期されている同期クロックと同期して出力されます。すべてのデバイスが開始トリガを受信した後、次の内部同期クロックを待機します。この時点で、すべてのデバイスが原則として同時にサンプリングクロックの生成を開始します。マスタデバイスとスレーブデバイスの両方の内部に、バックグラウンドで動作するサンプリングクロックがあります。このサンプリングクロックに関連づけられたデータは (このサンプリングクロック信号は他のデバイスには出力されません)、開始トリガイベントが発生するまで集録されません。波形では、開始トリガの発生前のサンプリングクロック信号が破線で示されています。

図15.マスタが開始トリガを送信すると、すべてのデバイスが同時にサンプリングクロックを開始します。

サンプリングクロック同期

サンプリングクロックタイムベースによる同期は、旧型のPCIデバイスおよびPXI DSAデバイス (NI 446xやNI 447xなどのデバイス) で使用されます。PXI Expressをベースとする、より新しいデバイスでは、基準クロック同期がサポートされます。サンプリングクロックタイムベースによる同期の詳細については、「NI-DAQmxヘルプ」または「DSAユーザマニュアル」を参照してください。

サンプリングクロックタイミングデバイスおよびオーバーサンプリングクロックタイミングデバイスの間で同期を行う

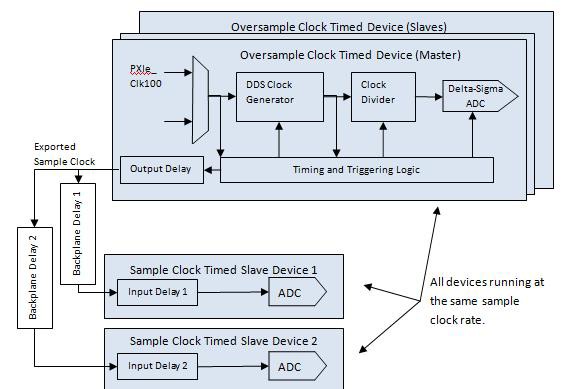

セルフタイミングデバイスからサンプリングクロックをエクスポート

この方法では、オーバーサンプリングクロックタイミングデバイスからサンプリングクロック信号をエクスポートする作業を行います。このスキームでは、複数のオーバーサンプリングクロックタイミングデバイスを使用している場合でも、すべて基準クロック同期によって同期されます。サンプリングクロックタイミングデバイスを同期するには、オーバーサンプリングクロックタイミングデバイスからPXI Expressバックプレーン経由でサンプリングクロック信号をサンプリングクロックタイミングデバイスにエクスポートします。この際、サンプリングクロックタイミングデバイスでは、前述のサンプリングクロック同期方法が用いられます。

図16.PXIe_Clk100信号の基準クロック同期を利用して、複数のオーバーサンプリングクロックタイミングデバイスが緊密に同期しています。

このサンプルシステムでは、PXIe_Clk100信号の基準クロック同期を利用して、複数のオーバーサンプリングクロックタイミングデバイスが緊密に同期しています。次にこれらのデバイスのいずれかでサンプリングクロックが生成され、PXI Expressバックプレーンのトリガライン経由で1つまたは複数のサンプリングクロックタイミングスレーブデバイスにルーティングされます。スレーブ間のスキューの量は、バックプレーンルーティング遅延のスキューによって決まります。

このサンプリングクロックをサンプリングクロックタイミングスレーブデバイスにルーティングするために必要なNI-DAQmxコードは、上記のサンプリングクロック同期コードとまったく同じです。

図17.上流のタスクにはサンプリングクロックを生成するオーバーサンプリングクロックタイミングマスタデバイス、下流のタスクにはこのサンプリングクロックを受け取るサンプリングクロックタイミングスレーブデバイスが含まれます。

「端子の完全名を取得」VIのディレクトリは、<LabVIEW>\examples\DAQmx\Synchronization\SubVIs\Get Full Terminal Name.viです。また、この記事のダウンロードファイルとしても提供されています。

この場合、上流のタスクにはサンプリングクロックを生成するオーバーサンプリングクロックタイミングマスタデバイス、下流のタスクにはこのサンプリングクロックを受け取るサンプリングクロックタイミングスレーブデバイスが含まれます。

| 長所 | 短所 |

|---|---|

|

|

表6.この方法ではさまざまな種類のデバイス間での同期が可能です。

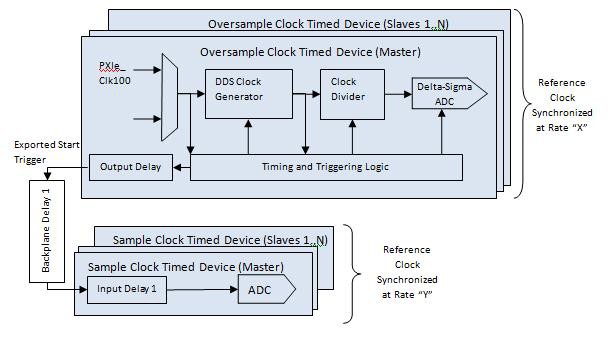

サンプリングクロックタイミングデバイスとオーバーサンプリングクロックタイミングデバイスでトリガを共有

この同じテクニックを使用して、オーバーサンプリングクロックタイミングデバイスとサンプリングクロックタイミングデバイスを前述のように同期することができます。 このテクニックを使用すると、デバイスをサンプリングクロックタイミングとオーバーサンプリングクロックタイミングの2つのグループに分けることができるというメリットがあります。各グループで基準クロック同期を使用して、グループ内での緊密な同期を達成することができます。また、トリガ信号を2つのグループ間で共有して、ほぼ同時に開始することも可能です。

図18.サンプリングクロックタイミンググループとオーバーサンプリングクロックタイミンググループの範囲では、基準クロック同期を使用できます。

トリガ信号がバックプレーン間で伝搬する時間や、受信側のデバイスが再同期してトリガ信号を受け入れる時間が必要なため、2つのグループ間で多少のスキューが見られることがわかります。ただし、各グループ内では、基準クロック同期により、スキューは事実上ゼロとなっています。トリガ信号のみを共有しているため (サンプリングクロックを直接共有していない)、各グループは異なるレートで実行できるようになっている点にもご注意ください。

| 長所 | 短所 |

|---|---|

|

|

表7.この方法ではサンプリングクロックタイミングデバイスをオーバーサンプリングクロックタイミングデバイスと異なるレートで実行できます (より高速になる可能性があります)。

トリガ信号の同期に関する注意点

注意1:トリガのスキュー

トリガ信号を使って同期を行う際に、考慮すべき重要な点がいくつかあります。まず、トリガ信号が送信先デバイスへ伝搬するのに時間がかかることにより、デバイス間にスキューが生じます。さらに、このトリガ信号はスレーブデバイスによって集録クロックと同期する必要があります。これにより、かなりのスキューが生じる可能性があります。図19の波形はこのスキューを示しています (複数のサンプリングクロックタイミングデバイスが複数のオーバーサンプリングクロックタイミングデバイスから開始トリガを受信していると仮定)。

図19.スキューを最小限に抑えるには、トリガ信号を集録クロックに同期させる必要があります。

サンプリングクロックタイミングのマスタデバイスは、トリガを受信すると、このトリガを同期クロックに再同期させ、すべてのサンプリングクロックタイミングのスレーブデバイスに転送する必要があります。これが前述のトリガスキュー補正プロセスです。その結果、2組のデバイスのサンプリングクロックで1~2周期の同期クロック分のスキューが生じています。この例では、同期クロックとしてPXIe_Sync100信号を使用しています。PXIe_Sync100は100 ns周期であるため、2組のデバイスのサンプリングクロックでは100~200 nsのスキューが生じています。

ここで、このプロセスをもう一度行い、その際にサンプリングクロックタイミングデバイスからオーバーサンプリングクロックタイミングデバイスへ開始トリガを送信した場合、さらにスキューが大きくなります。これは、オーバーサンプリングクロックタイミングデバイスで自走式のサンプリングクロックがバックグラウンドで実行されていることが原因です。トリガ信号に即座に応答することは不可能であるため、次のサンプリングクロックを待機する必要があります。この場合、図19に示されている同期クロックがオーバーサンプリングクロックタイミングデバイス内部のサンプリングクロック信号となります。これにより、2つのデバイスグループ間でサンプリングクロック1~2周期分のスキューが生じます。これははるかに大きな誤差の原因となります。

どちらの場合も、カウンタを使って各デバイスグループからエクスポートされたサンプリングクロック信号の間で2エッジ分離計測を実行することで、このスキューの実際の値を計測することが可能な場合があります。

注意2:DDSクロックドリフト

直観的には、サンプリングクロックタイミングデバイスとオーバーサンプリングクロックタイミングデバイスがどちらも同一の基準クロック (PXIe_Clk100) に固定されている場合、2組のデバイス間のドリフトはゼロになります。場合によっては、特定のレートで、デバイス間のドリフトが完全にゼロになることもありえます。

ただし、常にそうなるわけではありません。DDSは通常、デバイスで使用するデルタシグマADC用のオーバーサンプリングクロックを生成するため、PXIe_Clk100信号の分周方法を制御する32ビットチューニングワードでプログラムします。チューニングワードを計算する際、わずかな丸め誤差が生じ、このチューニングワードを理想値より≤0.5ビット高くまたは低く設定する必要に迫られる場合もあります。それにより、オーバーサンプリングクロックタイミングデバイスとサンプリングクロックタイミングデバイスの間で、サンプリングクロックレートに極めて小さな誤差が生じることがあります。この誤差は≤~0.1 ppb (0.5/2^32) です。これは長時間の集録では問題になることもありますが、短時間の集録では認識できないほどのレベルです。たとえば、100 kS/sの場合、このレベルの誤差のある2回の集録が1サンプル (10 μs) 分ドリフトするのに、約1日かかります。

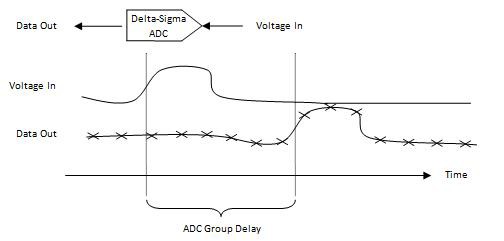

デジタルフィルタの群遅延

オーバーサンプリングクロックタイミングデバイスを使用する際のもう1つの注意点は、これらのデバイスに関連するデジタルフィルタの群遅延です。オーバーサンプリングクロックタイミングデバイスのデルタシグマADCは、入力信号をある周期にわたってオーバーサンプリングし、フィルタリングすることによって動作します。このプロセスによって、入力信号がADC入力ピンで有効になってから最終的なデジタル化されたサンプルが利用可能になるまで、多くのサンプル分の時間に相当する長い遅延が生じます。

ただし、新しいPXI Expressデバイスでは、群遅延補正技術が採用されているため、ほとんどの場合、エンドユーザが群遅延を認識することはありません。

図20.群遅延とは、ADCの入力で入力イベントが発生してからその相当するデータがADCから出力されるまでの時間のことです。

群遅延により、ADCの入力で入力イベントが発生してからその相当するデータがADCから出力されるまでに時間差が生じます。言い換えると、ある時点でADCから返されたデータは、過去のある時点でのADC入力における電圧を示しているということになります。

群遅延を正しく補正しない場合、群遅延が異なる各デバイスから返されたデータにスキューが発生します。また、群遅延により、そのようなタイプのADCから返されるデータを外部イベントと相関させるのがさらに難しくなります。

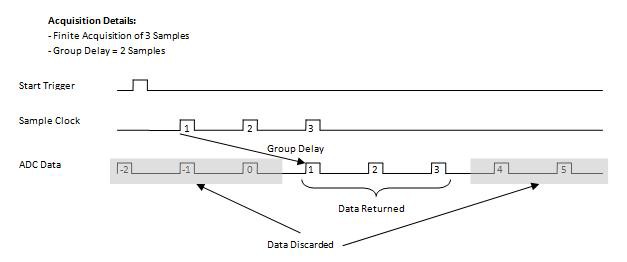

群遅延補正

群遅延補正機能を搭載したデバイスを使用すると、モジュール間の同期と外部イベントに基づくデータの相関のプロセスが簡素化されます。群遅延補正は以下のようなメカニズムで動作します。

- デバイスからのサンプリングクロック出力は、ADCの入力ピンで入力信号が有効になった時点で生成されます。このサンプリングクロックが別のデバイスと共有されると、これら2つのデバイスからのデータは、内部の群遅延に関わらず、時間的に近接します。

- これらのデバイスによって生成または受信されたトリガは、生成されたサンプリングクロックとの関係に基づいて解釈されます。たとえば、集録を開始する開始トリガが発行されると、すぐ次のサンプリングクロックからのデータが集録の開始ポイントとして返されます。

- ソフトウェアタイミングによるオンデマンド集録の場合、これらのデバイスはADCからサンプルを返す前に、群遅延の時間が経過するのを待機します。そのため、データが返される時間とソフトウェアがデータを要求した時間は近接します。

図21.新しいPXI Expressデバイスでは、群遅延補正技術が採用されているため、ほとんどの場合、エンドユーザが群遅延を認識することはありません。

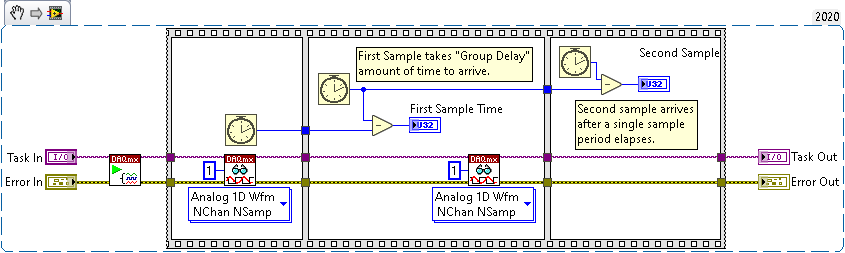

この集録は、ソフトウェアまたはハードウェアからの開始トリガによって始まります。開始トリガを受信した後、デバイスでは、できる限り早急にサンプリングクロックを生成します。ADCはすでにバックグラウンドで実行しているため、開始トリガを再同期してオンボード変換と揃える必要があります。このプロセスを行うことで、開始トリガが受信されてから最初のサンプリングクロックが出力されるまでにサンプリングクロック0~2周期分の遅延が発生します。

サンプリングクロックの生成が始まると、その集録に必要なポイント数に応じて続行されます (この例では3)。デバイスでは、内部的に、ADCからデータを集録するのに使用する遅延クロック信号が作成されます。この遅延値は群遅延に相当するため、最終的にADCから返されるデータはサンプリングクロックエッジが発生した時間と正確に一致します。

群遅延補正は、自動で実行され、ユーザはプログラムで特別な手順を実行する必要がない点にご注目ください。

群遅延補正デバイスのサポート

NI-DAQmx 9.1では、NI PXIe-433xブリッジ入力デバイスで群遅延補正がサポートされます。 NI PXIe-433xとPXIe-449xの両方の16チャンネルDSAモジュールを含むマルチデバイスタスクを作成する場合、NI-DAQmxは群遅延補正を自動で両デバイスに適用します。ただし、単独で使用した場合は、NI PXIe-449xは群遅延補正を実装しません。

群遅延補正の注意点

注意1:レイテンシ

群遅延補正は、目的の出力データが利用可能になるまで待機してから行われるため、デバイスからのデータの読み取りに伴う遅延時間が発生します。

図22.群遅延補正は、目的の出力データが利用可能になるまで待機してから行われるため、デバイスからのデータの読み取りに伴う遅延時間が発生します。

この例では、集録を開始して、次に最初のサンプルが利用可能になるまでに経過した時間を計測します。この遅延は、このサンプルレートでのデバイスの群遅延と同じです。デバイスから最初のサンプルを取り出した後、次のサンプルが利用可能になるのはサンプリングクロック1周期分の時間が経過した後になります。この例では、ソフトウェア遅延のほか、計測に使用しているソフトウェアタイマの確度については考慮していません。

注意2:アナログトリガ

これらのデバイスには、ADCから返されるデジタル化されたデータに基づいた「アナログ」トリガを実装するオンボードロジックも搭載されています。このアナログトリガを動作させ、同時にデバイスの群遅延を正しく補正できるようにするには、最小限のプレトリガポイントおよびポストトリガポイントを集録する必要があります。

ユーザはこのプロセスの仕組みを正確に理解する必要はありません。プレトリガサンプルとポストトリガサンプルを無効な組み合わせで指定すると、NI-DAQmxでは、指定したサンプル数を調整する方法を具体的に示すエラーメッセージが表示されます。

SC Expressによる柔軟な同期

SC Expressモジュールは、PXIプラットフォームとDAQmxドライバソフトウェアを利用して、ハードウェア同期のさまざまなオプションを提供するものです。 使用するデバイスと求めるパフォーマンスレベルによって、サンプリングクロックタイミングと基準クロックタイミングのどちらかを選ぶことができます。 これらの同期方法はカスタマイズ性に優れていますが、NIではマルチデバイスタスクを使用してモジュールを自動で同期するオプションをご用意しています。 SC Expressモジュールを使用すると、ハードウェアの緊密な同期とアプリケーション特有のニーズに合わせたカスタマイズが可能となります。