ダイレクトデジタルシンセシス (DDS) を理解する

概要

ダイレクトデジタルシンセシスの基礎と理論、およびそれを関数発生器と任意関数発生器に適用する方法を学びます。

内容

概要

「信号の生成」ホワイトペーパーでは、関数発生器や任意関数発生器 (AFG) などの信号発生器が必要なアナログ信号を出力する方法、および一部の信号発生器がダイレクトデジタルシンセシス (DDS) テクノロジを使用して正確な周波数で信号を出力する方法について説明しています。この記事では、信号生成においてサブヘルツ確度を達成する信号ソースのコンポーネントとテクノロジについて説明します。

動作理論

DDSを使用する信号発生器は、波形が保存された順序で各サンプルを出力する従来の方法とは異なり、独自のメモリアクセスおよびクロックメカニズムを使用して正確な周波数で信号を生成します。任意波形発生器 (AWG) は、従来の信号生成方法を使用します。AWGは、複雑なユーザ定義波形を生成できますが、波形生成時の周波数精度に限界があります。これは、波形がAWGのメモリからポイントごとに生成する必要があるのと、生成された各ポイント間の時間を制御するサンプリングクロックの周波数の数が有限であるためです。

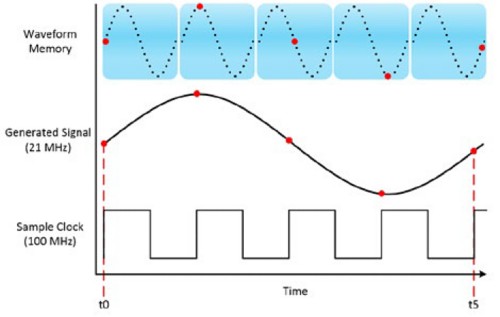

DDSを使用する関数発生器およびAFGは、周期波形の1サイクルに対して大量のポイントをメモリに保存します。DDSテクノロジは、関数発生器またはAFGがメモリから出力するサンプルを選択する機能を提供します。関数発生器またはAFGは、波形の次のサンプルを選択する際に制限がないため、正確な周波数で信号を生成できます。図1は、関数発生器またはAFGが100 MHzサンプリングクロックの整数除算ではない21 MHzの正弦波を生成する方法を示しています。100 MHzサンプリングクロックは、DAC出力のアップデートレートを駆動します。したがって、サンプリングクロックが高速であるほど、生成される信号の形状はより正確になります。

図1:DDS対応ハードウェアでは、サンプルは必ずしもメモリに格納された順序で選択されるとは限らない。これにより、100 MHzのサンプリングクロックで21 MHzの正弦波を正確に生成できる。

上記の特定のケースでは、AFGは100 MHzサンプリングクロックを使用してDACを駆動しますが、生成される信号の周波数は、波形メモリの場所からサンプルが選択される方法によって作成されます。次のセクションでは、サンプル選択の背後にある制御論理を実装するコンポーネントについて説明します。

機能の概要

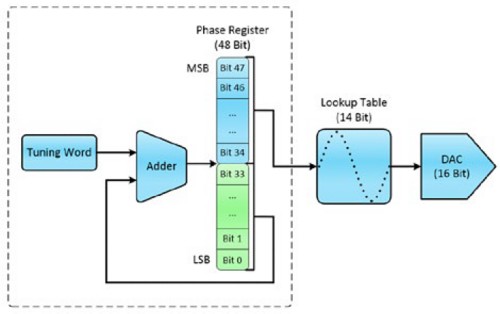

DDSの実装には、(a) サンプリングクロック、(b) 位相アキュムレータ、(c) ルックアップテーブル (プログラム可能な読み取り専用メモリの実装) の3つの主要なハードウェアビルディングブロックが必要です。図2は、ハードウェアブロックからハードウェアブロックへの上位レベルのフローを示します。

図2:DDSアーキテクチャのハードウェアブロック図

a.サンプリングクロック

サンプルクロックまたは基準クロックは、周波数チューニングワードの作成、位相アキュムレータ値の更新、デジタル/アナログ変換の駆動に使用されます。サンプリングクロックは、DACがサンプルを出力するタイミングを決定しますが、出力信号の周波数を直接決定するものではありません。

b.位相アキュムレータ

位相アキュムレータは、関数発生器またはAFGが正確な周波数で出力できるようにするコンポーネントの集合です。正確な周波数で信号を作成するために、位相アキュムレータは3つの一般的なコンポーネントを使用します。最初に、位相アキュムレータはチューニングワードを使用して信号の周波数を指定します。チューニングワードは、波形メモリでジャンプするサンプル数を指定する24~48ビットのデジタルワードです。2番目のコンポーネントである加算器は、チューニングワードを受け取り、それを位相レジスタの余りと合計します。この新しいデジタル値は位相レジスタに出力されます。位相アキュムレータの最後のコンポーネントである位相レジスタは、新しいデジタルワードを受け取り、それを使用してルックアップテーブルに出力される次のサンプルポイントのメモリアドレスを指定します。位相レジスタは、ルックアップテーブルメモリアドレスで使用されていない残りの最上位ビットを受け取り、それらを加算器に戻して、長期の周波数の精度を確保します。

c. ルックアップテーブル

位相レジスタの出力は、メモリアドレスが時間の経過とともに増加し、チューニングワードで指定されたレートで変化するため、デジタルランプのように見えます。したがって、必要な波形を出力するには、位相レジスタの出力がルックアップテーブル内の必要な波形サンプルアドレスを指します。次に、ルックアップテーブルは、指定されたメモリアドレスのデジタルワードを提供します。これは、DACが生成する正しい振幅と位相のデジタルワードです。

周波数可変能力、つまり波形の周波数を高速かつ位相連続的に変更できる機能は、DDSアーキテクチャの主な利点の1つです。DDSを使ったAFGは、波形の周波数を変えるためにチューニングワードを変えるだけでよいので、波形の周波数を非常に高速に変えることができます。

一般的な用途

前述のように、DDSテクノロジには大きく2つの利点があります。DDSテクノロジの主な利点の1つは、生成された信号の周波数確度です。この機能により、関数発生器またはAFGで作成された信号の周波数確度を信頼できるため、非常に正確なコンポーネントテストが可能になります。

DDSテクノロジの2番目の利点は、生成された信号の周波数を非常に高速かつ位相連続的に変更できることです。これにより、周波数変更を迅速に実装できるため、特定の範囲でより効率的なコンポーネントテストが可能になります。また、検査対象デバイスに提供する信号を制限することで、デバイスにストレステストを行うこともできます。

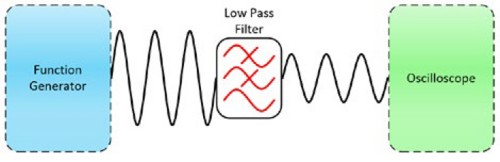

DDSテクノロジを使用したAFGが非常に役立つ例として、フィルタの正確な特性評価があります。フィルタに供給される信号がAFGによって正確に生成され、フィルタ処理された信号がオシロスコープで正確に測定された場合にのみ、フィルタの特性評価が正確になります。図3は、フィルタ特性評価の標準的なテスト設定を示します。

図3:DDS対応関数発生器、ローパスフィルタ、オシロスコープを使用したフィルタ特性評価アプリケーションのブロック図

まとめ

- DDSテクノロジを使用しない信号発生器は、保存された波形をサンプリングクロックの周波数でポイントごとに出力することで波形を生成します。

- DDSテクノロジを使用した信号発生器は、非常に高い周波数確度で多くの周波数で周期波形を生成できます。これは、独自のメモリアクセスとクロック機能メカニズムによるものです。

- DDSテクノロジは、サンプリングクロック、位相アキュムレータ、ルックアップテーブルの3つの上位レベルハードウェアブロックで実装されています。

- サンプリングクロックは、周波数チューニングワードを作成し、位相アキュムレータ値を更新し、DAC出力レートを駆動します。

- 位相アキュムレータは、周波数チューニングワードを入力として受け取り、ルックアップテーブルに出力される次のサンプルのデジタルメモリアドレスを提供します。

- ルックアップテーブルは、周期波形をデジタルサンプルとして保存します。ルックアップテーブルは、位相アキュムレータからメモリアドレスを受け取り、そのメモリアドレスのデジタル波形サンプルをDACに提供します。

- DDSテクノロジを使用した信号発生器は、正確な周波数生成または周波数可変能力を必要とするアプリケーションに使用する必要があります。

- 非常に大規模で複雑なユーザ定義の波形を必要とするアプリケーションでは、DDSテクノロジを使用した任意関数発生器ではなく、任意波形発生器を使用するのが最適な場合があります。