PXIe-4081 7½桁FlexDMMアーキテクチャについて

内容

- 概要

- 従来のDMMにおける制限

- NIのFlexDMMテクノロジ

- 低ノイズで安定性に優れたフロントエンドアーキテクチャ

- セルフキャリブレーション

- 電圧計測アーキテクチャ

- 電流計測アーキテクチャ

- 1.8 MS/s絶縁デジタイザアーキテクチャ

- 抵抗計測アーキテクチャ

- まとめ

概要

NIは2002年に最初のPXI FlexDMMを発売しました。この製品は、エンジニアに対して、従来の精密機器に固有の測定の課題、つまり測定スループットと柔軟性の制限へのソリューションを提供するものでした。FlexDMMは、数千ドルもより高価な高分解能デジタルマルチメータ (DMM) に匹敵する計測スループットを実現することにより、こうした問題の克服に貢献しました。NIはこの製品の発表以来、FlexDMMアーキテクチャの技術革新を次のような点で継続して推進してきました。

- 最速計測モードのスループットを2倍に向上

- 1.8 MS/sの絶縁高電圧デジタイザモードの追加

- PXI-4070のPCIバージョンの発表

- PXIe-4082 6½桁FlexDMMおよびLCRメータの発表

最新版はNI PXIe-4081 7½桁FlexDMMとなります。PXIe-4081 FlexDMMは、26ビットの確度と分解能を備え、それまでのFlexDMMデバイスと比較して、性能面で分解能は10倍、確度は最大60%向上しています。PXIe-4081は、表1に示すように、極めて幅広い計測範囲をカバーします。これにより、周波数/周期およびダイオード計測のほか、±10 nV~1000 Vの範囲のDC電圧、±1 pA~3 Aの範囲の電流、および10 µΩ~5 GΩの範囲の抵抗の計測が可能です。FlexDMMの絶縁デジタイザモードでは、すべての電圧および電流モードにおいて、最高1.8 MS/sのサンプルレートでDCカプリングされた波形を集録することができます。このドキュメントでは、FlexDMMと従来のDMMアナログ/デジタルコンバータ (ADC) およびそれらのアーキテクチャを詳細に比較します。

PXIe-4081

| PXIe-4080/4082

| |

| 最大分解能 | 7½桁 (26 ビット)

| 7½桁 (23 ビット)

|

| 電圧範囲 | ||

| 最大DC | 1000 V

| 300 V

|

| DC感度 | 10 nV

| 100 nV

|

| 最大AC rms (ピーク) | 700 Vrms (1000 V)

| 300 Vrms (425 V)

|

| コモンモード電圧 | 500 V

| 300 V

|

| 電流範囲 | ||

| 最大DC | 3 A

| 1 A

|

| DC感度 | 1 pA

| 10 nA

|

| 最大AC rms (ピーク) | 3 A (4.2 A)

| 1 A (2 A)

|

| AC rms感度 | 100 pA

| 10 nA

|

| 抵抗範囲 | ||

| 最大 | 5 GΩ

| 100 MΩ

|

| 感度 | 10 µΩ

| 100 µΩ

|

| LCR範囲1 | ||

| キャパシタンス | N/A

| 0.05 pF~10,000 µF

|

| インダクタンス | N/A

| 1 nH~5 H

|

| 料金 | 3,690米ドル

| 2,406/3,209米ドル

|

表1. FlexDMM入力比較

1 PXIe-4082のみ。 インダクタンスとキャパシタンスを測定する他のオプションとして、PXI LCRメータをご検討ください。

従来のDMMにおける制限

従来のDMMは一般的に分解能と確度を重視し、高速集録機能も備えていません。当然ながら、基本的な物理学の関数である、速度に対するノイズ性能にはいくつかの固有の制限があります。抵抗の熱雑音 (ジョンソン-ナイキスト雑音) は理論的限界の一例で、半導体デバイステクノロジでは実用上の限界を設けています。しかし、可能な限り最高の計測性能を実現するには、その他にさまざまな選択肢があります。

一部の特別な高分解能DMMは分解能が高く若干速度が高いことが特長ですが、その分非常に高価で8,000米ドル近くになります。また、フルラック構成での購入が条件となるため、システムスペースまたはベンチスペースを大きく占有していまいます。

DMMのもう1つの速度制限は、従来のハードウェアプラットフォームであるGPIB (IEEE 488) インターフェースバスに起因するものです。1970年代から使用されているこのインタフェースは、速度、柔軟性、コストのトレードオフにもかかわらず、多くの場合に標準と見なされています。ほとんどの従来の「箱型」DMMは、現在オプションとしてUSBやEthernetといった他のインタフェース規格を使用できるにも関わらず、このインタフェースを使用しています。これらすべてのインタフェースは、DMMとの接続に際して計測器にメッセージを送信して応答を待つという方法を採用していますが、これでは本質的に、PXIモジュール式計測器に採用されているレジスタベースのアクセスによる接続より遅くなります。

最初の試みとしてGPIBインタフェースの使用をやめても、DMMの速度と確度の両方での基本的な制限は、こうした製品にADCを使用している限り解消されません。採用するテクノロジについてより深く理解するには、性能の観点からどのようなメリットがあるのかさらに詳しく検討する必要があります。

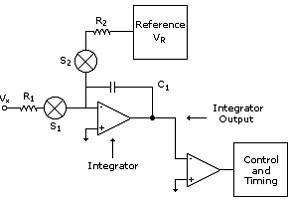

デュアルスロープADCテクノロジ

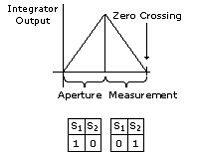

歴史的観点から、最も古いながらも最も一般的な高確度A/D変換形式はデュアルスロープADCです。このテクニックは1950年代以降、広く使用されてきました。これは基本的に2ステップからなるプロセスです。まず、入力電圧 (計測対象の信号を表す) は電流に変換され、スイッチS1を通して積分器の入力に渡されます。積分器を積分サイクルまたはアパーチャの開始時に入力に接続すると、積分器は積分サイクルまたはアパーチャの終了時まで増加し続け、その終了時点で積分器からの入力接続が切断されます。今度は高確度の既知の基準電流をスイッチS2から積分器に接続すると、積分器はゼロを超えるまで減少し続けます。この間に高分解能カウンタは、積分器が開始点からランプダウンするまでに要した時間を計測します。積分時間と基準電流に関連したこのような計測時間は入力信号の振幅に比例します。図1をご覧ください。

図1. デュアルスロープコンバータのブロック図

このテクニックは現在、多くの高分解能DMMで採用されています。利点はその簡明さと優れた確度にあります。積分時間を長くすると、理論的限界までは分解能を高くすることができます。ただし、次の設計上の制限により最終的な製品の性能は影響を受けます。

- 積分コンデンサの誘電体吸収を補正する必要があります。これは、高品質な積分コンデンサでも例外ではなく、複雑なキャリブレーションが必要になる場合もあります。

- ゲートで信号のオン/オフ状態を制御する必要があり、基準電流も同様です。このプロセスでは、入力信号に対して電荷注入が発生する可能性があります。電荷注入は入力依存のエラー (非線形) の原因になり、非常に高い分解能 (6½桁以上) では補正が困難です。

- ランプダウン時間により、計測速度が大きく低下します。ランプダウンが速いと、コンパレータ遅延や電荷注入などを原因とするエラーが大きくなります。

あるトポロジでは、積分器の前にトランスコンダクタンスを使用して電圧を電流に変換し、その後「電流ステアリング」ネットワークを使用して電荷注入を最小化しています。残念ながら、こうしたステップの追加により複雑性が増し、エラーも大きくなります。

こうした設計上の制限があるにもかかわらず、デュアルスロープコンバータは、最も一般的なベンチやフィールドサービスツールとしての用途から、高確度かつ高分解能を持つ高精度計測用のDMMにいたるまで、あらゆるDMMで使用されてきました。ほとんどの積分型A/Dテクニックとの併用で、デュアルスロープコンバータにはかなり優れたノイズ除去を発揮できるメリットがあります。積分周期を複数の1/PLC (電源周波数) に設定すると、A/Dが電源周波数ノイズを除去するという望ましい結果が得られます。

ランプダウン・チャージバランスADCテクノロジ

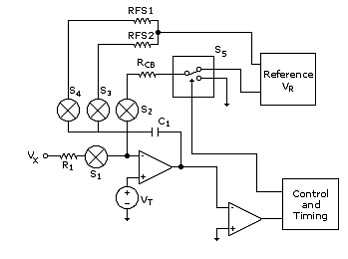

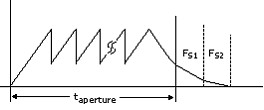

多くのメーカーは、デュアルスロープコンバータに特有の誘電体吸収と速度問題の解決に、ランプダウン・チャージバランスA/Dテクニックを使用しています。このテクニックは本質的にデュアルスロープに似てますが、積分サイクル中に量子化された増分ごとに基準信号を加える点が異なります。これは「変調」と呼ばれることもあります。 各増分は、最終カウントの固定数字を表します。図2をご覧ください。

図2. チャージバランスコンバータのブロック図

図2でtapertureと示されたこの積分の段階では、S1がオン状態になり、VxがR1を通して供給され、積分が開始されます。反対からの電流が一定の間隔で、スイッチS2およびS3を通して供給されます。これによってC1の電荷の平衡 (チャージバランス) が保たれます。S5がVRに接続されるたびに計測カウントが生成されます。実際、高い分解能の計測 (長い積分時間) の場合、カウントのほとんどはこのtaperture段階に生成されます。このチャージバランスの最後に、高確度の基準電流が積分器に供給されます。これはデュアルスロープコンバータの場合と同様です。このようにして積分器はゼロを超えるまでランプダウンします。積分の間に蓄積されたカウントから計測値が算出され、ランプダウン時に蓄積されたカウントに追加されます。メーカーは、2つ以上のランプダウン基準を使用します。最初はスピードが速くなるように減少を速くし、「最終スロープ」では速度が落ちて確度が向上します。

このランプダウン・チャージバランスA/Dは、積分コンデンサの誘電体吸収の問題を大きく改善する一方で、デュアルスロープコンバータと同様の性能メリットも提供します。(実際、デュアルスロープコンバータの中には複数のランプダウンスロープを使用するものがあります。) 速度が大きく改善されるのは、チャージバランス時に生成されるカウント数がランプダウンエラーを軽減して、ランプダウンがかなり速くなるためです。しかし、複数の計測を行う場合や信号をデジタル化する場合、積分の有効化や無効化を行うため、依然として大幅なデッドタイムが発生します。

このタイプのADCは1970年代から商用利用されて、大きく発展してきました。初期のタイプでは、電圧-周波数コンバータと同様の変調器が使用されました。周波数依存の寄生要素に起因する線形性の問題があったため、このタイプは変換速度が制限されていました。1980年代半ばにはテクニックが洗練され、現在でも広く使用されている「一定周波数」変調器が統合されるに至りました。これにより、このコンバータの最終的な性能と製造性の両方が劇的に向上しました。

シグマデルタコンバータテクノロジ

シグマデルタコンバータ、つまりノイズシェーピングADCは、電気通信にルーツがあります。このテクニックは現在、複数のメーカーが製造する市販の既製A/D構築ブロックの基盤として広く使用されています。この分野では過去10年間に大きな進展があり (音響/電気通信における高ダイナミックレンジでの変換ニーズが高まりによる)、現在でも多くの研究が行われています。現在でも一部のモジュール式DMM (PXI(e)、PCI(e)、VXI) の集録エンジンの心臓部には、シグマデルタADCが使用されています。このテクノロジはまた、次のようなケースのデジタル変換に広く利用されています。

- ダイナミック信号解析 (DSA)

- 商用および消費者向け音響/音声

- 振動、歪み、温度などの物理的現象 (適度な帯域幅のA/D変換で十分な分野)

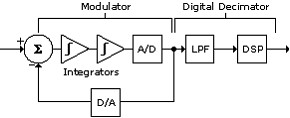

シグマデルタコンバータの基本図を図3に示します。

図3. シグマデルタコンバータのブロック図

シグマデルタコンバータの基本要素は、積分器または複数の積分器、1ビットADCおよびDAC (デジタル/アナログコンバータ)、およびデジタルフィルタです。ノイズシェーピングを行うには、積分ステージとデジタルフィルタ設計を組み合わせます。これを実装するテクニックは数多くあります。積分器の最適な数、デジタルフィルタの数、A/DおよびD/Aコンバータのビット数などに関しては異なる説が存在しています。ただし、機能を実現する基本的な要素は変わりません。1ビットのチャージバランス・フィードバックループで構成された変調器は、上述したものと類似しています。1ビットADCは、元々持っている優れた確度と単調性によって、非常に優れた線形性を実現します。

市販のシグマデルタコンバータには多くのメリットがあります。

- 優れた線形性と優れた差動型非線形性 (DNL) を示す。

- 信号ノイズを非常に効率よく制御できる。

- 本質的にセルフサンプリングとトラッキングが可能 (サンプルホールド回路は不要)。

- 一般的に低コスト。

ただし、高分解能DMMで市販のシグマデルタADCを使用するにはいくつかの制限があります。

- デジタルフィルタによるパイプライン遅延に起因する速度制限。特に複数チャンネルをスキャンする場合に発生する。

- 一般的に線形性と低ノイズを特長とするが、確度はメーカーの仕様では5½桁 (19ビット) に制限される。

- 変調の「トーン」は通過域にエイリアスを発生させるため、高分解能で問題が発生する。

- 速度とノイズのトレードオフ、集録時間などに対する制御に制限がある。

NIのFlexDMMテクノロジ

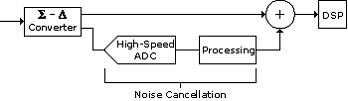

FlexADCが、NI FlexDMMシリーズ (PXIe-4080、PXIe-4081、PXIe-4082) を支えています。FlexADCにより、高速かつ高確度な計測に必要な低ノイズ、線形性、計測速度、柔軟性が実現されています。図4に示したFlexADCは、市販の高速ADCとカスタム設計シグマデルタコンバータの組み合わせをベースにしています。この組み合わせにより、線形性およびノイズを最適化して、最大7½桁の確度と安定性を提供するとともに、デジタイザモードでは最大1.8 MS/sのサンプルレートという高速を実現します。

図4. FlexADCコンバータ

図4のブロック図は、FlexADCの動作を簡単にモデル化したものです。低速度では、回路はシグマデルタコンバータのメリットを十分に利用します。フィードバックDACは、極めて低いノイズと優れた線形性が得られるよう設計されています。ローパスフィルタにより、すべての分解能にわたって効果的な性能を発揮するのに必要なノイズシェーピングができます。1.8 MS/sの超高確度変調器ではランプダウンなしで極めて高分解能な変換を行うため、ランプダウンは不要となります。高速度では、1.8 MS/sの変調器は高速サンプリングADCと組み合わされ、連続サンプルA/D変換を行います。デジタル信号プロセッサ (DSP) は、リアルタイムシーケンシング、キャリブレーション、線形化、AC真の実効値型計算、デシメーションを提供し、またDC機能に使用するノイズフィルタ機能を備えています。

FlexADCにはいくつかのメリットがあります。

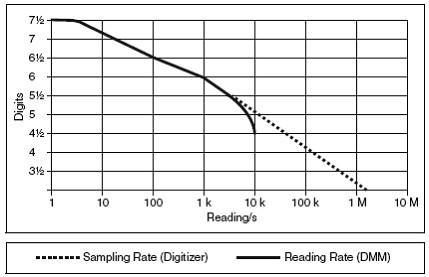

- 図5に示すFlexDMMの独特の構造により、7 S/s (7½桁) から10 kS/s (4½桁) までの連続可変の読み取り速度 (サンプリングレート) を設定できます。

- FlexADCを最大1.8 MS/sのサンプルレートでデジタイザとして使用できます。

- カスタム仕様のシグマデルタ変調器のため、ノイズシェーピングとデジタルフィルタは、DMMおよびデジタイザとして使用するために最適化されています。

- 他のADC変換技術とは異なり、入力信号のオン/オフをスイッチングする必要がありません。このため、連続的で切れ目のない信号集録が可能です。

- 従来のアナログAC Trmsコンバータやフラットネス補正用のアナログ「トリマ」を使用することなく、ACV直接変換および周波数応答キャリブレーションを実施できます。

- 適切なノイズシェーピングアルゴリズムを使用して、すべての機能に対して入力信号ノイズを大幅に軽減できます (「DCノイズ除去」を参照)。

- 信号をA/D変換すると、NI LabVIEWソフトウェアにより最新のホストベースの機能を実装できます。これには、高速フーリエ変換、インピーダンス計算、ACクレストファクタ、ピーク、AC平均などのさまざまな信号特性解析が含まれます。

図5. FlexDMM DC読み取り速度

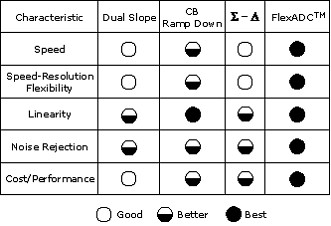

表2では、これら4つすべてのADCアーキテクチャを比較しています。

表2. ADCアーキテクチャの比較

低ノイズで安定性に優れたフロントエンドアーキテクチャ

すべてのFlexDMMは、最も安定性に優れたオンボード基準を採用しています。FlexDMMが使用する電圧基準はよく知られた熱的安定性に優れた基準で、比類のない性能を発揮します。このため、基準温度係数は最大でも0.3 ppm/ºC未満です。このデバイスの時間安定性は約8 ppm/年です。この価格範囲のDMMで、これだけの基準ソースと安定性を得られる製品は他にはありません。NI FlexDMMに2年間の確度保証が付帯しているのはこのためです。

抵抗測定は、本来要件の厳しい航空宇宙向けに設計された、安定性に優れた単一10 kΩの金属箔抵抗を基準としています。このコンポーネントは、保証温度係数が0.8 ppm/ºC未満、時間安定性が25 ppm/年未満の性能を備えています。

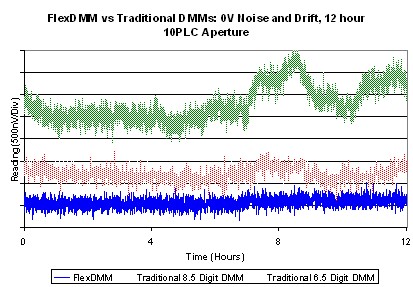

ソリッドステート入力信号調節

DMMで発生する従来のほとんどの計測エラーは、主にメカニカルリレースイッチが原因で発生していました。接触で誘発される熱電圧オフセットは、不安定性とドリフトの原因になることがあります。FlexDMMデバイスでは、DCV、ACV、および抵抗パスに使用する1個のリレーを除いてリレーは使用していません。特別なリレーの接点構成により、この単一リレーの熱エラーはキャンセルされます。このリレーはセルフキャリブレーション中のみスイッチ動作します。計測に関わる機能と範囲変更のスイッチ動作はすべて、信頼性に優れた低熱ソリッドステートスイッチによって行われます。これにより、メカニカルリレーの磨耗故障はほとんどすべて排除されます。最も感度の高い100 mV範囲のオーバーナイトドリフト性能を図6に示します。区切り線は500 nV刻みです。比較のため、従来の6½桁DMMとフルラック8½桁DMMを使用して行った同条件下での計測結果を図6に示します。

図6. FlexDMMの100 mV範囲の安定度を表した曲線 (下) を従来のDMMの曲線 (上) と比較した図 (500 nV/区切り)

線形性

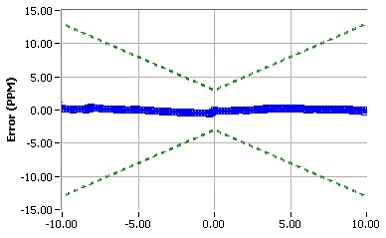

線形性とは、DMMの伝達関数の「品質」の指標です。変換コンポーネントの特性解析アプリケーションでは、市販のADCと比べて、DNLおよびINL (積分器の非線形性) の性能が大幅に優れていることが重要です。FlexADCは、DNLおよびINLの両方で、優れた線形性を考慮して設計されています。線形性が重要なのは、セルフキャリブレーション機能の再現性がそれで決定されるからです。図7に、10 V範囲 (-10~+10 V) で計測した通常のFlexDMMの線形性プロットを示します。

図7. 10 VDC範囲の線形性

セルフキャリブレーション

従来の6½および7½桁DMMは、特定の温度でキャリブレーションを行います。このキャリブレーションは、通常±5 ºC (±1 ºCの場合さえある) という制限された温度範囲で特性評価が行われ仕様が決定されます。つまり、DMMをこの温度範囲外で使用する場合、温度係数によって、その確度仕様の評価を下げる必要があることになります (通常は確度仕様/℃の約10%程度)。このため、この特定の範囲からの10 ºC逸脱すると、仕様計測エラーは2倍になり、完全な確度が重要な場合に深刻な問題となる可能性があります。

温度がこれらの制限から逸脱していても正確な仕様が必要とされる場合、再度新しい温度でキャリブレーションを行う必要があります。従来の7½桁DMMで10 VDCという範囲を例として取り上げましょう。DMMの確度を次のようなものとします。

2年間の確度:Tに対して (12 ppm (読み取り) + 0.5 ppm (範囲)) = ±5ºCのTselfcal

この仕様では、10 V の範囲を読み取るようプログラムされた入力に5 Vを印加すると、エラーは次のようになります。

12 ppm (5 Vの読み取り) + 0.5 ppm (10 Vの範囲) = 10 µV、ただし最後のセルフキャリブレーション時の温度で決まる温度範囲に対して。

PPMレベルの精度保証

このような影響によるエラーを排除するため、FlexDMMデバイスすべてに、直流電圧 (VDC)、抵抗、ダイオード、およびデジタイザモードに使用する専用のセルフキャリブレーション機能が組み込まれています。この機能が重要なのは次の理由によります。

1.セルフキャリブレーション機能は、DMM内のすべての信号パスゲインとオフセットエラーを、前述の高確度で安定性に優れた内部電圧基準に修正します。

2.セルフキャリブレーションは、すべての抵抗電流ソース、ゲイン、およびオフセットエラーに対処します。抵抗の場合、すべてのエラーを10 kWの高確度な単一の内部抵抗に修正します。

3. 1分のセルフキャリブレーションで、電圧、抵抗、およびデジタイザ機能の全範囲を完全にキャリブレーションします。従来のDMMでは、この機能の実行に10分以上かかりました。

結果として、どのような動作温度においても高確度が得られる超安定DMMが実現しました。セルフキャリブレーションにより従来の18~28 ºCの範囲外でも問題ありません。上記の例では、セルフキャリブレーションを使用した温度係数による追加のエラーが、90日仕様および2年仕様で完全にカバーされ、次のようになります。

温度係数 = (0.3 ppm (読み取り) + 0.01 ppm (範囲))/ºC、すると、追加されるエラーは次のようになります。

22 ºC x 温度係数 = (6.6 ppm (読み取り) + 0.22 ppm (範囲))、すなわち全体の不確定性は35.2 µVになります。周辺温度50 ºCでのこのエラーは、仕様化された1年間の確度のほぼ4倍のずれになります。

これは、FlexDMMの全動作温度範囲における確度の大幅な改善を表すものです。表3にこれらの結果のサマリを示します。

|

条件

|

従来の7½桁DMM (1年)

|

PXI-4071 7½桁FlexDMM

(2年) |

| 18~28 ºC内での計測 |

160 µV

|

65 µV

|

| セルフキャリブレーションなしで50 ºCでの計測 |

600 µV

|

111 µV

|

| セルフキャリブレーション による50 ºC での計測 |

600 µV (セルフキャリブレーションなし)

|

80 µV

|

表3.例のサマリ - 不確定性解析、10 V範囲で5 Vを計測する

セルフキャリブレーションありのFlexDMMを使用すると、従来の方法と比較して7倍優れた50 ºCでの確度を実現できます。表4では、セルフキャリブレーションと従来の「工場出荷時の」キャリブレーションを比較しています。

|

キャリブレーションオプション

|

アプリケーション

|

周期

|

性能上の利点

|

| 「工場出荷時の」キャリブレーション |

オンボード基準

の時間ドリフトを再キャリブレーション すべての機能で ACフラットネスドリフトを修正 |

2年ごと

|

フルスペックを保証

|

| セルフキャリブレーション |

7½桁の確度 -

VDCの計測パスとADC、抵抗、ダイオード、デジタイザの再キャリブレーション |

90日ごと、または温度変化が1 ºCを超えたとき

|

動作温度範囲全体にわたるVDC、抵抗、ダイオード、およびデジタイザ機能の仕様を保証

|

表4.キャリブレーションの比較

電圧計測アーキテクチャ

安定性が優れたDCおよびAC電圧機能の実現には妥協が許されません。FlexDMMが実現したこの性能には、複数の要素が貢献しています。

- 小型でサーフェスマウント可能かつ高性能の精密コンポーネントの入手のしやすさと品質は、過去10年で劇的に向上した。

- 小型で高密度にレイアウトされた電子回路パッケージの実用面での性能向上、特に高精度コンポーネント間での熱トラッキングの改善。

- ACV計算および周波数応答キャリブレーションへのFlexADCとDSPの採用により、入力信号調節を一般的なパスに単純化することが可能になり、コンポーネント数、複雑性、およびスイッチングの頻度が減少した。

- 箱型DMMでは一般的な「フロント/リア」スイッチがなくなることで、入力レイアウトを単純化でき、重要な回路信号パス抵抗が減少し、信号整合性が向上した。

- PXIシステムシャーシでは一般的コンポーネントである電源が計測モジュールでスペースを占有しない。

高電圧アーキテクチャ

NI PXI-4071では、CAT Iレベルで1000 VDCと700 VAC Trmsを計測できます。超小型PXIモジュールで1000 Vを正確に計測するには、コンポーネントの故障、電圧間隔、アッテネータ設計、フロントエンド回路の消費電力制限について考慮する必要があります。

10 MΩのシングル入力アッテネータ

DMMは従来より、フロントエンド信号調節回路に1 MΩと10 MΩの両方のアッテネータを使用していました。1 MΩアッテネータは、700 VAC信号の信号調節に使用した場合、0.5 Wを超える電力を消費します。これは小型精密コンポーネントとしては厳しい要件です。温度係数に起因するエラーの制御は、物理的に大きいコンポーネントにおいてさえ困難です。このため、1 MΩアッテネータの必要性をなくす必要があります。1 MΩアッテネータが従来のDMMに使用されてきたもう一つの重要な理由は、広いAC帯域幅です。従来の10 MΩアッテネータ使用の設計では、1 MΩアッテネータ使用の設計がもたらすAC帯域幅と同じレベルの実現は不可能です。

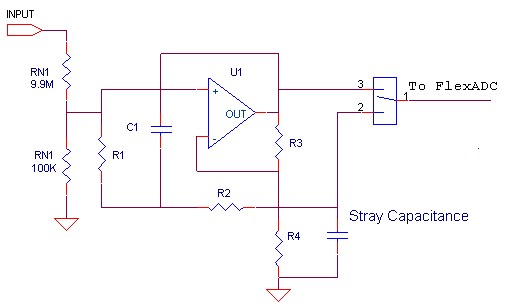

PXIe-4081 FlexDMMは、画期的なスケールブートストラップ設計を採用して、広帯域幅の性能を低下させるアッテネータのキャパシタンスをゼロにします。図8に示したこのブートストラップは、入力アッテネータネットワークRNの100 kΩアッテネータレグに負荷を与える浮遊キャパシタンスが最小になるよう設計され、入念にレイアウトされています。R1~R4、C1、およびU1によって形成されたスケールブートストラップを追加することで、フラットなステップ応答が保証されます。最も重要なのは、これにより特徴付けられた応答は、単極RCの応答に非常に似通ったものになるという点です。これはデジタイザおよびDCステップ応答にとって重要です。

図8. NI PXI-4071のスケール済みブートストラップ

次に、PXIe-4081は、補正コンデンサを使用せずに、デジタルAC DSPフラットネス補正を使用して、残留アッテネータフラットネスを補正します。単一のアッテネータがACrms、高精度DC、デジタイザ信号を伝達するという制限があるなか、これら2つの補正テクニックを使用することで他の方法に1桁勝る振幅改善が得られます。

コンポーネント故障と電圧間隔

高電圧計測で最も厄介な点は、範囲選択スイッチ (リレー) の故障です。従来よりDMMには高電圧リレーが使用されています。高電圧リレーによるスイッチングと優れた信頼性は、小型パッケージではもちろん、どのようなパッケージでも同時に実現することは容易ではありません。

これら両方の要件に応えるため、PXIe-4081ではまったく新しいソリッドステートデバイスを実装することで、オフ状態で1000 V以上に耐えられる範囲選択ができるようになりました。このデバイスには、メカニカルリレーが持つ従来の信頼性問題がありません。高電圧スイッチングで損傷を受ける接触、また、接触による寿命制限がないからです。ソリッドステート入力信号調節の2つ目のメリットは、優れた低レベルDC伝熱能力です。こうした組み合わせは現在5,000米ドル以内で購入可能ないかなる1000 V DMMでも見当たりません。

ソリッドステート高電圧スイッチに移行し、1 mΩ分周器の必要性をなくし、DSPを使用してキャリブレーションコンポーネントをなくすことによって、ボード表面とバルク領域の空きスペースが増え、電圧間隔の要件を満たすことができます。これで、1000 V PXI計測器のCAT Iの要件を満たすようにレイアウトを調節することが可能になります。

DCノイズ除去

DCノイズ除去は、すべてのFlexDMMデバイスによるDC計測で使用できるNI独自の機能です。FlexDMMが返す各DCの読み取り値は、実のところ複数の高速サンプルの計算結果です。これらのサンプルの相対加重を調整することで、他の干渉周波数への感度を調整できます。「標準」、「2次」、「高次」の3つの荷重があります。

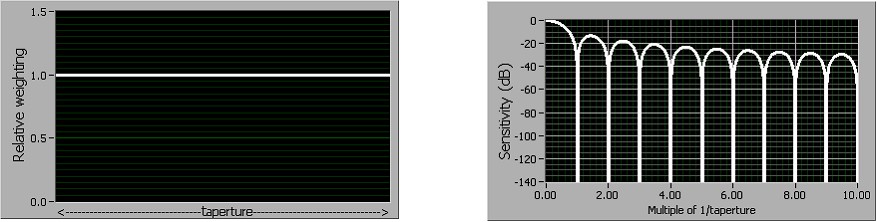

標準

標準DCノイズ除去を選択すると、すべてのサンプルを等しく加重します。このプロセスはほとんどの従来型DMMの動作をエミュレートするもので、f0の倍数 (f0 = 1/taperture - 計測に選択したアパーチャ時間) で優れた周波数除去を提供します。図9は、標準加重とそのノイズ除去結果を周波数の関数として示したものです。f0の倍数に近い領域でのみ優れたノイズ除去が得られることに注目してください。

図9.標準のDCノイズ除去

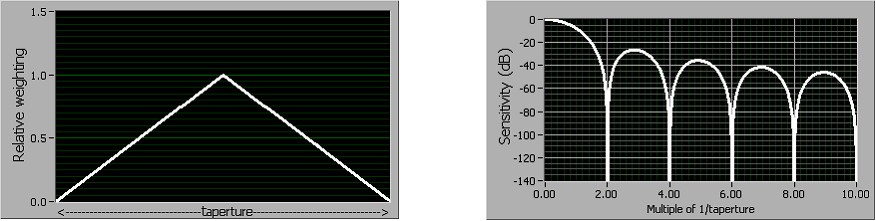

2次

2次DCノイズ除去は、図10のように計測サンプルに三角形の加重をかけます。f0の偶数倍領域で良好な除去が得られ、標準サンプル加重より周波数の増加とともに除去が急速に増大することに注意してください。また、応答ノッチが標準加重のノッチよりも広く、ノイズ周波数の微細な変動に対して感度が低くなることにも注意します。2次DCノイズ除去は、標準DCノイズ除去よりも良好な電源ノイズ除去を行う必要がある場合に適していますが、高次DCノイズ除去が可能になるほどサンプル取得を低速で行うことはできません。例えば、60 Hzの電源周波数には、アパーチャを33.333 msに設定することができます。

図10. 2次DCノイズ除去

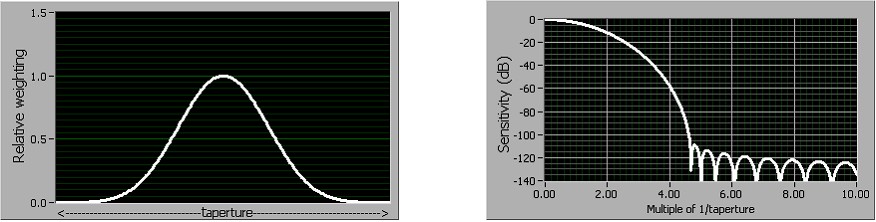

高次

図11は、高次サンプル加重とそのノイズ除去結果を周波数の関数として示したものです。4f0あたりでノイズ除去が良好になり始め、4.5f0以上で非常に優れた状態になることに注目してください。高次DCノイズ除去を使用すると、4.6f0以上の周波数ではノイズに対する感度がほとんどなくなります。100 msアパーチャ遅延 (10回読み取り/秒) で高次DCノイズ除去を行ったFlexDMMでは、干渉電源ノイズが1 Vを超える状態 (46 Hzを超える任意周波数で10 V範囲使用時) で完全6½桁の確度を実現できます。これは110 dBを超える標準モード除去に相当し、あらゆる電源周波数に対して反応しません。

図11. 高次DCノイズ除去

表5は、3つのDCノイズ除去設定の違いをまとめたものです。

| DCノイズ除去設定 | ノイズ除去対応最小周波数 | 高周波数ノイズ除去 |

| 標準 | 1/taperture | 良い |

| 2次 | 2/taperture | 適 |

| 高次 | 4/taperture | 110 dB除去より良い |

表5.DCノイズ除去設定

AC電圧計測

AC信号は通常、信号の合計エネルギーの指標であるrms振幅で表します。RMSは、二乗平均平方根 (root-mean-square) の略で、波形のrms値を計算します。信号レベルを二乗して平均値を出し、平方根を取ります。ほとんどのDMMは、アナログ領域で非線形信号処理を行いますが、FlexDMMではオンボードDSPを使用してAC波形のデジタルサンプルからrms値を算出します。結果としてノイズが少なく確度の高い、高速で整定するAC読み取り値が得られます。デジタルアルゴリズムにより自動的に信号のDCコンポーネントが拒否され、低速で整定する入力コンデンサをバイパスすることができます。DC電源のリプルなど、大きなDCオフセットの存在下で小さなAC電圧を計測するため、FlexDMMでは、標準AC電圧モードを使用してカプリングコンデンサでオフセットを除去し、FlexDMMが最も感度の高い範囲を使用できるようにします。

FlexDMMが使用するrmsアルゴリズムは、ほんの4周期 (サイクル) の波形を使用だけでノイズの少ない読み取りを行います。例えば、1 kHz正弦波を正確に測定するには、4 msの計測アパーチャが必要です。このテクニックによるメリットはシステム性能にまで及びます。従来のDMMでは、計測を開始するのにアナログTrmsコンバータが整定するのを待つ必要があります。FlexDMMでは、整定するのを待つTrmsコンバータがありません。その結果AC読み取り速度が速くなり、そのメリットはスイッチングを行うシステムで顕在化します。

rms計算へのデジタルアプローチでは、確度の向上も期待できます。クレストファクタにまったく影響されないアルゴリズムにより、乱れのない非常に安定した読み取り値が得られます。FlexDMMが提供するAC確度は、従来のDMMが提供するフルスケールの10%ではなく1%を保証し、さらにフルスケールの0.1%以下でも有効な読み取り値が得られます。

電流計測アーキテクチャ

DMMの電流計測ダイナミックレンジの拡張は、増え続けるユーザの需要を満たすための要件となっています。高電流では、バッテリ、回路、または電気機械装置の負荷性能の監視が必要になる場合があります。現在の統合された電子機器はより多くの電力を必要としています。このため、こうしたデバイスのテストおよび特性解析を1 Aよりも高いレベルで行う必要性が高まっています。一方低電流では、現在、半導体機器の「オフ」特性評価など、多くの用途でマイクロアンペアまたはナノアンペアレベルでの計測が必要になっています。

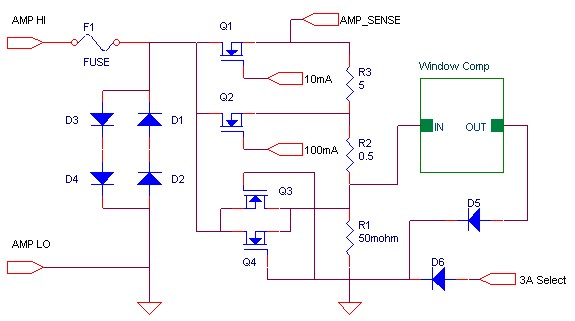

PXIe-4081は、これら両方のニーズに対応します。新しいソリッドステート電流計測構成を実装することで、1 µA~3 Aの8つのDC電流範囲、また電流範囲は100 µA~3 Aの6つのACrmsを実現しました。1 µA範囲では最小1 pA、すなわち10-12 Aまでの感度を提供します。両極端への対応には独創的な回路設計アプローチが必要になります。高電圧または過負荷電流保護と低漏電計測に関する問題への対処は、従来より相互排他的でした。FlexDMMには、図12に示す独自の設計アプローチを実装しています。この非常に簡略化された図は、PXI-4071での5つの電流範囲のうち3つを示しています。

図12. PXI-4071電流信号調節の簡略化モデル

電流範囲の選択にソリッドステートデバイスを使用すると、狭いスペースで優れた信頼性および保護を実現することができます。さらに、電流範囲選択デバイスのうちの2つ (Q3およびQ4) が実際に動作するのは過負荷時です。従って、安定性に優れた電流感知抵抗が保護され、最も要件の厳しいアプリケーションに堅牢性が加わります。

1.8 MS/s絶縁デジタイザアーキテクチャ

PXIe-4081 FlexDMMには、最高サンプルレート1.8 MS/sで最大1000 VDCおよび700 VAC (1000 Vp) 入力のDC結合波形を取得する機能もあります。サンプルレートを変更するだけで、デジタイザの解像度を10ビットから26ビットに変更できます。 FlexDMMでは、絶縁デジタイザ機能により、個別のデジタイザを購入する必要がなく、テストフィクスチャのサイズとメンテナンスコストを削減することで、テストシステム全体のコストを最小限に抑えることができます。

LabVIEWグラフィカル開発ソフトウェアをFlexDMMの絶縁デジタイザモードと組み合わせることで、時間領域と周波数領域の両方で、過渡信号やその他の非反復高電圧AC波形の解析も可能です。FlexDMMを除いてこの機能を持つ高分解能DMMはありません。

例えば、自動車産業での一般的なアプリケーションとして、イグニッションコイルのフライバック電圧の計測があります。エンジンのスパークプラグ動作用の高電圧を発生させるイグニッションコイルは、一次コイルと二次コイルから構成されています。一般的には二次コイルの巻き数は一次コイルより多くします。これは、一次コイルに加えた電圧に巻き数比を乗じたものが出力電圧になるからです。電流が突然転流されると磁界が消滅して、二次コイルに大きな電圧 (+20,000 V) が誘導されます。この電圧がスパークプラグに電流を流します。

二次コイルに流れる電圧が非常に高いため、実際のテストは一次コイルで行われます。フライバック波形は通常、約10 µsになり、イグニッションコイルによってピーク電圧は40~400 Vになります。この波形で行われる一般的な計測は、ピーク点火電圧、滞留時間、および燃焼時間です。FlexDMMのデジタイザ機能とLabVIEWの解析機能を使用すれば、フライバック電圧計測システムを構築することができます。

絶縁デジタイザの利点

絶縁を施すと、大きなコモンモード信号がある場合でも小さな電圧を安全に計測できます。絶縁の3つのメリットは次のとおりです。

- 除去の向上 – 絶縁によって、計測システムがコモンモード電圧を除去する能力を高めます。コモンモード電圧とは、計測デバイスの正極入力および負極入力の両方に存在する「共通・同相」の信号のことで、計測すべき信号の一部ではありません。例えば、コモンモード電圧は、燃料電池で数百ボルトになることがよくあります。

- 安全性の向上 – 絶縁バリアを使用することで、大きな過度電圧スパイクから保護しながら浮動計測を行うことができます。適切な絶縁計測回路であれば通常、2 kVより大きなスパイクに耐えられます。

- 確度の向上 – 絶縁により、物理的にグランドループを回避することによって、測定の確度が向上します。グランドループはエラーとノイズの一般的な原因であり、計測システムが異なる電位で複数のグランドを持つ場合に発生します。

抵抗計測アーキテクチャ

FlexDMMには、抵抗計測機能が備わっています。2線式と4線式両方の抵抗計測機能があります。4線式テクニックが使用されるのは、長いケーブルやスイッチが「リード線」抵抗オフセットとなり、低抵抗の計測が難しくなる場合です。しかし、オフセット電圧が大きなエラーの原因となる場合があります。

オフセット補正抵抗

このような場合、FlexDMMではオフセット補正による抵抗計測を行います。この計測は、多くの抵抗計測アプリケーションで見られるオフセット電圧に影響されません。

- 非補正のリードリレーを使用したスイッチシステムの抵抗計測 (デバイスのガラス封着にコバールのリード素材が使用されており、オフセット電圧が10 µVを超える)。

- インサーキット抵抗計測 (例えば、検証対象回路が通電状態で、電源導線の抵抗を計測する)。

- バッテリのソース抵抗、フォワードバイアスダイオードの動的抵抗などの計測。

上記のケース1では、テストシステムのスイッチング構成は抵抗計測以外の用途に最適化されている場合が多くみられます。例えば、リードリレーはRFテストシステムでよく使用されます。これは、リードリレーが予想可能なインピーダンス特性と信頼度に優れているからです。このようなシステムでは、検証対象ユニットの抵抗も計測する場合が多く、リードリレーが既にシステムに組み込まれています。

ケース2では、例として、電源オン時の電源バス配線の抵抗測定があります。(注: これらのテストを実施する場合は十分注意してください。) 抵抗が10 mΩの範囲と想定します。この抵抗に100 mAの電流が流れる場合、電圧降下は次のようになります。

100 mAの範囲に対してオフセット補正しないDMMは、これを1 Ωと解釈します。この電圧は、計測中の配線に流れる内部電流1 mAによって生成されたものと見なすからです。このDMMは違いを認識しません。オフセット補正抵抗を有効にしたFlexDMMを使用すると、1 mVのオフセットは区別されて拒否されます。その結果、抵抗の正しい値が返されます。

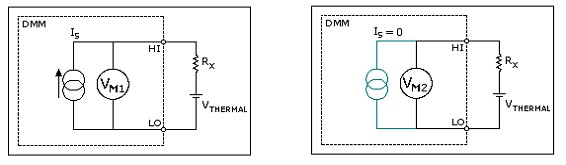

図13. 電流オン時の最初のサイクル 図14.電流オフ時の2番目のサイクル

この計測には2つのサイクルを使用します。最初は、図13のように、電流ソースをオンにして計測します。2番目は、図14のように、電流ソースをオフにして計測します。2つの計測間の違いが最終結果となります。オフセット電圧はどちらのサイクルにもあるため、下記のように差し引いて抵抗計算の中に含めないようにします。

VOCO = VM1 - VM2 = (ISRX + VTHERMAL) - VTHERMAL = ISRX

結果:

RX = VOCO/IS

まとめ

NIは、FlexADCテクノロジに基づいて、高性能のシングルスロット3U PXI-4081 FlexDMMを開発しました。従来のDMMでエラーの温床となっていたアナログ機能の多くが、市販の高速デジタイザ、DSPテクノロジ、およびホストコンピュータを使用することで置き換えが可能になりました。2年のキャリブレーションサイクルのセルフキャリブレーションで、動作温度範囲0~55 ºC全域にわたって最高の確度が実現します。安定性に優れた内蔵の基準要素を組み合わせることで、世界で最も速く、最も確度の高いPXI DMMが完成しました。従来のDMMに匹敵、あるいはそれを凌駕する、妥協のない機能と性能をお届けします。