NI VeriStand用にFPGAベースのI/O機能を作成

概要

内容

- FPGAベースのI/Oインタフェースとは?

- リアルタイムテストアプリケーションにFPGAを使用するメリット

- NI VeriStandでカスタムFPGA機能を使用する

- NI VeriStand FPGA機能のアーキテクチャ

- 次のステップ

FPGAベースのI/Oインタフェースとは?

FPGA(Field-programmable gate array)とは、ASIC(特定用途向け集積回路)などに見られるハードウェアロジックベースの優れた実行性能や信頼性などのメリットをもたらす再プログラミング可能なシリコンチップで、ソフトウェアやファームウェアをベースにしたインタフェースに劣らない柔軟性を備えています。構成可能な論理ブロックとプログラム可能な経路設定リソースを利用すると、デバイスを物理的に変更しなくても、FPGAを構成してカスタムハードウェア機能を実装することが可能です。ソフトウェアでデジタル演算タスクを開発し、ビットストリームファイルにコンパイルします。ビットストリームファイルとは、FPGAのロジックや経路設定コンポーネントの構成方法や接続方法に関する情報が含まれるファイルです。

リアルタイムテストアプリケーションにFPGAを使用するメリット

ユーザ定義のFPGAベースのI/Oインタフェースを使用すると、信号処理、シミュレーション、トリガ、制御などのタスクを組み合わせて実装し、お客様のアプリケーションのニーズにぴったりのI/Oインタフェースを生成することができます。また、I/OインタフェースはFPGAを採用しているため、インタフェースの特性や動作を再構成すれば、ハードウェアのセットアップを変更せずに新しい要件に合わせたり複数のアプリケーションに使用できるテストシステムを構築したりできます。

リアルタイムテストアプリケーションでFPGAを使用する最大の理由に、カスタマイズ可能なI/Oがあります。100種類以上あるNI Cシリーズ信号調節モジュールから選んで、アプリケーション専用のインタフェースを組み込むことができます。そのような多彩な信号調節オプションと柔軟性の高いFPGAベースのI/Oデバイスを併せて使用することで、お客様のリアルタイムテストアプリケーションの要件を完全に満たすカスタムタイミング/トリガ機能を備えたI/Oインタフェースを短時間で作成することが可能です。

また、FPGAをデータの前処理や後処理に使用して、リアルタイムテストアプリケーションを実行しているマイクロプロセッサの負荷を軽減することもできます。例えば、FPGAはエンコーダからデジタルデータを集録して、リアルタイムテストアプリケーションに情報を渡す前にその信号の速度と加速度を計算することがあります。

また、リアルタイムテストアプリケーションでFPGAを使用すると、高速閉ループ制御を追加することも可能です。例えば、FPGAにモーションコントローラ機能を実装して、リアルタイムテストアプリケーションでコントローラのセットポイントを設定することができます。そうすることで閉ループ制御の応答が格段に速くなり、システムをより高精度で制御することが可能となります。この方法の例として、ブラシレスDCモータの制御があります。

さらに、FPGAを使用することで、HILテスタの実装で、さまざまなセンサをシミュレーションすることもできます。FPGAは、正確なタイミングが要求される複数のセンサタイプに適応できるため、センサのシミュレーションにも最適です。ナノ秒レベルの分解能でセンサを実装して、センサの応答信号をよりリアルにシミュレーションすることが可能です。多くの場合、センサは異なる応答レートで個別に機能します。FPGAは物理的な並列性を備えているため、FPGAのコンポーネントの実世界での動作を再現するには最適です。NI VeriStandアドオンコミュニティには、ダウンロード可能なFPGA XML Builder Nodeが用意されています。

NI VeriStandでカスタムFPGA機能を使用する

一般的なアプリケーションでは、開発者はカスタムFPGAロジックのプログラミングと、FPGAロジックとリアルタイムプロセッサで実行中のアプリケーションの間の通信メカニズム、そしてリアルタイムアプリケーションでのデータの前処理と後処理を行う必要があります。NI VeriStandを使用すると、通信メカニズムとデータ処理という2つの部分を実装できるフレームワークが備わっているため、短い開発期間でFPGAを使用したリアルタイムテストアプリケーションが実現できます。NI VeriStandでFPGA機能を使用するのは簡単です。まずFPGA機能を開発してから、XMLファイルを使ってNI VeriStandリアルタイムテストアプリケーションとの間のインタフェースを指定するだけです。

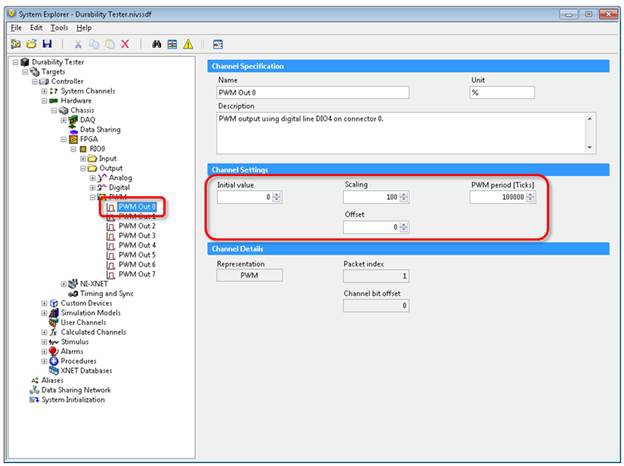

NI VeriStand FPGA機能を作成するには、まずNI LabVIEWソフトウェアでNI VeriStandアプリケーションとの通信に必要なコードが含まれたテンプレートプロジェクトを起動します。このフレームワークでは、LabVIEWを使用してカスタムFPGA機能を設定し、コンパイルしてから、XMLファイルを編集します。これらの手順が完了したら、XMLファイルを選択するだけで、機能をNI VeriStandシステム定義に追加することができます。XMLファイルは、FPGA機能との通信方法をNI VeriStandに伝え、NI VeriStand System Explorer内で入力、出力、およびパラメータを自動で指定するので、他のハードウェアインタフェースの場合と同様に、値や他のリアルタイムタスクとの接続を設定することが可能です。例えば、PWM出力でFPGA機能を定義すると、NI VeriStand System Explorerで周期や初期値などのチャンネルパラメータを設定したり、図1に示すようにデューティサイクル入力をリアルタイムテストアプリケーションの他のチャンネルにマッピングすることができます。

図1: System ExplorerでNI VeriStand FPGA機能を構成する

NI VeriStandリアルタイムアプリケーションを実装すると、NI VeriStandはコンパイル済みのFPGA機能をハードウェアインタフェースに自動でダウンロードします。

NI VeriStand FPGA機能のアーキテクチャ

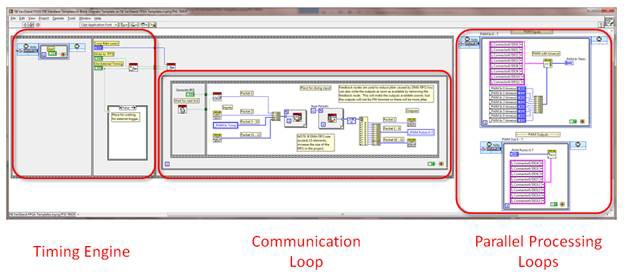

LabVIEW FPGAモジュールを使用してNI VeriStand FPGA機能を作成し、NI VeriStandアプリケーションとの通信に必要なコードを含む機能テンプレートを修正します。NI VeriStandにおけるFPGA機能は、タイミングエンジン、通信ループ、並列処理ループで構成されます。

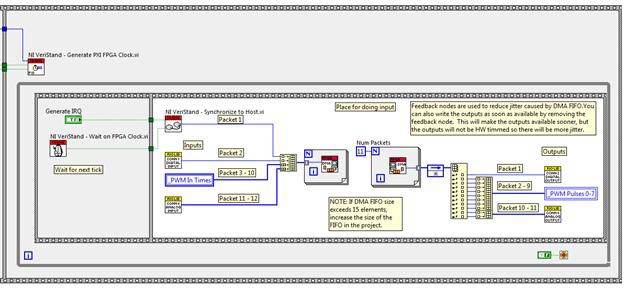

図2: NI VeriStand FPGA機能のテンプレート

タイミングエンジン

タイミングエンジンは、NI VeriStand System Explorerで構成するもので、FPGAをNI VeriStandリアルタイムアプリケーションやシステム内の他のハードウェアI/Oデバイスと同期させます。NI VeriStandリアルタイムアプリケーションが実装されたら、FPGA機能がロードされ、タイミングエンジンはNI VeriStandから開始状態で待機します。

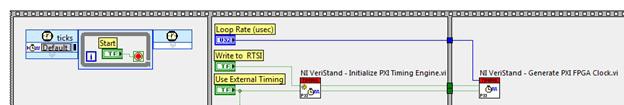

図3: タイミングエンジンの初期化

リアルタイムアプリケーションがStartトリガをアサートする前に、NI VeriStandはLoop Rate (µs)、Write to RTSI、Use External Timingのパラメータを設定します。これらの3つのパラメータは、タイミングエンジンの同期モード(マスタ、スレーブ、非同期)の指定と、FPGA機能とNI VeriStandリアルタイムアプリケーション間の通信レートの設定を担います。

NI VeriStand – Generate PXI FPGA ClockサブVIは、後述の通信ループのタイミングをとったり同期を処理するクロックを生成します。マスタモードでは、FPGA上で実行するループタイマにより通信ループのタイミングをとり、クロックをRTSI(Real-Time System Integration)バスにエクスポートして他のハードウェアデバイスと同期します。スレーブモードでは、FPGAはRTSIバスを監視して、RTSI0で捉えたクロックにより通信ループのタイミングをとります。非同期モードでは、FPGAは自身のループタイマによって通信ループの同期をとり、RTSIバスには何もエクスポートしません。

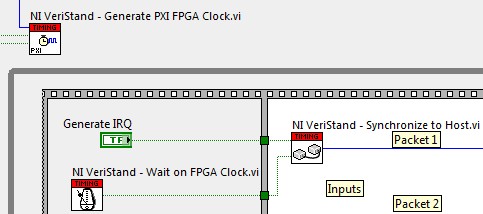

タイミングエンジンは、ハードウェアの同期の実行に加え、NI VeriStandリアルタイムアプリケーションとの同期も可能です。通信ループの一部を図4に示します。

図4: NI VeriStandをFPGAと同期

NI VeriStand – Wait on FPGA ClockサブVIは、通信ループのループタイマとして動作し、NI VeriStand – Generate PXI FPGA ClockサブVIからのクロックを待ちます。マスタモードでは、NI VeriStandはStart制御器をアサートする前にGenerate IRQをアサートします。Generate IRQ がアサートされている場合、NI VeriStand – Synchronize to HostサブVIは通信ループの各反復において割り込みをアサートします。FPGAがマスタとして構成されている場合、NI VeriStandリアルタイムアプリケーションの実行の際は、FPGAによってこのIRQ信号経由でタイミングがとられます。

通信ループ

通信ループは、NI VeriStandリアルタイムアプリケーションとの間でデータを送受信する役割を担っています。NI VeriStandでは、ハードウェアタイミングによるシングルポイント方式でチャンネルをアップデートするので、FPGAは通信ループをNI VeriStandエンジンのプライマリ制��ループで指定したレートで実行する必要があります。NI VeriStandエンジンの詳細については、NI VeriStandのヘルプを参照してください。

通信ループは、NI VeriStand – Wait on FPGA ClockサブVIによってタイミングがとられます。このサブVIは、上述のNI VeriStand – Generate PXI FPGA ClockサブVIにより生成されたクロック上で待機するループタイマとして動作します。

図5: データ通信ループ

図5に示すように、64ビットパケット形式のデータがDMA first-in-first-outメモリバッファ(FIFO)経由でNI VeriStandリアルタイムアプリケーションに送られ、NI VeriStandリアルタイムアプリケーションからの64ビットパケット形式のデータがDMA FIFO経由で受信されます。

NI VeriStandに最初に送られるパケットには、FPGAループの実行が遅れているかどうかを示すNI VeriStand – Synchronize to HostサブVIからの情報が含まれます。ホストに送られるその他のパケットには、FPGAで実行された計測または計算データが含まれています。パケットを送信するには、Forループ内のNI VeriStand – Send Packet to HostサブVIに書き込みを行います。このサブVIの役割は、DMA_READ FIFOに書き込むことです。DMA_READ FIFOはプロジェクトエクスプローラで定義され、その深度は少なくとも各反復で送信されたパケットと同じ要素数に指定する必要があります。

データは、やはりプロジェクトエクスプローラで定義されるDMA_WRITE FIFO経由でFPGAに送られます。深度は、少なくとも各反復で送信されたパケットと同じ要素数に指定する必要があります。DMA_WRITE FIFOは、Forループ内に配置されているNI VeriStand – Receive Packet from HostサブVIによってFPGA上で読み取られます。Forループは、Whileループの反復ごとに読み取る必要のあるパケットと同じ回数実行するよう設定する必要があります。するとパケットは分割され、FPGA機能の適切な部分に送られます。図5では、黄色のタイトルバーの付いたサブVIがI/Oリソースを示しています。このループで集録・生成されるI/Oは、全てNI VeriStandおよびシステム内の他のハードウェアデバイスと同期されます。

並列処理ループ

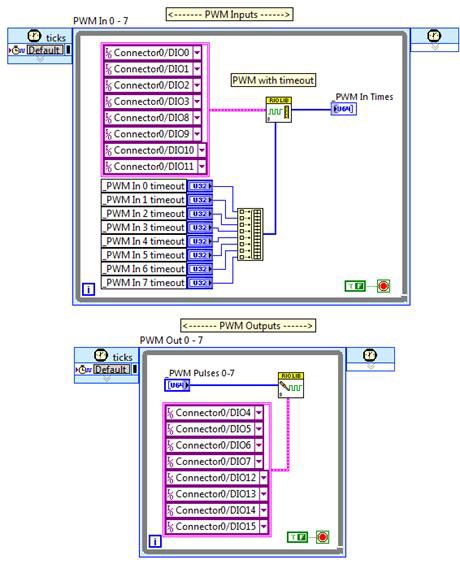

並列処理ループは、NI VeriStandフレームワークにおけるカスタムFPGA機能の最後の部分です。これらのループは並列ループと呼ばれます。それは、NI VeriStandへの通信ループとシステム内の他のハードウェアと同じクロックでタイミングが取られていないためです。それらのループは、単にカスタムタイミングのI/O上でデータを集録・生成していることもあれば、PWM I/Oなどのカスタム計測・生成を行う場合もあります。また、NI VeriStandからFPGAに送信されたデータのコプロセッシングに使用されることもあります。図6に示すように、サンプルテンプレートにはPWM入出力が含まれています。

図6: 並列PWMループ

図5と図6に示すように、並列処理ループと通信ループの間のデータ送信は、ローカル変数を介して行われます。通信ループはそれらのローカル変数を自身の実行と同じレートでしか更新せず、ローカル変数の現在値(バッファなし)をNI VeriStandホストにのみ送信します。並列ループのデータは通信ループによってデシメーションされますが、並列ループのタイミングは通信ループの影響を受けません。

次のステップ

FPGAベースのI/Oインタフェースは、リアルタイムテストアプリケーションに多くのメリットをもたらします。信号処理、シミュレーション、トリガ、制御などのタスクを組み合わせて実装し、新たな要件に合わせて簡単に再構成できるカスタムI/Oデバイスや、ハードウェアの設定を変更せずに複数のアプリケーションに使用できるテストシステムを作成することができます。NI VeriStandを使用すると、通信メカニズムとデータ処理を開発者に代わって実装するフレームワークが備わっているため、少ない開発量でFPGAを使用したリアルタイムテストアプリケーションが実現できる上、FPGA機能の開発に専念できます。その後他のハードウェアI/Oインタフェースの場合と同じように、NI VeriStandにFPGA機能をシームレスに組み込んで、リアルタイムテストアプリケーションの残りの部分をプログラミング不要な環境で完成させます。