用于FlexRIO的控制器:深入了解可部署的仪表

概览

用于FlexRIO的控制器是一款现成即用型(COTS)解决方案,其外形小巧、可独立运行,旨在满足应用的高性能I/O和实时信号处理需求。模块化I/O、LabVIEW可编程FPGA和板载处理器的组合使工程师能够针对特定应用全面重新配置硬件,这使得用于FlexRIO的控制器有别于大多数COTS仪器。该控制器还与PXI上的FlexRIO共享相同的适配器模块、FPGA和软件体验,使其成为在PXI平台上开发解决方案的理想部署目标。尽管与PXI中的FlexRIO有许多共同之处,但其主要用于满足嵌入式应用中更紧凑、更轻便、更低功耗的需求。

内容

图1:用于FlexRIO的控制器是一款独立式信号采集和处理设备,具有高性能I/O和大型Kintex-7 FPGA。

内部架构

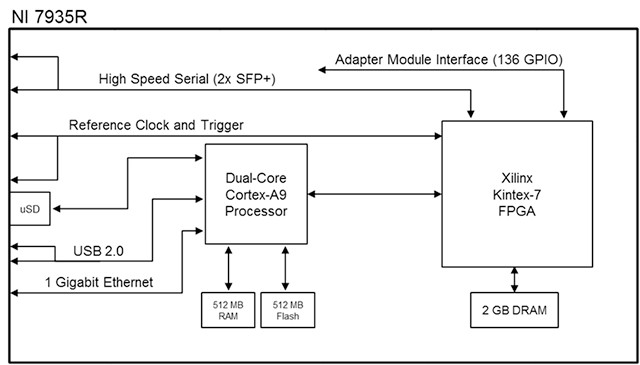

用于FlexRIO的控制器基于大型Kintex-7 FPGA构建,该FPGA可连接至模块化I/O接口、处理器和2 GB DDR3 DRAM。FPGA内置超过400,000个逻辑片、1,540个数字信号处理(DSP)切片和28 Mb BRAM,可实现大量信号处理。双核ARM处理器提供网络和USB连接,用于连接其他设备,并提供用于参数和数据记录的板载存储。

尽管在FPGA上可以实现大多数算法,但将大型FPGA和低功耗处理器相结合尤为必要,可以将双核ARM处理器用于上电配置和系统监控。该架构使智能更接近边缘,其中可借助高性能FPGA将高速数据转换为有意义的信息。

图2:用于FlexRIO的控制器采用大型Kintex-7 FPGA,非常适合需要实时运行信号处理算法的应用。

如需在中心位置聚合高带宽数据,NI 7932R和NI 7935R还配有2个高速串行端口,可使用10千兆位以太网UDP、Xilinx Aurora或自定义协议直接从FPGA传输数据。

FlexRIO适配器模块接口

图3:NI 5772是一款双通道高速数字化仪适配器模块,常用于时域和频域测量。

FPGA

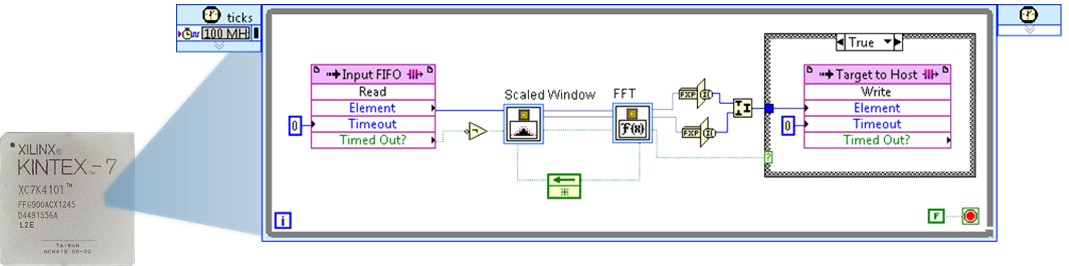

用户可通过LabVIEW FPGA模块,使用LabVIEW系统设计软件对FPGA进行编程,实现基于LabVIEW的算法捕捉和VHDL/Verilog集成。现有的LabVIEW库可用于加速开发数据移动基础设施、高级信号处理功能,如超宽带快速傅立叶变换(FFT)和并联重采样算法,以及托管DMA流至主机。在本地编译或使用NI编译云服务之前,可在LabVIEW中对设计进行仿真。使用LabVIEW FPGA和Xilinx Vivado编译FPGA比特文件后,在开发机器上部署比特文件的方法有3种:通过LabVIEW;通过由LabVIEW或C/C++构建并在控制器上运行的实时应用程序;或通过设备上电时的闪存。在诸多FlexRIO设计中,逻辑的时钟频率为数百兆赫兹,因此更难满足定时约束。NI建议LabVIEW FPGA开发新手首先阅读高性能LabVIEW FPGA开发人员指南,了解有关定时和资源优化的最佳实践。

图4:LabVIEW为设计、仿真、调试和部署提供了一个集成式图形化开发环境,简化了FPGA编程过程。

工程师可在2种FPGA选项中进行选择:Xilinx Kintex-7 K325T和大型K410T。在开发初期,使用最大的FPGA具有显著优势。它不仅可在开发过程中灵活添加功能,用户还可以在大型FPGA上编译相同的代码,从而普遍减少设计过程中的编译时间,尽可能加快迭代速度。借助NI提供的I/O接口,可以将针对一个硬件终端编写的LabVIEW FPGA代码快速移植至其他NI硬件,甚至可以是具有不同FPGA和I/O功能的硬件。

FPGA | 切片 | LUT | 触发器 | DSP切片 | 块RAM (kb) | 板载DRAM |

Kintex-7 K410T | 63,550 | 254,200 | 445,200 | 1,540 | 28,620 | 2 GB |

Kintex-7 K325T | 50,950 | 203,800 | 407,600 | 840 | 16,020 | 2 GB |

图5:用于FlexRIO的控制器具有2个不同的Xilinx FPGA,便于用户根据应用选择合适的器件。NI建议在尝试优化部署设计之前,使用最大的FPGA进行初期开发。

DRAM资源可为多级信号处理算法和跨非确定性总线的数据缓冲附加重要价值。 为实现该类型的操作,用于FlexRIO的控制器具有3种变体,且所有变体均有一个与FPGA连接的2 GB DDR3 DRAM组。DRAM接口的数据宽度为512位,可在高达166 MHz的时钟速率下进行有效访问,因此DRAM和FPGA之间的最大理论带宽可达10.6 GB/s。随机存取读写会降低DRAM吞吐量,但NI已对9 GB/s以上的顺序读写进行了基准测试。DRAM可通过LabVIEW FPGA中的LabVIEW存储器项进行寻址,也可将存储器仪器设计库(IDL)作为FIFO进行寻址。

高速串行

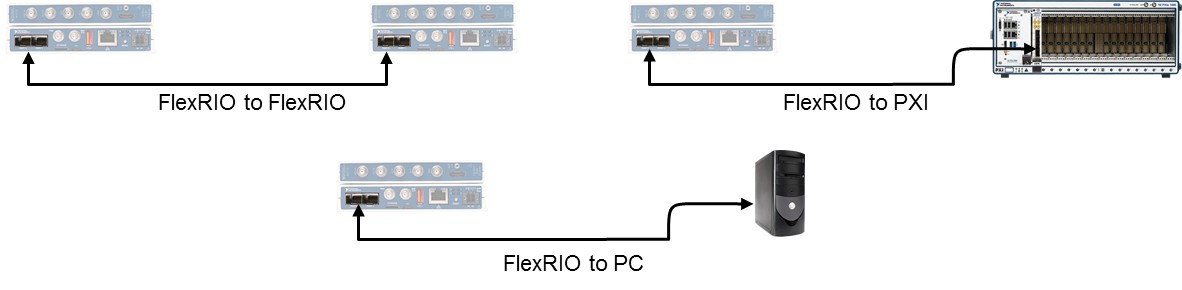

对于在信号采集和处理后需要高带宽数据传输的应用,NI 7932R和NI 7935R搭载了2个高速串行收发仪,每个收发仪的数据传输速率高达10.3125 Gb/s。该技术依赖于Xilinx GTX多千兆位收发器(MGT),MGT从FPGA连线至前面板上的2个SFP+连接器。NI提供了可用于10千兆以太网UDP和Xilinx Aurora协议的LabVIEW FPGA范例项目。熟悉VHDL的用户可以执行其他协议,如串行RapidIO或自定义协议。

使用这些高速串行端口的数据流配置示例包括使用Xilinx Aurora在多个控制器之间共享数据、 使用Aurora或10千兆以太网将数据传输回PXI,以及通过10千兆以太网将数据传输至台式机、数据记录仪、网络区域存储(NAS)或服务器。

图6:高速串行端口旨在将高带宽的数据传输至多个设备。在LabVIEW FPGA中定义通信协议,每个收发仪的运行速度高达10.3125 Gb/s。

时钟

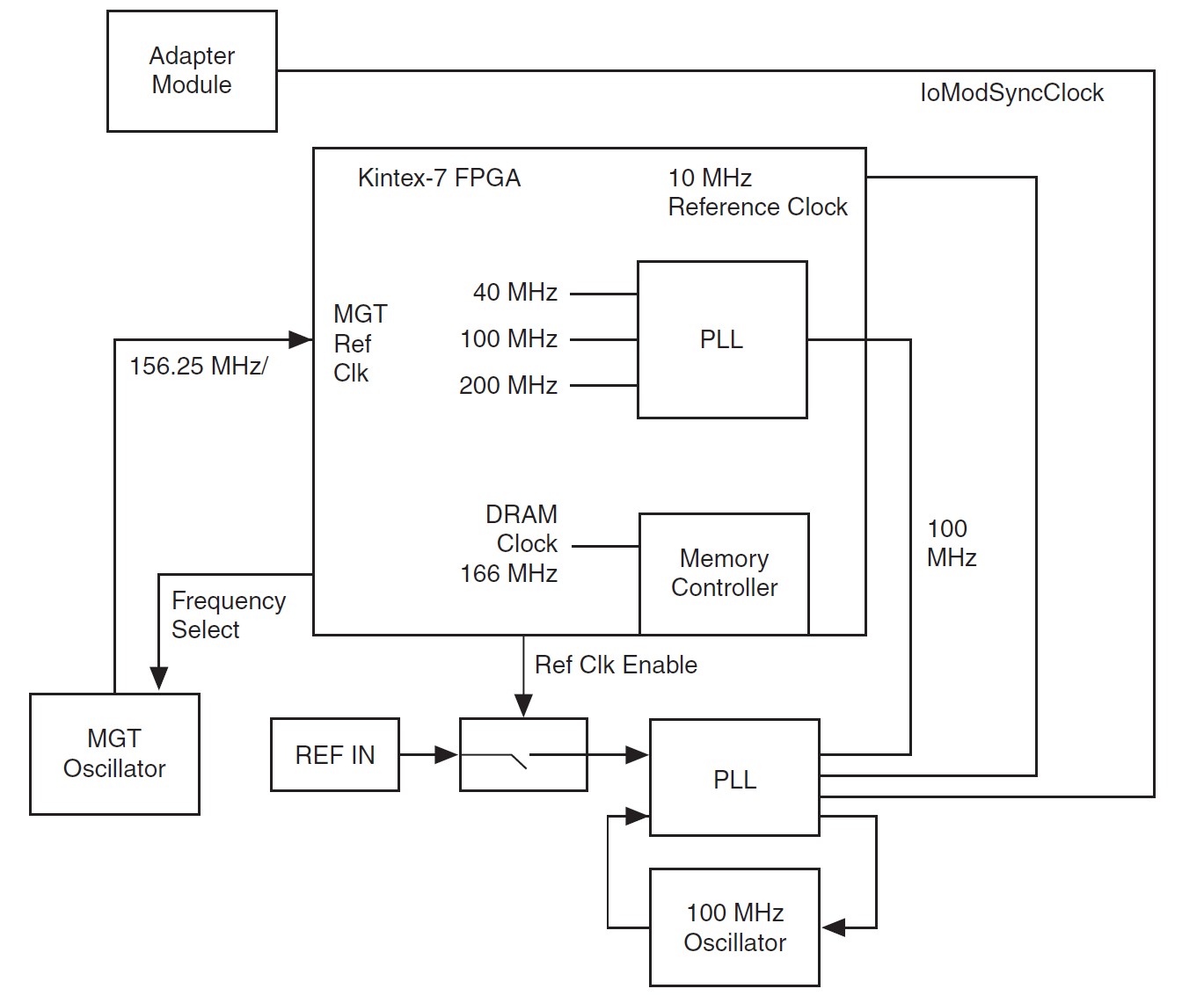

使用FPGA和高速I/O的工程师通常会花费大量时间来实现合适的时钟和同步架构。为简化该过程,用于FlexRIO的控制器提供多种时钟选项,包括外部10 MHz参考时钟输入、双向触发线、板载100 MHz振荡器以及对外部参考的 锁相能力。为确保I/O模块与FPGA之间的同步数据传输,I/O模块采样时钟与用于FlexRIO的控制器时钟电路共享。也可在FPGA上导出其他时钟。

图7:用户通过用于FlexRIO的控制器中的时钟电路,可以以子采样精度同步多个设备。

对于分布式系统和时间戳,可连接GPS接收器为参考时钟输入提供10 MHz时钟,为触发器SMA提供每秒1个脉冲的输入。对于不太严格的同步要求,NI Linux Real-Time主机还支持基于软件的IEEE 1588。对于可实现电同步的系统,可使用Ettus Octoclock等10 MHz时钟源提供共享参考时钟。在多个单元共址的情况下,可以考虑PXI平台的高级时钟和同步功能。

处理器

双核ARM Cortex-A9处理器加强了在现场部署用于FlexRIO的控制器所需的灵活性和连接性。它可用于向网络提供数据、调整配置参数、记录数据和消息,甚至更新设备上运行的软件和FPGA固件。该处理器在运行NI Linux Real-Time操作系统时,具有更高的确定性和可靠性,以及Linux内核的标准优势。实时操作系统(RTOS)可使用LabVIEW Real-Time模块通过LabVIEW进行编程,还支持通过用户首选的集成开发环境(IDE)进行C/C++开发。开发人员通过使用LabVIEW编程和构建应用程序,可访问用于网络通信和文件I/O的预构建库,从而显著简化开发工作。

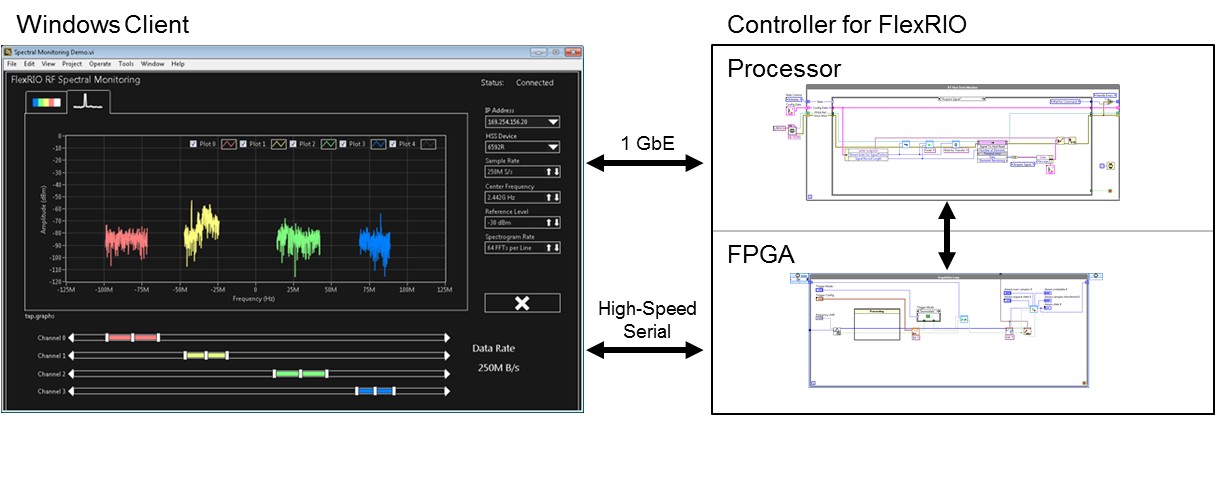

对于熟悉FlexRIO的用户而言,从PXI上的FlexRIO迁移至用于FlexRIO的控制器,其主要区别在于FPGA与传统的Windows客户端之间增加了网络通信层。为NI Linux Real-Time开发的代码以FPGA为目标,而非直接在Windows系统中针对FPGA,用户负责编写用于监控或配置系统的任何网络通信程序。在NI 7932R和NI 7935R中,用户可利用2个高速串行端口,通过10千兆以太网UDP或Xilinx Aurora直接从FPGA流式传输数据。

图8:所部署的系统通常包含3个应用程序层:运行在FPGA上的固件、运行在Linux Real-Time主机上的LabVIEW或C/C++代码,以及用于远程配置、监控或数据记录的客户端应用程序。

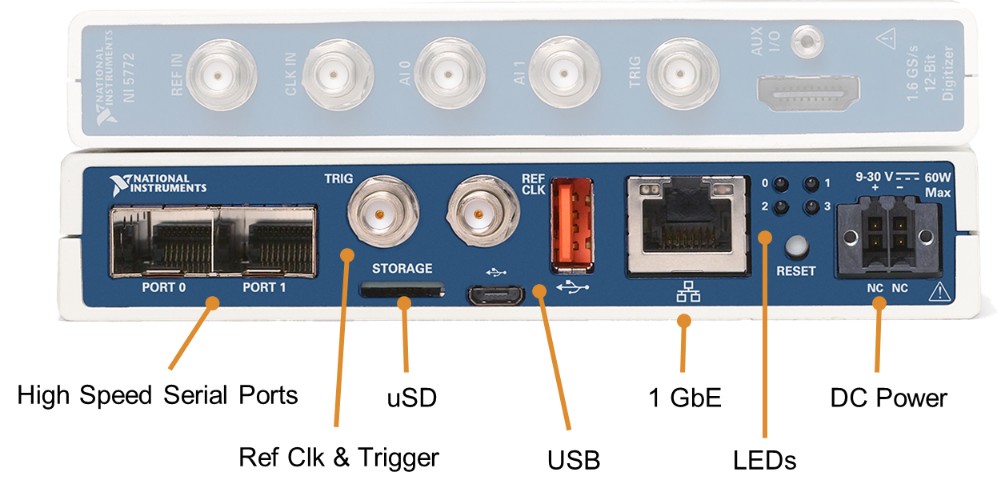

该处理器还具有512 MB的闪存和512 MB的RAM,配有一个1千兆以太网接口、USB 2.0设备和主机接口以及一个µSD卡插槽。所部署应用程序的主要接口应为1千兆以太网,因其支持更大带宽;但USB设备端口可用于设置、配置和诊断。

连接

所有连接都位于同一硬件表面,这使设备更易于集成至更大的系统中。虽然采用模块化I/O,但模拟适配器模块也通过辅助I/O连接器为FPGA提供数字I/O。该控制器适用9 V至30 V的直流电源,因此可由电池供电,从而用作便携式系统。

图9:除FlexRIO适配器模块提供的连接功能外,用于FlexRIO的控制器还具有用于数据传输的行业标准接口、用于时钟和同步的SMA连接器、用于外设通信的USB端口以及用于可视状态显示的LED灯。

除2个USB端口外,所有连接器均可实现电缆加固连接。USB主机端口(橙色)专为高留存而设计,而USB设备端口主要用于诊断。

物理包装

该设备具有铝制外壳,因此无需设计定制机械结构,可在各种场景中提供一致的模拟和热性能,从而更易于集成。还可借助安装套件为设备安全安装前面板。

图10:用于FlexRIO的控制器包装专门针对尺寸、重量和功耗受限的嵌入式应用而设计。

该包装设计还包含多项功能,可确保产品的长期可靠性和适用性。首先,开发人员可使用软件钩来监控FPGA和处理器温度。如果FPGA或处理器温度超过安全限值,设备将自动关闭以防止内部组件损坏。主动冷却由用户可维修的风机提供,可通过软件监控,并随设备温度进行自动调节。在40 ℃时,风机的平均故障间隔时间(MTBF)超过7年。

对于需要考虑冲击、振动、温度或湿度的情况,用于FlexRIO的控制器的额定值与PXI相似,可承受30 g峰值半正弦冲击、5 Hz至500 Hz频率的0.3 grms振动、0 ℃至55 ℃的环境温度和5%到95%的非冷凝湿度。

总结

十多年来,凭借LabVIEW可重配置I/O (RIO)架构和LabVIEW FPGA,快速构建实时运行算法原型的能力一直是NI的一大优势。对于在雷达、频谱监测、通信、工业机械、超声和医学成像技术等领域需要对新技术进行原型验证的工程师和科学家而言,该平台可在产品化或部署过程中最大限度地重用代码,从而加快原型验证的速度。

后续步骤

注册商标Linux®的使用获得了Linus Torvalds专属授权商LMI的再授权,Linus Torvalds拥有Linux®注册商标在全球范围内的所有权。