Camera Link Analyzer for the Camera Link Logging Utility

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report to a Moderator

Products and Environment

This section reflects the products and operating system used to create the example.To download NI software, including the products shown below, visit ni.com/downloads.

- NI-1483

- PCIe-1473

Hardware

Code and Documents

Attachment

Description

Description-Separate-1Overview

This example program shows how you can take data files produced by the Camera Link Logger for Vision-RIO and analyze them with some basic statistics and display. It provides a decompression function to view the data in the time domain or allows for viewing of relative offsets of data. This application is meant to serve as a tool to assist in debugging of Camera Link signal issues. It can be used to help debug triggering problems and camera line problems. This application does not interface with any hardware but reads log files generated from other applications, interpreted as camera link line data. This application was written in LabVIEW 2012.

Required Hardware and Software

Required Software:

- LabVIEW 2012 Run-Time Engine for the executable

- LabVIEW 2012 for the project download

Required Hardware:

- None

Motivation and the Camera Link Logger

This application is coupled with the Camera Link Logger for Vision-RIO. The logger is capable of generating log files which can be read to debug the lines on an NI-1473R or NI-1483R. There is a separate logger for the NI-1433. These log files can be read by this application in order to help debug difficult Camera Link issues.

The Log Files

The log files are simple and come in two parts. The entire log file is encoded in ASCII for readability. The first line of the log file is a space delimited set of integer values which represent the data on the lines at a given moment. The second line represents the number of tick counts on the FPGA that the data lines stayed in that configuration.

Compressed, this file often only reaches a megabyte. However, decompressed it can reach a gigabyte with ease.

The Interface

The interface to the camera link analyzer provides some basic functionality. The display shows compressed data where the x-axis is "changes" in the data and the different lines are shown at different vertical intervals. The zoom and pan functionality is provided by the LabVIEW Control. The user can select a new log file and click the Reload button to load it onto the display. The user can choose to analyze the whole file or only what is being displayed on the screen.

The analyzer is capable of basic edge counting and statistics on the pulse width and frequency of the signals. Synchronization is included but incomplete as of the first release. The ability to display cursors on edges is also included. The user can select a line they wish to analyze and either Rising, Falling or All Edges to analyze. The following Statistic Methods are included:

-

- Pulse width arithmetic mean (ticks)

- Pulse width RMS (ticks)

- Pulse width standard deviation (ticks)

- Pulse width variance (ticks)

- Pulse width median (ticks)

- Pulse width mode (ticks)

- Maximum pulse width (ticks) and index of maximum

- Minimum pulse width (ticks) and index of minimum

- Number of Edges

- Total Time (ticks)

- Frequency (Hz)

These metrics are only applied starting at the beginning of the first edge and going until the last edge. The spaces on either side of the edges on the display will not be taken into account as part of the analysis.

A decompressor is also provided which allows the user to generate a log file where the count is always equal to 1. This turns the time domain into a unit of ticks instead of changes. This will provide a better sense of the actual intervals of the signal. It is not recommended to try to use a large window to view decompressed data. The data becomes extremely large extremely quickly and you will likely run out of memory viewing any more than a few hundred data points.

A Brief Look Under the Hood

The code is provided for all analysis functions. The functions will be reviewed here in brief including all implemented functions and the yet-unimplemented sync analysis functionality.

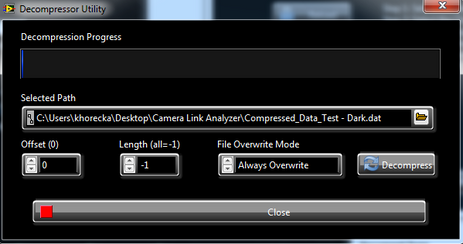

The Decompression Utility

This utility can be accessed by clicking the Decompress File button on the front of the Analyzer. It pops up as a dialog meaning you must complete using it before using the analyzer more.

The utility takes the filename of the compressed file and appends _Decompressed to it. It is extremely simple functionally as it just iterates the number of times in Count and outputs that many data points. It then takes the size of the expanded data and appends a line of ones equal in size.

The decompressor also provides a file overwrite function which determines if we should always overwrite existing files, never overwrite existing files, or prompt the user to decide if needed.

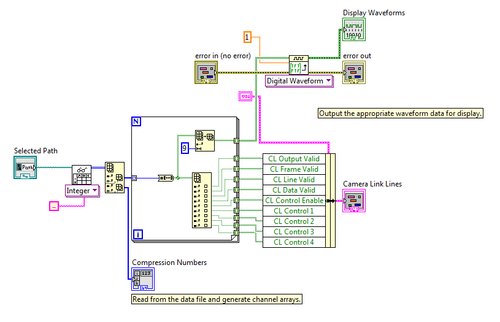

Read from CL Data File VI

This VI provides the functionality to read from our compressed data format and output a cluster of boolean arrays representing the states of the lines. It also outputs an array of compression numbers and a displayable set of digital waveforms.

The CL Digital Analysis Library

This small library provides all the custom digital analysis logic which can be used to gather information about our signals. It provides some helper functions which can be used together to determine all the metrics on the front panel and more. The primary function of concern is the Analyze Channel function. Each function is reviewed in brief here.

Analyze Channel

This is the primary analysis function. It uses the pulse widths at each point on the signal (in ticks) in conjunction with LabVIEWs built in statistic functions to determine all the statistical methods stored on the front panel. It can do this with Rising Edges, Falling Edges or All Edges. The Edge detection functionality is also included.

Edge Counter

The edge counter function performs the basic edge counting for the application. It iterates through the array of booleans, determining the number of times we switch from F->T, T->F and the sum of both. This is used for a great number of analysis functions.

Get Offset Values From Compression Values

This function determines the actual location in time a data point inhabits rather than its relative offset to other data points. This is generated from the Count values and can be used to determine the exact position in time (in ticks) the signal inhabits.

Compute Consecutive Difference

This function finds the pulse width between edges given their locations in time. Note that these functions do not require the data to become decompressed and are, therefore, very efficient memory wise.

Cross Reference Arrays

This function is extremely slow and not used, but provides a general way to cross reference two arrays for identical values. This can be used to determine synchronization in a signal which is not represented in order.

Cross Reference Sorted Arrays

This function is the sorted counterpart to Cross Reference arrays an very efficiently determines the intersection of both arrays. It is based on the set_intersection function in C++.

Find Synced Edges

Although incomplete, this function provides some basic logic which can be used to determine how synchronized two signals are. It can count the number of edges which line up given two signals.

Troubleshooting and Future Work

The basic analysis functions should work quite well on compressed data. If you use decompressed data you are likely to run into performance issues quickly. Note that the cursor functionality should not be used on more than 1000 cursors. They become fairly meaningless at that density and will severely lag your application.

The entire program is read-only in regard to your log files with the exception of the decompressor. This means you are safe to play with the data as you wish without worrying about damaging your test data.

The most obvious future work is the completion of the sync analysis functionality. There are likely many functions which users may find useful one day and all suggestions are very welcome! The goal of the application is to make debugging tricky camera link issues more manageable and to give the user a feeling of control and understanding on a very low level.

Description-Separate-2Example code from the Example Code Exchange in the NI Community is licensed with the MIT license.