PXI 고속 시리얼 계측기 소개

개요

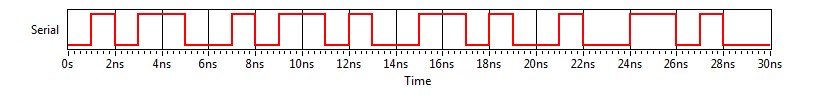

PXI 고속 시리얼 계측기는 엔지니어가 고속 시리얼 프로토콜을 검증, 인터페이스, 테스트하는 데 도움이 됩니다. PXIe-7903 및 PXIe-7902와 같은 일부 고속 시리얼 디바이스는 대용량 데이터 이동과 인라인 리얼타임 신호 처리를 위해 고성능 FPGA 코프로세싱 기능이 필요한 엔지니어를 위해 설계되었습니다. 이 하드웨어에는 Xilinx Kintex™ UltraScale+™ 또는 7 시리즈 FPGA가 있으며, 이를 LabVIEW FPGA Module로 프로그래밍하여 어플리케이션별로 최대한 사용자 정의하고 재사용할 수 있습니다. 이 계측기는 FPGA 멀티기가비트 트랜시버 (MGT)를 활용하여 최대 28.2 Gbps의 라인 속도와 최대 48개의 TX 및 RX 레인을 지원합니다. PXI 플랫폼의 일부로서 PXI 클럭, 트리거링 및 고속 데이터 이동 기능 (디스크 스트리밍, 최대 7 GB/s의 P2P 스트리밍 포함)의 이점을 이용합니다.

내용

고속 시리얼 인터페이스의 등장

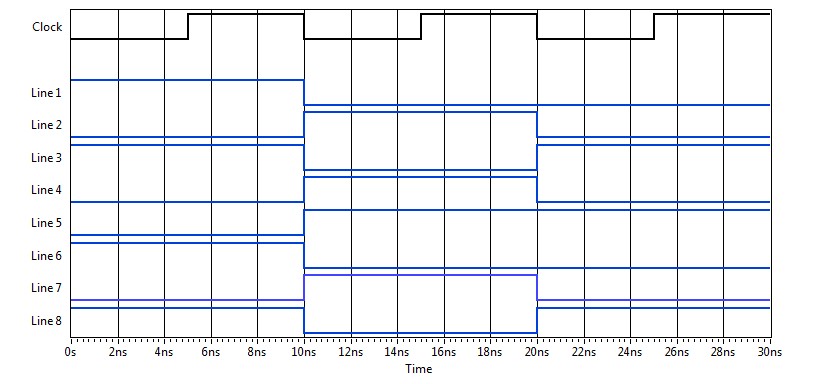

더 높은 데이터 대역폭에 대한 요구가 계속해서 증가함에 따라 유선 인터페이스는 이를 충족하기 위해 클럭 속도를 높이고 병렬 처리를 개선했습니다. 그러나 기존의 병렬 데이터 버스로는 클럭과 데이터 라인 간에 아주 작은 스큐가 발생하는데 이로 인해 인터페이스의 비트 에러 속도를 저해할 수 있습니다. 시리얼 데이터 링크는 주어진 차동 추적 쌍의 데이터 스트림에 클럭을 임베드하여 클럭과 데이터 간에 스큐가 발생할 가능성을 없애 이 문제를 해결합니다. 이 기능을 사용하려면 인터페이스 수신단에 전자 장치를 추가하는 것은 물론 클럭 복구를 위해 추가로 인코딩해야 합니다. 그러나 이렇게 하면 데이터 속도가 비약적으로 높아질 수 있기 때문에 대역폭에 대한 요구가 충족됩니다.

그림 1. 같은 데이터 대역폭에서의 병렬 클럭 (검정색) 및 데이터 (파란색)와 데이터의 임베디드 클럭 (빨간색) 비교.

최신 데이터 통신 프로토콜은 이러한 병렬 인터페이스에서 PCI Express, HDMI, DisplayPort 비디오 표준, IEEE 1394b, USB 3.0 등과 같은 고속 시리얼 인터페이스로 전환되었습니다. 설계와 테스트 엔지니어가 이러한 인터페이스를 검증하는 일은 새로운 과제로 새 테스트 하드웨어가 필요합니다. 지금까지 엔지니어는 고가의 오실로스코프 또는 비트 에러 속도 테스터 (BERT)를 사용하여 물리적 인터페이스를 특성화하고 프로토콜별 분석기와 생성기를 사용하여 프로토콜 스택이 올바르게 구현되었는지, 데이터가 효율적으로 전송되고 수신되는지 검증했습니다. 그러나 자동화된 V&V와 제조 테스트의 경우, 이러한 시리얼 인터페이스를 테스트하는 데 최적화된 하드웨어가 없습니다. 오실로스코프와 비트 에러 속도 테스터는 종종 너무 비싸고 속도가 느려서 범위를 맞출 수 없습니다. 반면 프로토콜별 하드웨어는 자동화된 테스트 시스템에 통합할 수 있을 만큼 융통적이지 않은 경우가 많습니다. 반면에 프로토콜별 하드웨어는 다른 테스트에 재사용하거나 다른 DUT (Device Under Test)에 사용할 수 없습니다.

FPGA는 이러한 문제를 해결할 수 있습니다. 최신 고성능 FPGA에는 일반적으로 여러 MGT가 포함되어 있는데, 이는 다양한 고속 시리얼 인터페이스와 함께 작동합니다. 적절한 프로토콜별 IP, LabVIEW FPGA Module을 통한 그래픽 프로그래밍, PXI 에코시스템의 장점과 결합하면 새로운 고속 시리얼 소프트웨어 설계 계측기가 탄생합니다.

고속 시리얼 모듈

표 1. PXI 고속 시리얼 계측기.

¹8 Gbps와 9.8 Gbps 간에 얻을 수 있는 라인 속도 차이.

²PXIe-7903은 2 슬롯 모듈.

데이터 속도가 높고 아날로그 대역폭이 20 GHz 이상인 어플리케이션에서는 연결과 케이블링이 매우 중요합니다. PXIe-7903, PXIe-7902, PXIe-6594, PXIe-6593, PXIe-6592, PXIe-6591에는 각각 고유한 옵션이 갖춰져 있으며 특정 사용 사례에 맞게 연결을 단순화합니다. 세 모듈 모두 코어에 사용자가 프로그래밍 가능한 Xilinx FPGA가 있습니다.

Xilinx 7 시리즈 GTX 트랜시버는 이러한 계측기의 핵심 기술입니다. 이 트랜시버는 전류 모드 로직 (CML)을 사용합니다. CML은 차동 인터페이스인데, 이 차동 인터페이스는 전력 소비 감소와 방사 방출을 위해 800 mVpp (공칭값 최대 1,000 mVpp)의 작은 신호 스윙과 높은 데이터 속도에서 반사와 그로 인한 신호 이상을 최소화하기 위해 100옴의 차동 (신호 레그당 50옴) 임피던스를 특징으로 합니다. 또한 신호 충실도를 최적화하기 위해 이 트랜시버에는 프로그래밍 가능한 전송 진폭이 포함되어 긴 케이블을 보완할 뿐만 아니라 사전 강조와 사후 강조, 자동 적응형 수신기 균등화를 전송하여 아날로그 채널/케이블 대역폭의 제한을 해제합니다.

모든 고속 시리얼 인터페이스에는 라인 속도의 정수 제수에서 작동하는 참조 클럭이 필요합니다. 최대한 다양하게 활용할 수 있도록 이 GTX 트랜시버에는 참조 클럭을 최대 100배까지 곱하여 시리얼 데이터 속도를 생성할 수 있는 위상 고정 루프 (PLL)가 포함되어 있습니다. 또한 비율이 최대 80X인 시리얼-병렬 변환기를 포함하여 FPGA 클럭 주파수를 제한하면서 시리얼 데이터 속도를 높일 수 있습니다. 또한 트랜시버에는 8b/10b, 64b/66b, 64b/67b 인코딩과 디코딩 구조가 내장되어 있어 클럭을 복구하기에 충분할 만큼 신호를 변환하고 범용 FPGA 리소스를 사용하지 않습니다. Xilinx 7 Series FPGA GTX/GTH Transceivers User Guide를 읽으면 Xilinx GTX 트랜시버의 더 자세한 정보를 확인할 수 있습니다.

계측기의 Xilinx FPGA는 고속 시리얼 트랜시버를 제공하는 것 외에도 몇 가지 중요한 역할을 합니다. 사용 중인 프로토콜의 로직뿐만 아니라 하드웨어 설정과 시스템 전체에 걸친 데이터의 생성, 수신, 이동을 위한 어플리케이션별 사용자 로직을 구현합니다.

그림 2. 주요 인터페이스와 데이터 속도를 갖춘 PXIe-7903 하드웨어 아키텍처.

표 2. PXI 고속 시리얼 계측기 및 각 FPGA의 스펙.

FPGA에 직접 연결된 최대 20 GB의 내장 DDR3 DRAM은 사용자 정의 액세스 패턴에서 최대 25 GB/s (최대 이론값)의 속도로 읽거나 쓸 수 있습니다. 또한 FPGA에는 PCI Express x8 Gen 3 인터페이스가 포함되어 있는데 이를 PXI Express 백플레인에 연결하여 호스트와 디스크 간에 데이터를 스트리밍할 수 있습니다. 또는 단방향의 경우 최대 7 GB/s, 양방향의 경우 최대 2.4 GB/s 속도 (총 4.8 GB/s)로 시스템의 다른 FPGA 지원 디바이스에 P2P 연결이 가능합니다.

지터가 낮고 충실도가 높은 참조 클럭은 모든 고속 시리얼 통신 시스템의 중요한 구성요소입니다. 모든 모듈에는 Xilinx GTX 트랜시버의 전체 범위에 걸쳐 MGT 작동을 지원하는 내장된 모든 속도 대응 신시사이저가 있습니다. 이때 PXIe-6591, PXIe-6592, PXIe-7902는 최대 디바이스 속도까지 500 Mbps~8 Gbps와 9.8 Gbps로 작동하고, PXIe-6593, PXIe-6594, PXIe-7903은 최소 라인 속도와 최대 라인 속도 간에 이러한 간극 없이 작동합니다. PXIe-6591, PXIe-6592, PXIe-6593, PXIe-6594는 전면 패널 동축 연결을 통해 내장된 참조 클럭을 반출할 수 있으며, 4개의 모듈 모두 연결을 통해 외부 참조 클럭을 반입할 수 있습니다. 마지막으로 이 디바이스는 PXI Express 100 MHz 또는 DStarA 백플레인 클럭을 MGT의 참조로 연결할 수 있습니다.

소프트웨어

소프트웨어로 설계된 계측기는 고정 기능 계측기와 같은 기능을 갖췄지만, 사용자가 프로그래밍 가능한 개방형 FPGA를 통해 계측기 하드웨어를 사용자 정의할 수 있습니다. PXI 고속 시리얼 계측기에서 다양한 프로토콜과 어플리케이션을 지원하려면 이러한 사용자 정의가 가능해야 합니다. 따라서 이러한 디바이스를 프로그래밍하기 위한 단일 상위 레벨 API는 없습니다. 대신 LabVIEW 소프트웨어에서 호스트 (CPU)와 FPGA 코드 모두 직접 프로그래밍되며, 하위 레벨 NI-RIO API를 사용하여 이 둘 사이를 연결합니다. 사용자가 신속하게 시작하고 실행할 수 있도록 다양한 예제를 통해 여러 프로토콜의 사용법과 이러한 계측기의 다양한 사용 모델을 설명합니다.

개방형 FPGA를 통해 다른 계측기에서는 불가능한 수준으로 사용자 정의가 가능합니다. 가장 먼저, 계측기가 설정된 시리얼 프로토콜을 구현합니다. 이것만으로도 PXIe-7903, PXIe-7902, PXIe-6594, PXIe-6593, PXIe-6592, PXIe-6591은 다양한 표준 시리얼 프로토콜과 사용자 정의 시리얼 프로토콜을 지원할 수 있습니다. 프로토콜뿐만 아니라 사용자 정의 하드웨어 기능을 통해 이전에는 불가능했던 유형의 테스트가 가능합니다. 예를 들어, FPGA에서 알고리즘 데이터를 생성하면 이러한 웨이브폼을 다운로드하는 데 필요한 웨이브폼 저장 메모리와 시스템 대역폭이 줄어들어 테스트 처리 속도가 빨라집니다. 응답 비교, 지능형 트리거링, 데이터 축소 및 압축과 같은 알고리즘 데이터 분석에서 호스트 CPU가 처리해야 할 데이터 양이 크게 줄어 테스트 시간 또한 단축됩니다.

사용자 정의된 DRAM 액세스를 통해 DRAM이 자극 영역과 응답 영역으로 분할되는 방식을 다양하게 선택할 수 있습니다. 또한 사용자 정의 압축과 압축 해제 알고리즘을 활성화하여 DRAM의 크기와 대역폭을 최적화할 수 있습니다. 표준 웨이브폼의 캡처와 재생도 가능하지만, 프로토콜, 라인 속도, 레인 수에 따라 I/O 대역폭이 DRAM 대역폭을 초과할 수 있습니다. 마지막으로 고속 시리얼 계측기와 호스트 또는 다른 계측기 간에 사용자 정의 데이터를 이동할 수 있어 매우 다양한 방식으로 시스템 레벨로 통합할 수 있습니다. 예를 들어, 고속 디지타이저를 사용하여 아날로그 데이터를 디지털 샘플로 변환하고, NI P2P 스트리밍을 사용하여 해당 데이터를 최대 7 GB/s의 속도로 고속 시리얼 계측기로 전송한 다음 해당 디지털 샘플을 시리얼 프로토콜을 통해 외부 디바이스에 전송할 수 있습니다. 또는 고속 시리얼 계측기에서 시리얼 데이터 스트림을 캡처한 후 이를 호스트 CPU와 궁극적으로 고대역폭 RAID 배열로 전송하여 최대 7 GB/s의 속도로 몇 시간 또는 며칠 간 연속으로 저장합니다.

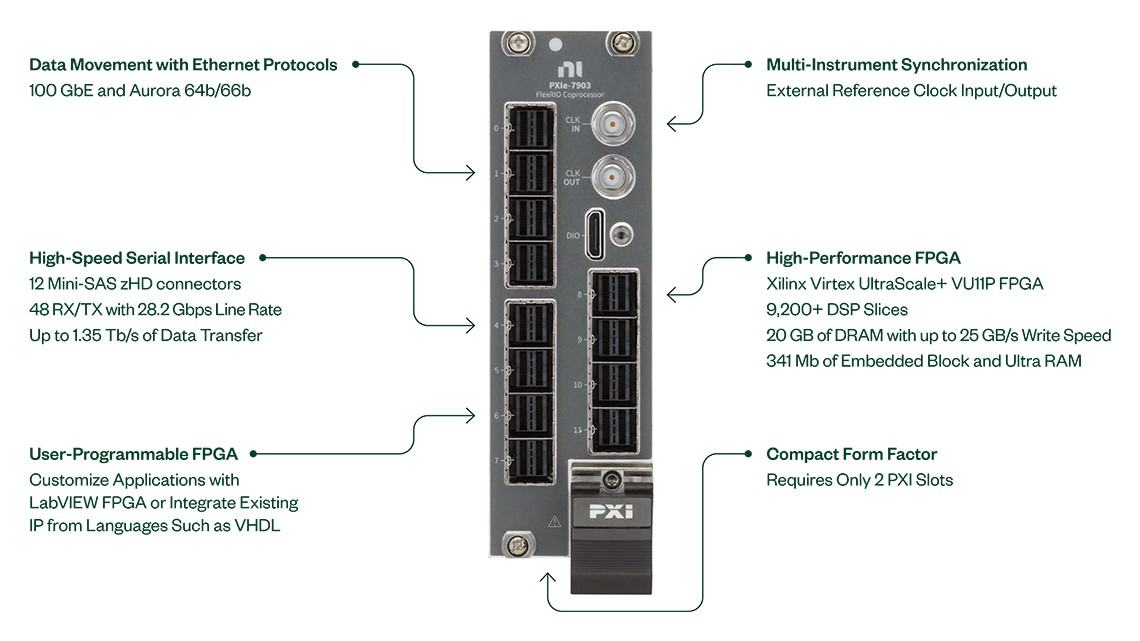

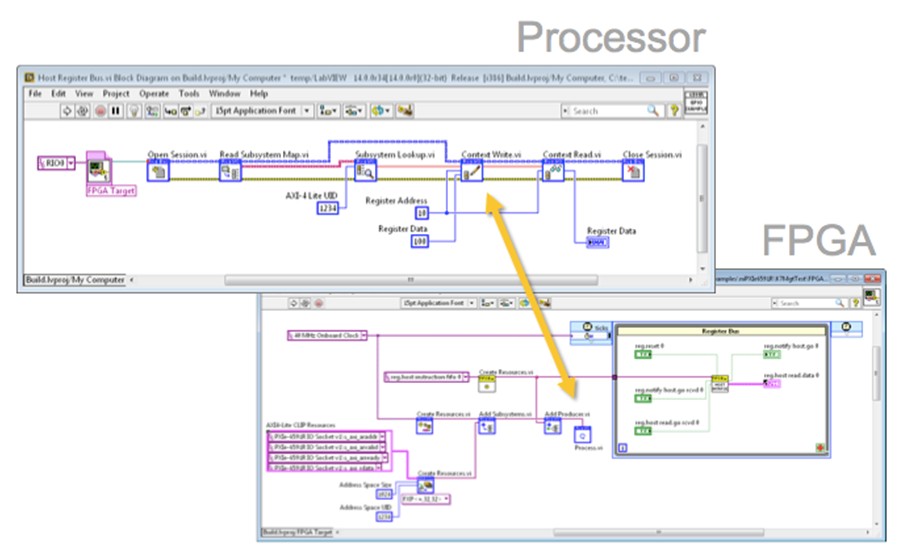

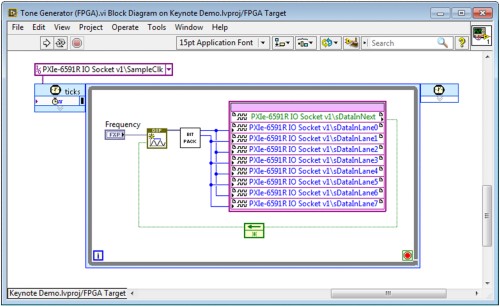

LabVIEW FPGA를 사용하면 이러한 고속 시리얼 계측기를 손쉽게 설정하고 프로그래밍할 수 있습니다. 그림 3은 대표적인 코드와 함께 LabVIEW를 통해 이용할 수 있는 주요 인터페이스를 보여줍니다. LabVIEW FPGA와 NI-RIO API로 레지스터 읽기 쓰기뿐만 아니라 양방향 DMA 전송 등 호스트 CPU와 FPGA 간의 PCI Express 기반 데이터 전송을 위한 효율적인 메커니즘을 얻을 수 있습니다. DRAM 액세스는 일반적으로 하위 레벨 하드웨어 기술 언어 (HDL)에서 관리하기 어려운 인터페이스로, 추상화된 요청, 읽기, 쓰기 인터페이스를 통해 단순화되는 동시에 높은 처리량을 유지하고 기본 읽기/쓰기 중재가 가능합니다. GTX 트랜시버 설정은 일반적으로 프로토콜에 따라 다르며 트랜시버 설정이 내장된 많은 고속 시리얼 인터페이스 (HDL 또는 넷리스트)에 IP가 이미 있습니다. 이 시리얼 프로토콜 인터페이스는 소켓 구성요소 레벨 IP (CLIP) 인터페이스를 통해 LabVIEW FPGA에 공개됩니다. CLIP 노드를 사용하면 LabVIEW에서 구현되지 않은 코드의 비동기화 작업이 가능하지만, LabVIEW FPGA 다이어그램에 대해 잘 정의된 인터페이스가 있습니다. 일반적인 시나리오에서는 Xilinx Vivado IP 카탈로그의 Xilinx 프로토콜별 IP (트랜시버 설정 포함)와 VHDL의 얇은 계층을 사용하여 LabVIEW FPGA에 대한 인터페이스를 정의합니다. 프로토콜이 구현되면 LabVIEW FPGA에서는 의사 결정, 상태 머신 구현, DUT 제어, 신호 처리, 데이터 이동과 같은 임의의 사용자 로직을 구현할 수 있는 다양한 언어를 제공합니다.

그림 3. LabVIEW FPGA는 PXI 고속 시리얼 계측기에서 사용자가 프로그래밍 가능한 FPGA의 주요 측면을 그래픽으로 설명합니다.

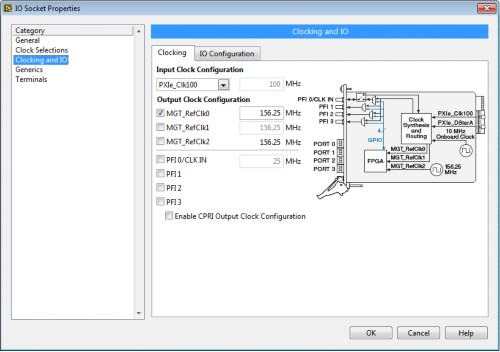

LabVIEW는 사용자가 프로그래밍 가능한 FPGA에서 구현할 로직을 정의하는 것 외에도 프로젝트 계층구조와 관련 설정 페이지를 통해 하드웨어 설정을 단순화합니다. 예를 들어, 이러한 고속 시리얼 계측기의 참조 클럭 설정에는 FPGA의 전원을 켤 때 이러한 레지스터를 적용하는 데 필요한 로직 이외에 많게는 4개의 개별적인 집적 회로에 적용할 수백 개의 레지스터 설정을 결정하는 복잡한 알고리즘이 필요합니다. LabVIEW FPGA는 유효한 설정을 강제 적용하기 위한 설계 규칙 및 지침과 함께 옵션을 그래픽으로 표현한 대화 상자로 이를 나타냅니다. 이 방식을 통해 모든 속도의 클럭 신시사이저와 라우팅 회로의 구성을 몇 시간 또는 며칠이 아닌 몇 분이 걸리는 작업으로 단순화할 수 있습니다.

그림 4. LabVIEW FPGA에서 제공되는 직관적인 그래픽 인터페이스로 클럭을 설정하면 복잡한 프로세스를 단순화할 수 있습니다.

PXI 고속 시리얼 계측기는 코드를 재사용하고 일반 태스크를 단순화할 수 있는 특정 계측기 설계 라이브러리를 지원합니다. 이 라이브러리는 서로 작동하고 일반 기능을 제공하는 LabVIEW 인터페이스를 갖춘 호스트와 FPGA 코드 라이브러리입니다. 명령 프레임워크는 런타임 중 다이나믹 하드웨어 설정을 위한 계측기 설계 라이브러리입니다. 이러한 시리얼 계측기의 하드웨어 기능 (예를 들어, 클럭 설정) 대부분을 LabVIEW 프로젝트에서 정적으로 설정할 수 있지만, 사용자는 명령 프레임워크를 활용하여 어플리케이션별 펌웨어 파라미터를 컨트롤할 수 있습니다. 예를 들어, 명령 프레임워크는 일반적으로 Xilinx 시리얼 프로토콜 IP에서 볼 수 있는 FPGA의 AXI-4 Lite 인터페이스를 통해 표시되는 레지스터 설정의 호스트 설정을 단순화합니다.

그림 5. AXI-4 Lite 인터페이스를 통해 레지스터를 쓰고 읽는 프로세서와 FPGA 코드.

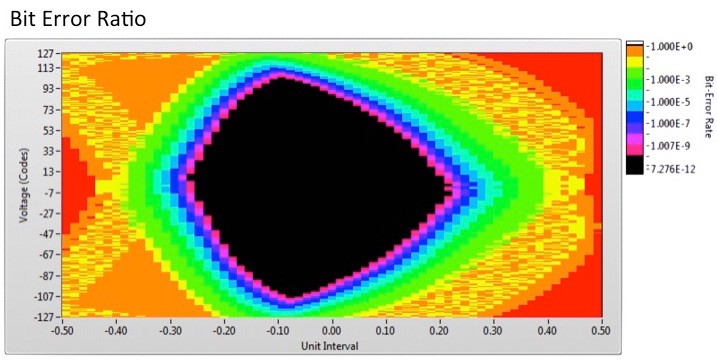

명령 프레임워크를 기반으로 구축된 아이 스캔 계측기 설계 라이브러리를 통해 고속 시리얼 수신 채널을 디버그할 수 있습니다. Xilinx GTX 트랜시버에는 채널당 두 개의 수신기 비교기가 있습니다. 둘 중 하나의 비교기는 복구된 클럭 주파수와 위상에 따라 자동으로 시리얼 아이의 중심을 추적하고 나머지 비교기는 진폭과 위상에서 독립적으로 이동할 수 있습니다. 아이 스캔 계측기 설계 라이브러리는 뒤에 언급한 비교기의 파라미터를 변경하고 그 결과를 먼저 언급한 비교기의 파라미터와 비교하여 Xilinx GTX 트랜시버의 비트 에러 속도 플로어에 정확히 맞는 인터페이스의 링크 여백을 결정하는 데 유용한 통계적 아이 다이어그램을 생성할 수 있습니다. 또한 아이 스캔 계측기 설계 라이브러리는 독립적인 하드웨어 리소스 세트를 사용하기 때문에 다른 프로토콜 IP와 공존 가능하며 다른 어플리케이션별 기능과 동시에 실행할 수 있습니다.

그림 6. LabVIEW Instrument Design Libraries for PXI High-Speed Serial Instruments에는 루프백 설정을 사용하여 통계적 아이 스캔을 수행하기 위한 참조 설계가 포함되어 있습니다.

이러한 계측기 설계 라이브러리 외에도 다른 NI 소프트웨어로 설계된 계측기를 통해 DRAM 기반 수집과 생성뿐만 아니라 멀티 레코드와 같은 다양하고 유용한 기능을 위한 라이브러리를 이용할 수 있습니다. PXIe-7903, PXIe-7902, PXIe-6594, PXIe-6593, PXIe-6592, PXIe-6591에서 공식적으로 지원되거나 테스트되지는 않았지만, 계측기 설계 라이브러리의 하드웨어 독립성(Hardware Agnosticism)에 따라 PXI 고속 시리얼 계측기에서도 사용될 수 있습니다.

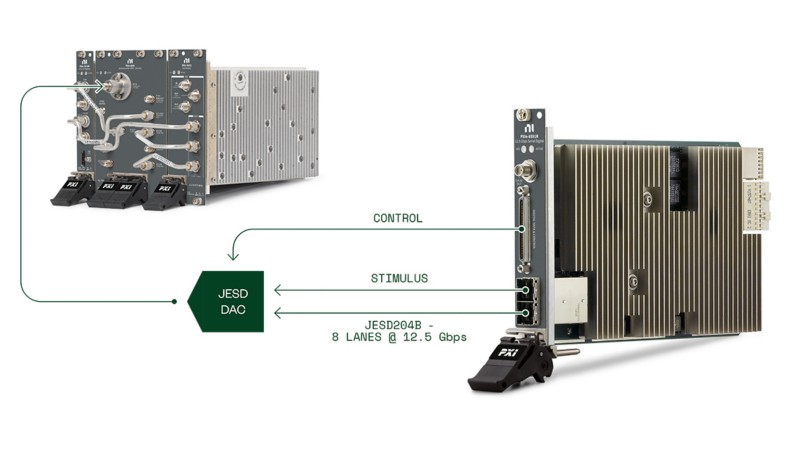

그림 7. 엔지니어는 DSP 계측기 설계 라이브러리를 사용하여 시리얼 JESD204B 프로토콜을 통해 디지털-아날로그 변환기로 전송할 사인파를 합성할 수 있습니다.

프로토콜

PXI 고속 시리얼 계측기의 Xilinx GTX 트랜시버는 다양한 프로토콜을 지원합니다. NI는 여러 어플리케이션 패턴의 LabVIEW 아키텍처뿐만 아니라 일반적인 프로토콜의 통합 방법을 보여주는 여러 소프트웨어 예제를 제공합니다. 각 예제는 관련 소스 코드 및 프로토콜 IP와 함께 지원되는 계측기에 따라 미리 컴파일된 FPGA 비트 파일과 함께 제공됩니다. 이 코드를 최종 어플리케이션에 맞게 수정해야 하는 경우 특정 프로토콜에서는 FPGA를 다시 컴파일하는데 Xilinx의 IP 라이센스가 필요합니다. 이 프로토콜 IP는 Xilinx 또는 Avnet이나 DigiKey와 같은 리셀러를 통해 구입할 수 있습니다.

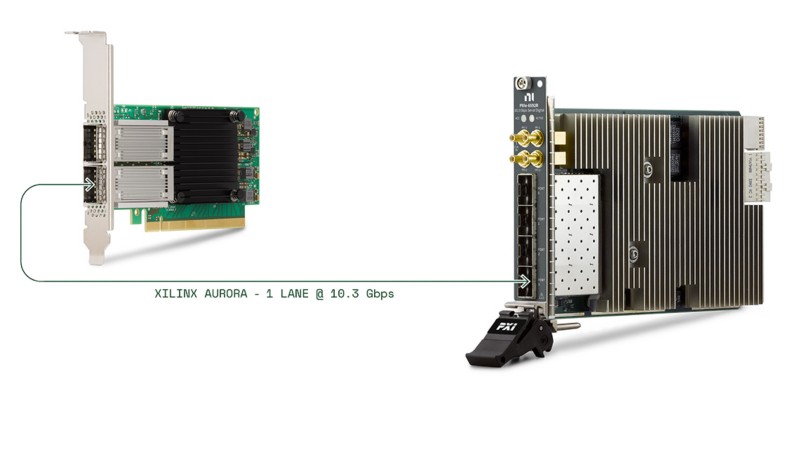

Xilinx Aurora

Xilinx Aurora는 포인트 간 시리얼 인터페이스용으로 설계된 프로토콜로, 설치 공간이 작고 가벼우며 지연 시간이 짧습니다. Xilinx GTX 시리얼 트랜시버의 최대 속도와 더 큰 대역폭을 위한 레인 본딩을 지원합니다. Aurora는 주로 고대역폭 데이터 이동을 위해 설계되었으며, 흐름 제어, 유연한 프레이밍, 단방향 또는 전이중 채널의 옵션을 제공합니다. Xilinx Aurora에 대한 자세한 정보는 다음 링크를 참조하십시오.

http://www.xilinx.com/products/design_resources/conn_central/grouping/aurora.htm

Instrument Design Libraries for High Speed Serial Instruments 드라이버를 통해 Aurora 64b66b의 샘플 프로젝트 참조 설계를 설치하게 되며, NI에는 Aurora 8b10b의 웹 예제가 있습니다.

JESD204B 및 JESD204C

무선 광대역 변조 디지털 전송의 필요성이 대두되면서 이를 해결하기 위해 아날로그-디지털 변환기 (ADC)와 디지털-아날로그 변환기 (DAC) 샘플링 속도와 분해능이 증가함에 따라 이러한 변환기를 오가는 데이터 속도가 증가했습니다. 기존의 병렬 클럭과 데이터 인터페이스로는 집적 회로 핀이 더 많이 필요하고 허용오차도 더 엄격해야 합니다. JESD204B와 JESD204C는 이러한 인터페이스를 고속 시리얼로 전환하여 이러한 문제를 해결합니다. 고속 시리얼은 지연 시간이 짧고 데이터 대역폭은 높아 멀티 변환기를 손쉽게 동기화할 수 있습니다. JESD204B는 최신 고대역폭, 고속, 채널 수가 많은 ADC와 DAC에 맞게 최대 12.5 Gbps로 32 레인을 지원합니다. JESD204C는 최대 32 Gbps의 속도를 지원합니다. JESD204B는 8B/10B 코딩을 사용하는 반면 JESD204C는 8B/10B, 64B/66B, 64B/80B를 지원합니다.

10 기가비트 이더넷

10 기가비트 이더넷 (10 GbE)은 10.3125 Gbps의 라인 속도에서 대략 1 GB/s의 실제 대역폭을 제공합니다. 10 기가비트 이더넷 인터페이스의 대부분은 8P8C/RJ45 기반 인터페이스를 갖춘 광학 또는 SFP+ 직접 연결 (구리)입니다. PXIe-6592의 10 기가비트 이더넷 예제는 Xilinx 10 기가비트 이더넷 PCS/PMA IP 코어와 OpenCores.org 10 기가비트 이더넷 미디어 액세스 컨트롤러를 사용하여 10GBASE-SR, 10GBASE-LR, 10GBASE-ER 광학 인터페이스와 SFP+ 직접 연결을 지원합니다. 이 MAC/PHY 솔루션 위에 LabVIEW FPGA로 구현된 경량 UDP 스택이 있습니다. 10 기가비트 이더넷 IP 코어에 대한 자세한 정보는 다음 링크에서 찾을 수 있습니다.

https://www.xilinx.com/products/intellectual-property/10gbase-r.html

Instrument Design Libraries for PXI High-Speed Serial Instruments 드라이버를 통해 1 GbE와 10 GbE 모두의 샘플 프로젝트 참조 설계를 설치하게 됩니다.

100 기가비트 이더넷

100 기가비트 이더넷 (100 GbE)은 초당 100 기가비트 (Gbit/s)의 속도로 이더넷 프레임을 전송할 수 있습니다. 이는 10 기가비트 이더넷보다 훨씬 빠른 속도입니다. 100 GbE는 다양한 광학 및 전기 인터페이스와 여러 개의 광섬유 가닥을 제공합니다. 주요 인터페이스로는 100GBASE-KR2, 100GBASE-CR2, QSFP28이 있습니다.

LabVIEW FPGA는 100 GbE의 예제와 함께 제공됩니다.

CPRI

CPRI는 무선 장비 컨트롤 (REC)과 일반적으로 원격 무선 헤드 (RRH)로 알려진 무선 장비 (RE) 간의 광학 인터페이스를 정의합니다. 무선 헤드 설정과 동기화는 물론 디지털 I/Q (기저대역) 데이터 스트리밍이 간단해집니다. Xilinx CPRI IP 코어에 대한 자세한 정보는 다음 링크를 참조하십시오.

https://www.xilinx.com/products/intellectual-property/do-di-cpri.html

시리얼 RapidIO

시리얼 RapidIO는 통신 인프라, 군사 및 항공우주 임베디드 컴퓨팅, 고대역폭 생명 과학 디바이스, 산업 제어와 같은 에너지 효율적인 임베디드 시스템에 최적화된 고성능 시리얼 상호연결 프로토콜입니다. 최대 6.25 Gbps의 속도, 4개의 레인 본딩, 짧은 지연 시간, 흐름 제어, 순서대로 패킷 전달, 상대적으로 작은 설치 공간이 특징입니다. Xilinx Serial RapidIO IP 코어에 대한 자세한 정보는 다음 링크를 참조하십시오.

http://www.xilinx.com/products/intellectual-property/ef-di-srio.html

PXIe-6592용 시리얼 RapidIO의 참조 설계는 NI 커뮤니티에서 찾을 수 있습니다. x2보다 SRIO 인터페이스가 큰 경우, NI에서는 PXIe-6591을 권장합니다.

추가 프로토콜

위의 예제는 PXI 고속 시리얼 계측기와 호환되는 모든 프로토콜의 전체 리스트가 아닙니다. 특정 프로토콜, 위 예제의 사용자 정의, 사용자 정의 또는 독점 프로토콜 통합과 관련된 질문은 현지 NI 영업 엔지니어에게 문의하십시오.

예제 어플리케이션

PXI 고속 시리얼 계측기의 아키텍처는 유연하여 각각 다른 데이터 이동 패턴, 시리얼 프로토콜, 소프트웨어 기능을 활용하는 다양한 사용 사례에 대응할 수 있습니다.

프로토콜 기능 테스트

PXI 고속 시리얼 계측기는 일반적으로 주어진 DUT에서 프로토콜별 기능을 테스트하는 데 사용됩니다. 이 테스트는 DUT가 시리얼 프로토콜을 통해 "외부 세계"와 안정적으로 통신할 수 있는지 확인하기 위해 설계되었습니다. 이러한 테스트는 DUT의 레지스터를 쓰고 다시 읽거나 데이터 처리량과 지연 시간 벤치마크를 수행하거나 다른 프로토콜별 속성 또는 내장 테스트 모드를 실행할 수 있습니다. 또한 응답 타임아웃, 주입된 에러 또는 무시된 흐름 제어 명령 등 결함 시나리오에 DUT가 어떻게 반응하는지 테스트할 수도 있습니다. 관련 태스크에는 링크 비트 에러 속도 측정, 최대 및 최소 라인 속도와 같은 물리적 계층 스트레스 테스트, 번인 테스트는 물론 계측기가 FPGA에서 분석, 사용자 정의 트리거링, 데이터 캡처를 수행하는 버스 스누핑도 포함됩니다.

DUT 컨트롤, 자극, 응답

PXI 고속 시리얼 계측기의 또 다른 일반적인 사용 사례는 DUT 컨트롤, 자극, 응답 캡쳐입니다. 이 시나리오에서 계측기는 고속 시리얼 프로토콜을 직접 테스트하지 않고, 디바이스의 다른 측면을 테스트할 수 있도록 고속 시리얼 프로토콜을 사용하여 DUT에서 데이터를 보내거나 받습니다. 또한 보조 디지털 I/O를 사용하면 SPI와 같은 병렬 또는 저속 시리얼 프로토콜을 사용하여 DUT를 컨트롤할 수 있습니다.

다음 예제에서는 PXIe-6591에서 JESD204B 프로토콜을 사용하여 DAC를 자극하여 DAC의 아날로그 출력 특성을 테스트합니다.

그림 8. 많은 최신 고성능 DAC와 ADC에 JESD204B 고속 시리얼 프로토콜을 사용한 통신이 포함되어 있습니다.

고대역폭 데이터 이동

많은 고성능 임베디드 어플리케이션에서 PXI 플랫폼의 장점을 활용할 수 있으며, 타사 하드웨어와 NI PXI 디바이스 간의 저지연 고대역폭 데이터 이동이 필요합니다. 이러한 어플리케이션은 PXI 고속 시리얼 계측기를 통해 LabVIEW FPGA 하드웨어 처리, PXI Express 계측기로의 P2P 데이터 스트리밍, 디스크로의 고대역폭 스트리밍과 같은 이점을 얻을 수 있는 동시에 표준 고속 시리얼 프로토콜을 통해 고대역폭으로 외부 디바이스에 연결할 수 있습니다.

다음 예제에서 NI 오실로스코프는 아날로그 신호를 샘플링한 후 P2P 데이터 스트리밍을 사용하여 디지털화된 원시 데이터를 PXIe-6592 고속 시리얼 계측기로 보냅니다. 계측기는 LabVIEW FPGA에 구현된 알고리즘을 사용하여 실시간으로 데이터를 처리합니다. 마지막으로 FPGA 간 시리얼 통신용으로 설계된 경량 Xilinx Aurora 프로토콜을 사용하여 처리된 데이터를 타사 디바이스로 전송합니다.

그림 9. PXI 고속 시리얼 계측기는 타사 디바이스로의 저지연 고대역폭 데이터 이동에 적합한 솔루션입니다.

디버그 및 파라미터 테스트 링크

고속 시리얼 인터페이스는 주파수가 매우 높은 신호를 사용하기 때문에 신호 무결성이 나쁘면 통신이 중단될 수 있습니다. 이러한 문제가 발생하면 디버깅 도구를 사용하여 링크 상태와 관련된 유용한 정보를 얻을 수 있습니다. 앞에서 설명한 아이 스캔 계측기 설계 라이브러리를 사용하면 설계자는 수신된 신호의 링크 여백을 확인하고 통신에서 발생한 문제가 신호 무결성이 낮기 때문인지 식별할 수 있습니다. 이 기능은 주로 어플리케이션 개발 중 디버깅을 하기 위해 설계되었지만, 디바이스별 성능 파라미터와 관련된 인사이트를 얻기 위해 디바이스 검증 또는 제조 테스트에도 사용할 수 있습니다. 그러나 PXI 고속 시리얼 계측기를 통해 진폭과 타이밍 정확도의 공칭값을 얻을 수 있으며, NI는 이러한 파라미터에 대해 성능 또는 추적성을 보장하지 않습니다. 특정 어플리케이션에서는 현장 교정 또는 조정이 옵션으로 제공될 수 있습니다.

다른 파라미터 테스트에는 특정 프로토콜 대신 업계 표준 패턴 (PRBS-7, PRBS-15, PRBS-23, PRBS-31)을 사용하는 잘 알려진 유사난수 비트 시퀀스 (PRBS)의 비트 에러 속도가 포함됩니다. 송신기와 수신기의 라인 속도를 변경하여 특정 DUT에 지원되는 비트 속도의 범위를 결정할 수 있습니다. 마지막으로, 자동 게인 제어와 동적 균등화를 포함하여 수신기 민감도를 테스트하기 위해 송신기 진폭과 사전 강조 및 사후 강조를 변경할 수 있습니다.

PXIe-6591과 PXIe-6592의 경우, NI 커뮤니티의 다음 링크에서 추가 리소스를 찾을 수 있습니다. PXI 고속 시리얼 계측기와 함께 사용할 수 있는 물리적 계층 분석 도구가 더 많이 필요한 경우 NI 커뮤니티의 NI MGT Debug Tool을 참조하십시오. PXIe-6593과 PXIe-6594의 경우, PXIe-6593과 PXIe-6594 고속 시리얼 디바이스에서 아이 스캔 사용하기를 참조하십시오.

필수 보유 기술

LabVIEW와 LabVIEW FPGA는 고속 시리얼 기술을 구현하는 작업을 크게 단순화하지만, PXI 고속 시리얼 계측기를 제대로 프로그래밍하려면 특정 전문 지식이 반드시 필요합니다. LabVIEW로 설계되었기 때문에 LabVIEW 그래픽 프로그래밍에 익숙해져야 합니다. ni.com의 NI LabVIEW 어플리케이션 개발 교육과정 페이지에서 도움을 받으실 수 있습니다. 또한 LabVIEW FPGA에서 비프로토콜 FPGA 로직을 사용자 정의하려면 처리량이 높은 LabVIEW FPGA 프로그래밍을 자세히 이해해야 합니다. 자세한 내용은NI LabVIEW High-Performance FPGA Developer's Guide를 참조하십시오. 기존 IP 또는 예제가 있는 프로토콜의 경우 프로토콜 IP와 LabVIEW FPGA 다이어그램 간의 인터페이스를 정의하려면 VHDL 관련 지식과 경험이 필요합니다. 마지막으로 새 프로토콜 또는 사용자 정의 프로토콜을 구현하려면 고급 디지털 설계 전문 지식을 습득하는 것이 좋습니다. 일부 NI 파트너는 사내에 이러한 지식을 갖춘 직원이 없는 경우 지원을 제안합니다. 현지 NI 영업 담당자가 적절한 파트너를 찾는 데 도움을 드릴 수 있습니다.

표 4. 고속 시리얼 계측기를 프로그래밍하려면 인터페이스에 필요한 변경 수준에 따라 다양한 기술과 도구가 필요합니다.

다음 단계

- NI PXI 고속 시리얼 모듈을 사용한 데이터 이동과 신호 처리 최대화에 대해 자세히 알아보십시오.

- 고속 시리얼 통신 링크의 기본 개념에 대해 자세히 알아보십시오.

- 무선 트랜시버용 기능 테스트 시스템에 고속 시리얼 프로토콜을 구현하는 데 도움이 되는 예제 참조 설계를 확인하십시오.

- 소프트웨어로 설계된 계측기용 예제 및 IP와 NI FlexRIO 커뮤니티에서 하드웨어 드라이버에 포함되지 않은 추가 프로토콜 참조 설계를 얻으십시오.

- PXI 고속 시리얼 계측기 구매하기.

- PXI 시스템 구축하기.

|  |  |  |  |  | |

| 스펙 | PXIe-6591 | PXIe-6592 | PXIe-6593 | PXIe-6594 | PXIe-7902 | PXIe-79032 |

| 라인 속도 | 500 Mbps–12.5 Gbps¹ | 500 Mbps–10.3125 Gbps¹ | 500 Mbps–16.3 Gbps | 500 Mbps–28.2 Gbps | 500 Mbps–12.5 Gbps | 500 Mbps–28.2 Gbps |

| 채널 | 8 TX/RX | 4 TX/RX | 8 TX/RX | 8 TX/RX | 24 TX/RX | 48 TX/RX |

| FPGA | Kintex 7 K410T | Kintex 7 K410T | Kintex UltraScale KU040, KU060 | Kintex UltraScale+ KU15P | Virtex™ 7 485T | Virtex UltraScale+ XCVU11P |

| DRAM | 2 GB | 2 GB | 4 GB | 8 GB | 2 GB | 20 GB |

| 호스트 스트리밍 BW | 3.2 GB/s | 3.2 GB/s | 7 GB/s | 7 GB/s | 3.2 GB/s | 7 GB/s |

| 커넥터 | Mini-SAS HD | SFP+ | QSFP28 | QSFP28 | Mini-SAS HD | Mini-SAS HD |

| 케이블 연결 옵션 | 구리 또는 광학 | 구리 또는 광학 | 구리 또는 광학 | 구리 또는 광학 | 구리 또는 광학 | 구리 또는 광학 |

| 보조 DIO | 20 SE | 4 SE | 8 GPIO | 8 GPIO | 해당 사항 없음 | 8 GPIO |

| 스펙 | FPGA | LUT | DSP 슬라이스 | 임베디드 블록 RAM |

| PXIe-6591 | Kintex-7 K410T | 254,200 | 1,540 | 28 Mb |

| PXIe-6592 | Kintex-7 K410T | 254,200 | 1,540 | 28 Mb |

| PXIe-6593 | Kintex UltraScale KU040 | 242,400 | 1,920 | 21.1 Mb |

| Kintex UltraScale KU060 | 331,680 | 2,760 | 38 Mb | |

| PXIe-6594 | Kintex UltraScale+ KU15P | 523,000 | 1,968 | 34.6 Mb |

| PXIe-7902 | Virtex-7 485T | 303,600 | 2,800 | 37 Mb |

| PXIe-7903 | Virtex UltraScale+ XCVU11P | 2,835,000 | 9,216 | 341 Mb |

| 모델 사용 | LabVIEW | 높은 처리량 LabVIEW FPGA | VHDL | 광범위한 디지털 설계 전문성 |

| 기존 특성 사용 | — | — | — | |

| 프로토콜이 아닌 FPGA 코드 사용자 정의 | — | — | ||

| 기존 프로토콜 통합 | — | |||

| 새 프로토콜 또는 사용자 정의 프로토콜 구현 |