NI VeriStand를 위한 FPGA 기반 I/O 생성하기

개요

내용

- FPGA 기반 I/O 인터페이스란?

- 리얼타임 테스트 어플리케이션에 FPGA를 사용하는 이유?

- 직접 구성한 FPGA I/O를 NI VeriStand에서 실행하는 방법

- NI VeriStand FPGA 아키텍처

- 다음 단계

FPGA 기반 I/O 인터페이스란?

FPGA는 ASIC (application specific integrated circuits)와 같은 하드웨어 로직의 실행 성능과 신뢰성을 소프트웨어/펌웨어 기반의 유연성을 동시에 제공하는 프로그래밍 가능한 실리콘 칩입니다. 구성가능한 로직 블록과 프로그래밍 가능한 라우팅 리소스를 사용하면 디바이스를 물리적으로 변경할 필요없이 맞춤 하드웨어 기능을 실행하도록 FPGA를 구현할 수 있습니다. 사용자는 소프트웨어에서 디지털 연산 태스크를 개발한 후, FPGA의 로직과 라우팅 컴포넌트가 어떻게 구성되고 연결되는지에 대한 정보가 담긴 비트스트림 파일로 컴파일합니다.

리얼타임 테스트 어플리케이션에 FPGA를 사용하는 이유?

사용자 정의된 FPGA 기반 I/O 인터페이스를 사용하면, 사용자 어플리케이션의 요구를 정확하게 만족하는 통합된 신호 처리, 시뮬레이션, 트리거링, 컨트롤 태스크를 실행하는 I/O 디바이스를 직접 구축할 수 있습니다. 또한 I/O 인터페이스는 FPGA 기반이므로 조건이 새롭게 변경되었을 경우 하드웨어 변경없이 인터페이스의 특성이나 동작을 편리하게 재구성할 수 있습니다.

맞춤구성 가능한 I/O는 리얼타임 테스트 어플리케이션에서 FPGA를 사용하는 가장 일반적인 이유입니다. 어플리케이션에 특화된 100개 이상의 NI C 시리즈 모듈과 FPGA 기반 I/O 디바이스의 유연성을 통합하면, 리얼타임 테스트 어플리케이션의 요구를 정확하게 충족하도록 맞춤 타이밍과 트리거링 기능이 있는 I/O 인터페이스를 신속하게 구축할 수 있습니다.

또한 데이터 전/후 처리를 위해 FPGA를 활용하면 리얼타임 테스트 어플리케이션에서의 프로세서의 로드를 줄일 수 있습니다. 예를 들어 FPGA는 엔코더에서 수집된 디지털 펄스 데이터를 리얼타임 테스트 어플리케이션에 전달하기 전에 신호의 속도와 가속도를 계산합니다.

또한 FPGA를 통해 고속 폐루프 컨트롤을 추가할 수도 있습니다. 예를 들어, 리얼타임 테스트 어플리케이션의 FPGA에 모션 컨트롤러를 실행하여 컨트롤러 설정값을 제공할 수 있습니다. 그렇게 되면 폐루프 컨트롤이 더욱 신속하게 응답하므로 시스템에 대한 더욱 정확한 컨트롤을 제공하게 됩니다. 이 방식의 한 가지 예로는 브러시리스 DC 모터 컨트롤을 들 수 있습니다.

또한 FPGA를 통해 HIL 테스터 구현 시 다양한 센서를 시뮬레이션할 수 있습니다. FPGA는 무엇보다 정확한 타이밍 요구사항이 있는 여러 센서 유형에 적응할 수 있으므로 센서 시뮬레이션에 이상적입니다. 나노초 분해능으로 센서 시뮬레이션을 구현하여 센서 응답 신호를 더욱 사실적으로 시뮬레이션할 수 있습니다. 대부분의 경우 센서들은 서로 다른 응답 속도로 독립적으로 작동합니다. FPGA는 물리적 병렬 처리 덕분에 이러한 구성요소의 실제 동작을 구현하는 데 이상적입니다. NI VeriStand 애드온 커뮤니티에서 FPGA XML 빌더 노드를 다운로드할 수 있습니다.

직접 구성한 FPGA I/O를 NI VeriStand에서 실행하는 방법

일반 어플리케이션을 개발할 때 개발자는 맞춤 FPGA 로직 프로그래밍, FPGA 로직과 리얼타임 프로세서간의 통신 메커니즘, 리얼타임 어플리케이션에서 데이터 전/후 처리를 담당합니다. NI VeriStand는 이 중 두 가지 (통신 메커니즘과 데이터 처리) 기능을 실행하는 메커니즘을 제공함으로써 리얼타임 테스트 어플리케이션에서 FPGA를 사용하는 데 필요한 작업양을 줄여줍니다. FPGA 특성을 NI VeriStand에 사용하면 FPGA 를 개발한 후 XML 파일을 사용하여 FPGA 특성과 NI VeriStand 리얼타임 테스트 어플리케이션간의 인터페이스를 기술하기만 하면 되므로 개발에 필요한 개발 노력이 절감됩니다.

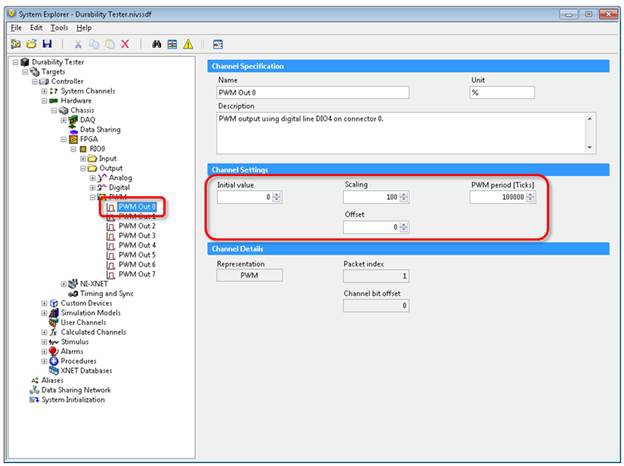

NI VeriStand에서 FPGA를 사용할 때, 인터페이스하기 위해 필요한 코드를 포함한 NI LabVIEW 프로젝트를 사용하여 시작할 수 있습니다. LabVIEW를 사용하여 FPGA 기능을 직접 정의하고 FPGA 특성을 컴파일한 후 FPGA 특성을 위해 XML 파일을 편집합니다. 이 단계가 완성되면, XML 파일을 선택하기만 하면 생성된 FPGA 특성을 NI VeriStand 시스템 정의에 추가할 수 있습니다. XML 파일은 FPGA 특성에 인터페이스하는 방법과 NI VeriStand System Explorer 내에서 입출력과 파라미터를 자동으로 제공하는 방법을 NI VeriStand에 전달하므로, 사용자는 다른 하드웨어 인터페이스를 사용할 때와 마찬가지로 기타 리얼타임 태스크에 값과 연결을 설정할 수 있습니다. 예를 들어, 사용자가 FPGA I/O를 통하여 PWM 출력에 대한 정의하면 NI VeriStand System Explorer는 사용자가 주기 및 초기값 등의 채널 파라미터를 설정하고 듀티비 입력을 리얼타임 테스트 어플리케이션의 다른 채널에 맵핑하도록 합니다. (그림 1)

그림 1: System Explorer에서 NI VeriStand FPGA 구성하기

사용자가 NI VeriStand 리얼타임 어플리케이션을 배포하면 NI VeriStand는 컴파일된 FPGA 특성을 하드웨어 인터페이스로 자동 다운로드합니다.

NI VeriStand FPGA 아키텍처

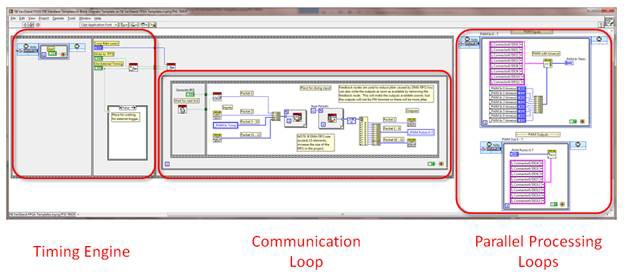

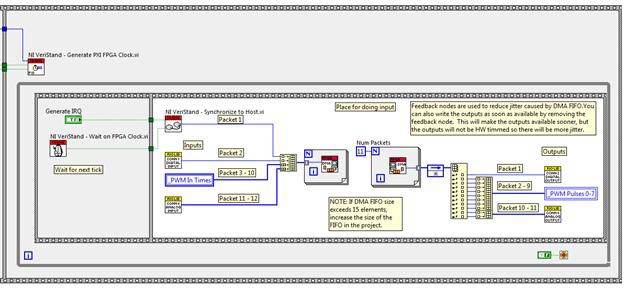

LabVIEW FPGA를 사용하여 NI VeriStand FPGA 를 생성하여 템플릿을 변경할 수 있습니다. 템플릿에는 NI VeriStand 어플리케이션에 인터페이스하기 위해 필요한 코드가 포함됩니다. NI VeriStand의 FPGA는 타이밍 엔진, 통신 루프, 병렬 처리 루프로 구성됩니다.

Figure 2: NI VeriStand FPGA Personality Template

타이밍 엔진

타이밍 엔진은 NI VeriStand System Explorer에서 설정이 가능하며 FPGA를 NI VeriStand 리얼타임 어플리케이션 및 시스템의 기타 하드웨어 I/O 디바이스와 동기화합니다. NI VeriStand 리얼타임 어플리케이션이 배포되면 어플리케이션은 FPGA 특성을 로딩하고 타이밍 엔진은 NI VeriStand로부터 시작 조건을 기다립니다.

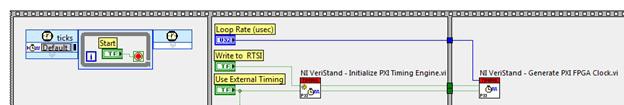

그림 3: 타이밍 엔진 초기화

리얼타임 어플리케이션이 시작 트리거를 시작하기 전에, NI VeriStand는 Loop Rate (usec), Write to RTSI, Use External Timing에 대한 파라미터를 설정합니다. 이 세 가지 파라미터는 타이밍 엔진의 동기화 모드 (마스터, 슬레이브 또는 동기화 없음)를 구성하고 특성과 NI VeriStand 리얼타임 어플리케이션간의 통신 속도를 설정합니다.

NI VeriStand – Generate PXI FPGA Clock subVI는 통신 루프의 시간을 담당하는 클럭을 생성하며 동기화를 처리합니다. 마스터 노드에서 FPGA는 FPGA에서 실행되는 루프 타이머로 통신 루프의 시간을 담당하며 클럭을 RTSI (Real-Time System Integration) 버스로 반출하여 기타 하드웨어 디바이스를 동기화합니다. 슬레이브 모드에서 FPGA는 RTSI 버스를 모니터링하며 RTSI0에서 캡쳐된 클럭으로 통신 루프의 시간을 잽니다. No Synchronization 모드에서 FPGA는 루프 타이머로 통신 루프의 시간을 처리하며 RTSI 버스로 아무 것도 반출하지 않습니다.

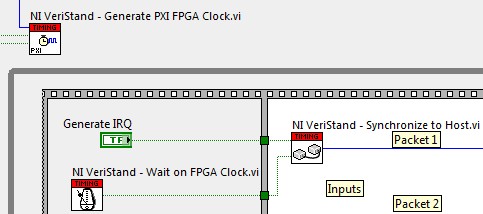

하드웨어 동기화를 수행하는 것 이외에도 타이밍 엔진은 또한 NI VeriStand 리얼타임 어플리케이션에 동기화를 허용합니다. 그림 4는 통신 루프의 일부입니다.

그림 4: FPGA로 NI VeriStand 동기화

NI VeriStand – Wait on FPGA Clock subVI는 통신 루프를 위한 루프 타이머 역할을 하며 NI VeriStand – Generate PXI FPGA Clock subVI로부터 클럭을 기다립니다. 마스터 모드에서 NI VeriStand는 시작 컨트롤을 지정하기 전에 Generate IRQ를 지정합니다. Generate IRQ가 지정되면 NI VeriStand – Synchronize to Host subVI는 통신 루프의 각 반복에 대해 인터럽트를 지정합니다. FPGA가 마스터로 구성되면 NI VeriStand 리얼타임 어플리케이션 실행은 이 IRQ 신호를 통해 FPGA가 시간 처리합니다.

통신 루프

통신 루프는 NI VeriStand 리얼타임 어플리케이션에서 데이터를 송수신합니다. NI VeriStand는 하드웨어 타이밍 단일 포인트 방식으로 채널을 업데이트하므로 FPGA는 반드시 NI VeriStand Engine의 Primary Control Loop에서 지정된 속도로 통신 루프를 실행해야 합니다. NI VeriStand Engine에 대한 더욱 자세한 정보는 NI VeriStand 도움말을 참조하십시오.

통신 루프는 NI VeriStand – Wait on FPGA Clock subVI (NI VeriStand – Generate PXI FPGA Clock subVI에 의해 생성된 클럭을 기다리는 루프 타이머)의 타이밍에 의해 진행됩니다.

그림 5: 데이터 통신 루프

그림 5와 같이 64-비트 패킷 형태의 데이터는 DMA FIFO (first-in-first-out) 메모리 버퍼를 통해 NI VeriStand 리얼타임 어플리케이션으로 전송되며, 64-비트 패킷 형태의 데이터는 DMA FIFO를 통해 NI VeriStand 리얼타임 어플리케이션으로부터 수신됩니다.

NI VeriStand로 보내진 첫 번째 패킷에는 FPGA 루프 실행 지연 여부를 설명하는 NI VeriStand – Synchronize to Host subVI로부터의 정보가 포함됩니다. 호스트에 보내지는 다른 패킷에는 FPGA에 의해 수행된 측정 또는 계산 데이터가 포함됩니다. 패킷은 DMA_READ FIFO에 쓰기를 담당하는 For 루프 내의 NI VeriStand – Send Packet to Host subVI에 작성하여 전달됩니다. DMA_READ FIFO는 프로젝트 탐색기에서 정의되며, 깊이 (depth)는 반드시 최소한 패킷이 각 반복에 보낸 요소의 개수를 갖도록 정의되어야 합니다.

데이터는 프로젝트 탐색기에서 정의되는 DMA_WRITE FIFO를 통해 FPGA로 보내집니다. 크기는 반드시 각 반복에 보내지는 최소한의 개수를 갖도록 지정되어야 합니다. DMA_WRITE FIFO는 For 루프 내에 배치된 NI VeriStand – Receive Packet from Host subVI에 의해 FPGA에서 읽혀집니다. For 루프는 반드시 While 루프의 각 반복에서 읽혀져야 하는 패킷 반복의 동일 개수를 실행하도록 구성되어야 합니다. 그 후 패킷은 분리되며 FPGA 특성의 적절한 부분으로 보내집니다. 그림 5에서 노란색 막대가 있는 subVI는 I/O 리소스를 나타냅니다. 본 루프에서 수집되고 생성된 모든 I/O는 NI VeriStand와 시스템의 다른 하드웨어 디바이스와 동기화됩니다.

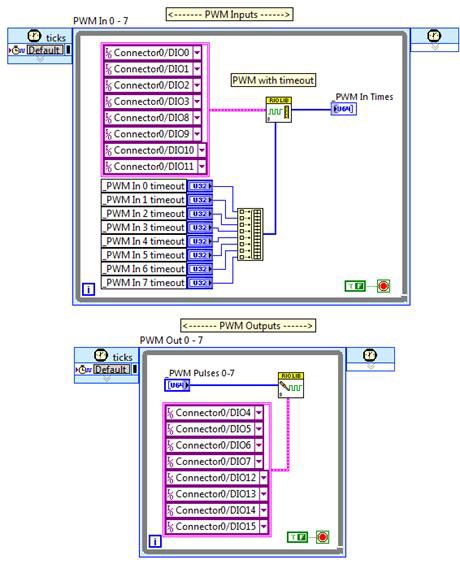

병렬 처리 루프

병렬 처리 루프는 NI VeriStand 프레임워크 내의 직접 정의된 FPGA 특성의 최종 부분입니다. 병렬 처리 루프가 병렬이라고 불리는 이유는 NI VeriStand와 시스템의 나머지 하드웨어에 대한 통신 루프의 시간을 처리하는 동일한 클럭으로 시간이 처리되지 않기 때문입니다. 병렬 처리 루프는 맞춤 타이밍이 있는 I/O에서 데이터를 수집하거나 생성할 수도 있고, PWM I/O와 같은 맞춤 측정과 생성을 진행할 수도 있습니다. 또한 NI VeriStand에서 FPGA로 보내지는 데이터를 코프로세싱 (coprocessing)할 때 사용될 수도 있습니다. 예제 템플릿은 그림 6과 같이 PWM 입출력을 포함합니다.

그림 6: 병렬 PWM 루프

그림 5, 6과 같이 병렬 처리 루프는 로컬 변수를 통해 통신 루프에서 데이터를 송수신합니다. 통신 루프는 실행되는 속도에서만 로컬 변수를 업데이트하며, 로컬 변수의 현재 값만 (버퍼링 없음)을 NI VeriStand 호스트로 보냅니다. 병렬 루프의 데이터는 통신 루프에 의해 제거되지만 병렬 루프의 타이밍은 통신 루프의 영향을 받지 않습니다.

다음 단계

FPGA 기반 I/O 인터페이스는 리얼타임 테스트 어플리케이션을 위한 여러가지 장점을 제공합니다. 다양한 요구조건을 만족하며 하드웨어 설정을 변경하지 않고 여러 어플리케이션에 사용되는 테스트 시스템을 구축할 수 있도록 편리하게 재구성되는 신호 처리, 시뮬레이션, 트리거링, 컨트롤을 통합 실행하는 I/O 디바이스를 직접 구축할 수 있습니다. NI VeriStand에서는 통신 메커니즘과 데이터 처리를 실행하는 프레임워크를 제공하여 리얼타임 테스트 어플리케이션에서 FPGA를 사용하는 데 필요한 개발 작업양을 줄여주므로, 사용자는 FPGA 기능 개발에 더욱 집중할 수 있습니다. 그 후 다른 하드웨어 I/O 인터페이스를 사용하는 동일한 방식으로 FPGA 특성을 NI VeriStand에 추가하고 구성 기반의 환경을 사용하여 나머지 리얼타임 테스트 어플리케이션을 완성할 수 있습니다.