FlexRIO 控制器:深入了解可部署的儀器

綜覽

FlexRIO 控制器為商用現成 (COTS) 解決方案,屬精巧的獨立式規格,專為需要高效能 I/O 與即時訊號處理功能的應用所設計。模組化 I/O、以 LabVIEW 設計程式的 FPGA,與內建處理器組合,讓工程師可針對特定應用重新設定硬體,這也是 FlexRIO 控制器與多數 COTS 儀控的差異之處。此控制器也可與 PXI 上的 FlexRIO 共用相同的轉接器模組、FPGA 與軟體體驗,非常適合為開發的解決方案佈署在 PXI 平台上。雖然此控制器與 PXI 中的 FlexRIO 有許多相同之處,但它主要是針對嵌入式應用設計,以執行更小巧、更輕盈、耗能較低的解決方案。

內容

圖 1:FlexRIO 控制器是一款獨立式擷取與訊號處理裝置,具備高效能 I/O 與大型 Kintex-7 FPGA。

內部架構

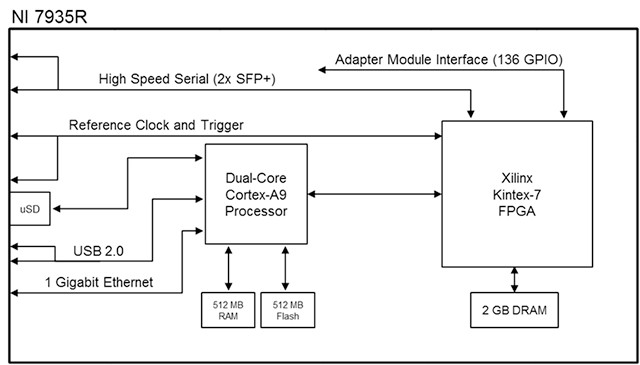

FlexRIO 控制器是根據大型 Kintex-7 FPGA 所建,並連接至模組化 I/O 介面、處理器,以及 2 GB DDR3 DRAM。FPGA 包含超過 400000 組邏輯分割、1540 個數位訊號處理 (DSP) 分割與 28 Mb BRAM,因此可在 FPGA 上處理大量的訊號處理作業。雙核心 ARM 處理器提供網路與 USB 連接功能,可與其他裝置介接,且內建儲存空間,可記錄參數與資料。

當大多數的演算法都可在 FPGA 上操作時,大型 FPGA 與低耗電處理器組合將特別重要,而雙核心 ARM 處理器則可用來設定開機設定與系統監控。此架構讓智慧更具優勢,可透過高效能 FPGA,將高速資料轉換為有效資訊。

圖 2:FlexRIO 控制器配備大型 Kintex-7 FPGA,非常適合即時執行訊號處理演算法的應用。

若需在中央位置彙整高頻寬資料,NI 7932R 與 NI 7935R 型號也具備 2 組高速序列埠,可透過 10 Gigabit 乙太網路 UDP、Xilinx Aurora 或客製化協定,直接從 FPGA 串流資料。

FlexRIO 轉接器模組介面

圖 3:NI 5772 為 2 通道的高速示波器轉接模組,常用於時域與頻域量測作業。

FPGA

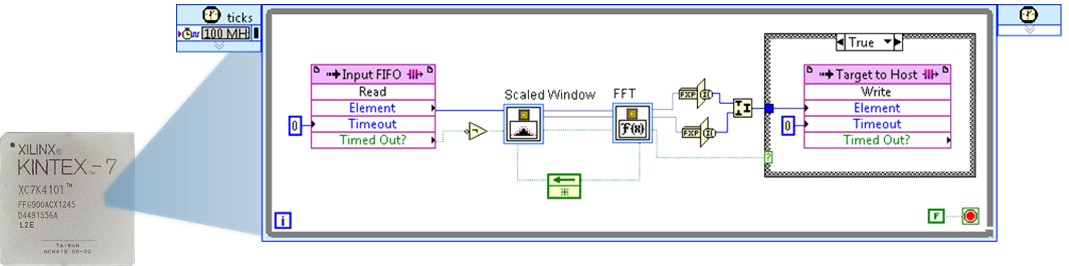

使用者可透過 LabVIEW FPGA Module,搭配 LabVIEW 系統設計軟體來進行 FPGA 程式設計,並同時進行 LabVIEW 架構的演算法擷取,與 VHDL/Verilog 的整合。現有的 LabVIEW 函式庫可搭配資料傳輸基礎架構、超寬頻快速傅利葉轉換 (FFT) 等進階訊號處理功能,與平行重新取樣演算法,以及託管 DMA 串流至主機,可加速開發流程。在本地或透過 NI Compile Cloud Service 編譯之前,可於 LabVIEW 中模擬設計。使用 LabVIEW FPGA 與 Xilinx Vivado 編譯 FPGA 位元檔案之後,再透過下列功能佈署位元檔案:開發機器上的 LabVIEW;控制器上所執行的以 LabVIEW 或 C/C++ 建立的即時應用程式;或是在開機時從裝置的閃存中。在許多 FlexRIO 設計中,邏輯電路時脈為數百 MHz,因此更難滿足時序限制。NI 建議新的 LabVIEW FPGA 開發人員先閱讀高效能 LabVIEW FPGA 開發人員指南,了解時序與資源最佳化的最佳實務。

圖 4:LabVIEW 提供針對設計、模擬、除錯,與佈署的整合式圖形化開發環境,簡化 FPGA 程式設計。

工程師可以選擇 2 種 FPGA 選項:Xilinx Kintex-7 K325T 與更大的 K410T。若是初期開發,則使用最大的 FPGA 可享有顯著的優勢。不僅可於開發期間新增功能,亦可在較大的 FPGA 上編譯相同的程式碼,進而縮短設計期間的編譯時間,並加速反覆式的速度。透過 NI 提供的 I/O 介面,針對單一硬體目標所撰寫的LabVIEW FPGA 程式碼,即可快速匯至其他 NI 硬體,甚至是具有不同 FPGA 與 I/O 功能的硬體。

FPGA | 分割 | 查找表 (LUT) | 正反器 | DSP 分割 | 區塊 RAM (kb) | 內建 DRAM |

Kintex-7 K410T | 63550 | 254200 | 445200 | 1540 | 28620 | 2 GB |

Kintex-7 K325T | 50950 | 203800 | 407600 | 840 | 16020 | 2 GB |

圖 5:FlexRIO 控制器具有 2 種不同的 Xilinx FPGA,以便使用者針對應用選擇正確的零件。NI 建議先使用最大的 FPGA,以進行初步開發,然後再嘗試最佳化設計以進行佈署。

DRAM 可於多級訊號處理演算法與跨非確定性匯流排的資料緩衝中,大幅增值。至 可進行這些類型的執行,所有三款 FlexRIO 控制器均具備 1 組 2 GB 的 DDR3 DRAM,連接至 FPGA。DRAM 介面具有 512 位元的資料寬度,並以最高 166 MHz 的時脈率進行存取,因此 DRAM 與 FPGA 之間的最高理論頻寬為 10.6 GB/s。隨機存取讀取與寫入作業會降低 DRAM 傳輸率,不過,NI 已將序列讀取與寫入作業標為 9 GB/s 以上的速度。DRAM 可透過 LabVIEW FPGA 中的 LabVIEW 記憶體項目進行存取,也可使用記憶體儀器設計函式庫 (IDL) 作為 FIFO。

高速序列

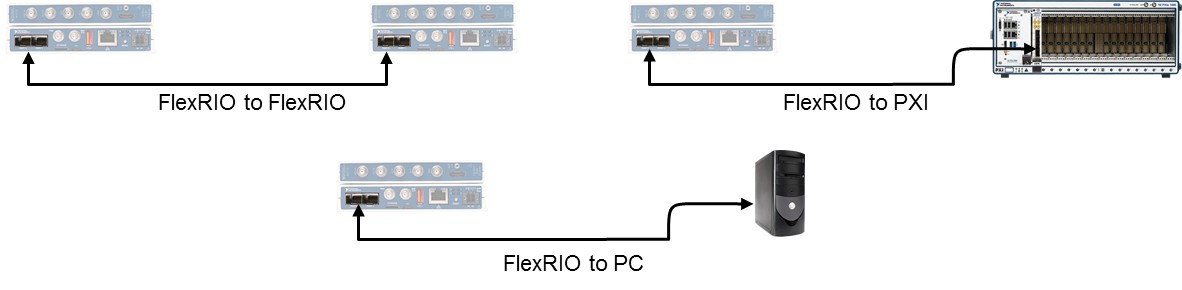

針對訊號擷取並處理後,需要高頻寬資料串流的應用,NI 7932R 與 NI 7935R 均配備 2 組高速序列收發器,各組收發器均可達到最高 10.3125 Gb/s 的資料串流速度。此技術依賴 Xilinx GTX 多 Gigabit 收發器 (MGT),可從 FPGA 路由至人機介面上的 2 個 SFP+ 接頭。NI 提供適用於 10 Gigabit 乙太網路 UDP 與 Xilinx Aurora 協定的 LabVIEW FPGA 範例專案。具有 VHDL 經驗的使用者也可實施其他協定,如 Serial RapidIO 或客製化協定。

可使用這些高速序列埠的資料串流設定,包含在多個控制器之間共用資料 使用 Xilinx Aurora 或 10 Gigabit 乙太網路將資料串流回 PXI,並用 10 Gigabit 乙太網路將資料串流至桌上型電腦、資料記錄器、網域儲存 (NAS) 或伺服器。

圖 6:高速序列埠可將高頻寬資料串流至多個裝置。通訊協定會在 LabVIEW FPGA 中定義,每個收發器執行率可高達 10.3125 Gb/s。

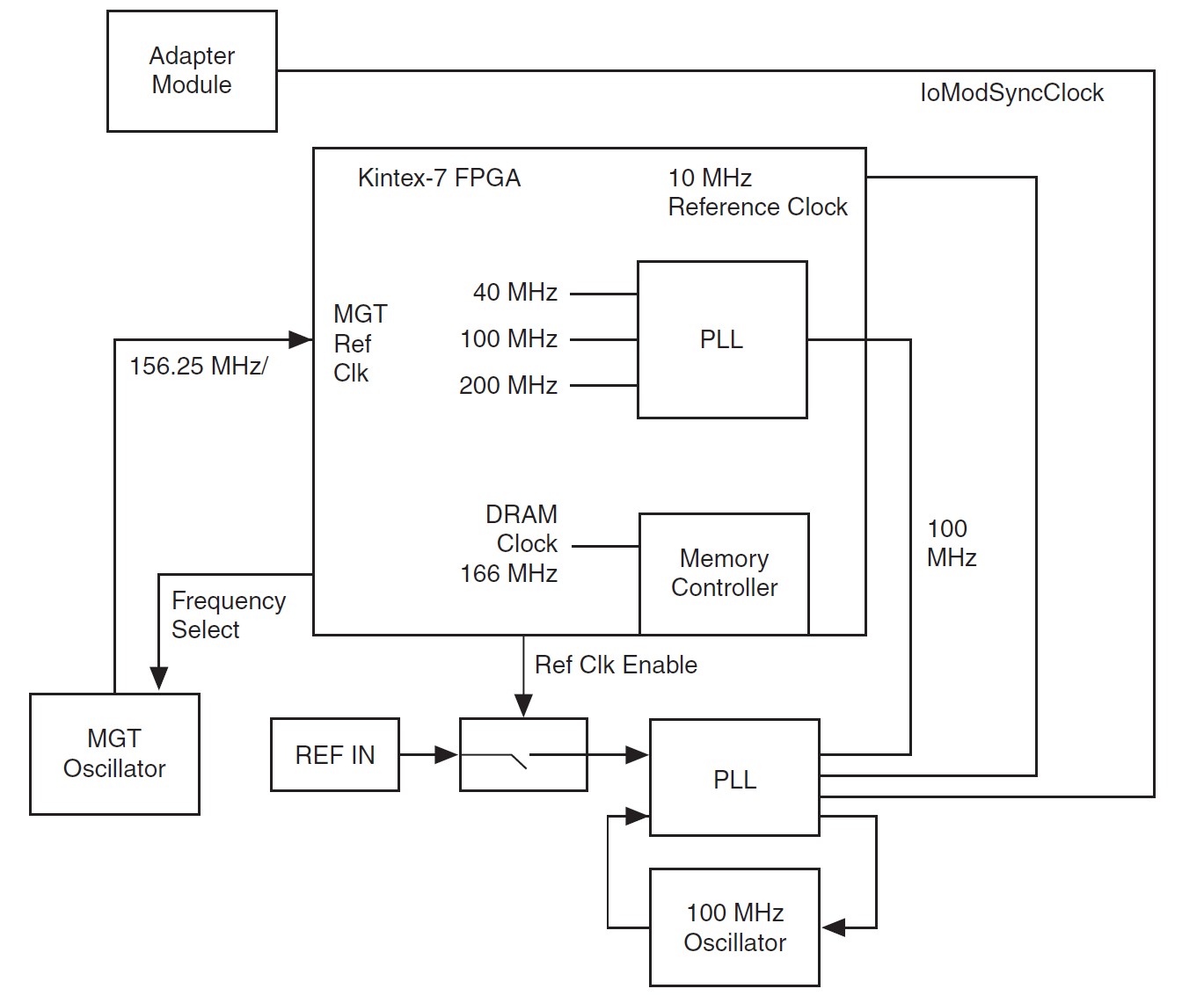

時脈

使用 FPGA 與高速 I/O 的工程師通常會花費大量時間,來實施合適的時脈與同步化架構。為簡化此程序,FlexRIO 控制器提供多種時脈選項,包含外部 10 MHz 參考時脈輸入、雙向觸發線路、內建 100 MHz 振盪器,並可鎖相 至外部參考為確保 I/O 模組與 FPGA 之間的資料傳輸同步化,I/O 模組取樣時脈會與 FlexRIO 控制器時脈電路共用。亦可透過 FPGA 產生額外的時脈。

圖 7:透過 FlexRIO 控制器上的時脈電路,使用者即可運用子取樣精確度為多個裝置進行同步。

針對分散式系統與時間戳記,可連接 GPS 接收器,以為參考時脈輸入提供 10 MHz 時脈,為觸發 SMA 提供 1 秒的脈波輸入。針對不太嚴格的同步化需求,NI Linux Real-Time 主機亦可支援軟體架構的 IEEE 1588。對於可進行電子同步化的系統,可使用 10 MHz 源,如 Ettus Octoclock,以提供共用的參考時脈。如果要同時使用多個設備,就可以考慮 PXI 平台的進階時脈與同步化功能。

處理器

雙核心 ARM Cortex-A9 處理器可提升彈性與連線功能,可在現場部署 FlexRIO 控制器。此處理器可用來提供網路資料、調整設定參數、記錄資料與訊息,甚至更新裝置上的軟體與 FPGA 韌體。此處理器搭載 NI Linux Real-Time OS,可提供更高的決定性與穩定性,以及 Linux 核心的標準優勢。Real-Time OS (RTOS) 可透過 LabVIEW Real-Time Module 搭配 LabVIEW 進行程式設計,並且可透過個人偏好的整合式開發環境 (IDE) 支援 C/C++ 開發。透過 LabVIEW 程式設計與建置應用,即可存取預先建立的函式庫,以用於網路通訊與檔案 I/O,進而簡化開發程序。

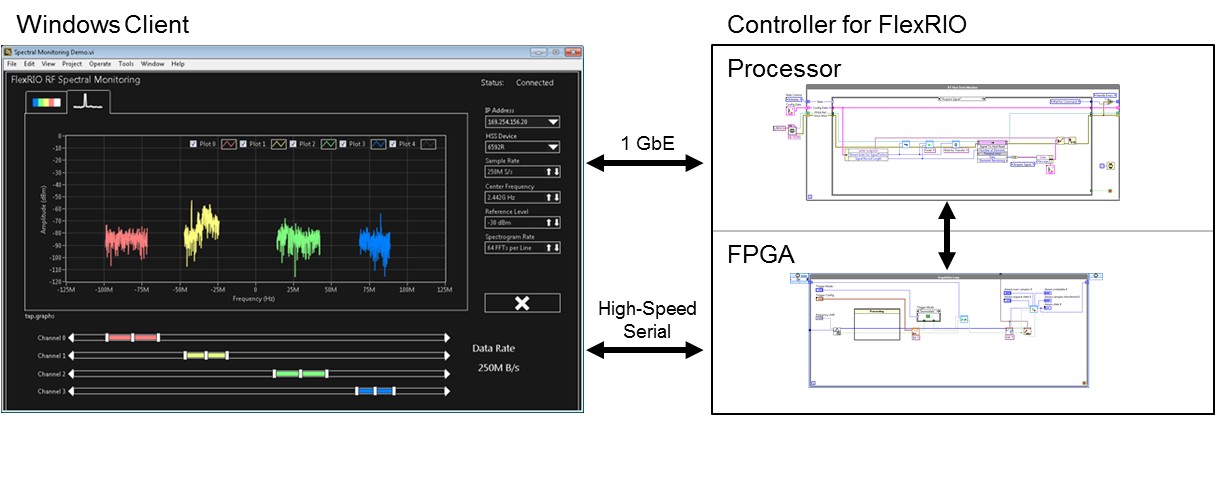

對 FlexRIO 熟悉的使用者來說,從 PXI 的 FlexRIO 遷移至 FlexRIO 控制器時,主要的差異就是在 FPGA 與傳統的 Windows 用戶端之間新增網路通訊層。無需透過 Windows 直接以 FPGA 為目標,而是針對 NI Linux Real-Time 所開發的程式碼以 FPGA 為目標,由使用者自行設計任何網路通訊的程式,以監控或設定係統。NI 7932R 與 NI 7935R 均可利用 2 組高速序列埠,透過 10 Gigabit 乙太網路 UDP 或 Xilinx Aurora,直接從 FPGA 傳輸資料。

圖 8:佈署的系統通常包含 3 組應用層:FPGA 韌體、Linux Real-Time 主機上執行的 LabVIEW 或 C/C++ 程式碼,以及遠端設定、監控或資料記錄的用戶端應用。

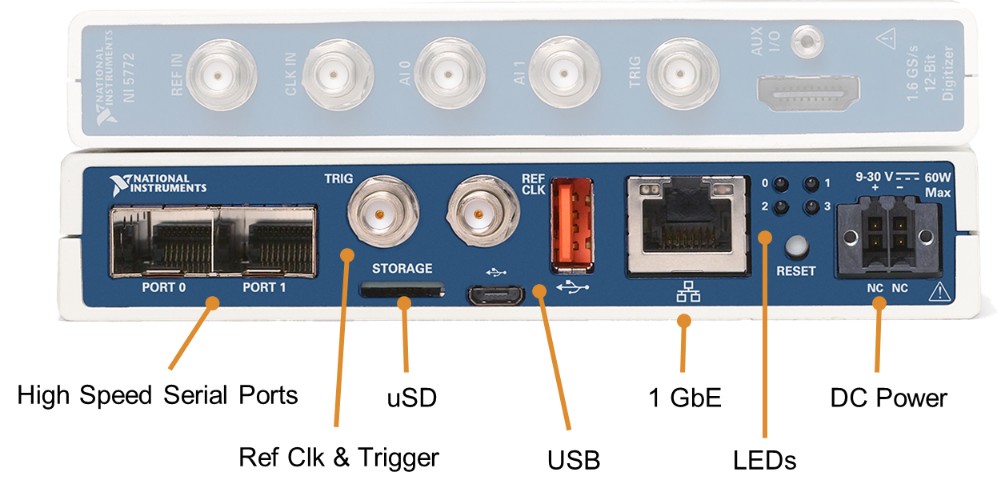

處理器亦可使用 512 MB 的隨身碟與 512 MB RAM、1 Gigabit 乙太網路介面、USB 2.0 裝置與主機介面、USD 卡插槽。1 Gigabit 乙太網路已佈署應用的主要介面,可支援更多頻寬;不過,USB 裝置埠可用於設定、設定與診斷。

連接功能

所有連接功能均呈現於單一硬體表面,可更輕鬆整合至更大的系統。雖然 I/O 為模組化設計,但類比轉接器模組也可透過附屬 I/O 接頭,為 FPGA 提供數位 I/O。控制器可接受 9 ~ 30 伏特的 DC 電源,也就是說可攜式系統的電池供電。

圖 9:除了 FlexRIO 轉接器模組所提供的連結功能,FlexRIO 控制器還具備工業級標準介面,適用於資料串流、適用於時脈與同步化的 SMA 接頭、可溝通周邊設備的 USB 埠,以及具有視覺狀態指示燈的 LED。

除 2 組 USB 通訊埠之外,所有接頭均具有連接線固定措施。USB 主機埠 (橘色) 是專為高保留時間所設計,而 USB 裝置埠則可主要用於診斷作業。

實體封裝

此裝置的鋁合金外殼,不需設計客製化的機械裝置,且可於多種情形中提供一致的類比與熱能效能,進而簡化整合作業。透過安裝套件,也可將裝置固定於面板。

圖 10:FlexRIO 控制器是專為體積、重量與功率受限的嵌入式應用所設計。

此封裝還具備多項功能,可確保產品的長期穩定性與適用性。首先,開發人員可以存取軟體,以監控 FPGA 與處理器的溫度。如果 FPGA 或處理器溫度超過安全限制,則裝置將自動關閉,以防止內部元件損壞。主動式冷卻是由使用者可自行維護的風扇提供,並可透過軟體進行監控,並根據裝置溫度自動調整。在 40 °C 時,風扇的平均無故障時間 (MTBF) 超過 7 年。

如果要針對沖擊、振動、溫度或濕度的情形來說,FlexRIO 控制器的等級與 PXI 類似,可承受 30 g 峰值半正弦波衝擊、0.3 grms 振動、5 Hz 至 500 Hz、0 °C 至 55 °C 環境溫度,5% 到 95% 的濕度。

摘要

十多年以來,NI 透過 LabVIEW 可重設 I/O (RIO) 架構 與 LabVIEW FPGA,一直以來都能快速製作即時執行的演算法原型,這是過去十多年的優勢。對於雷達、頻譜監控、通訊、工業機器、超音波與醫療影像等領域的新技術原型工程師與科學家來說,此平台可加速製作原型的速度,並在產品化或佈署期間重複使用最多的程式碼。

後續步驟

- 深入了解 FlexRIO

- 購買 FlexRIO 轉接器模組

- 查看 FlexRIO 控制器機型

Linux® 註冊商標的使用方式係根據 LMI 的轉授權許可;Linus Torvalds 持有此商標在全球的擁有權、LMI 則取得 Linus Torvalds 的獨家授權。