광대역 IF 디지타이저를 사용하여 RF 신호 스트리밍 및 기록 문제 해결

개요

내용

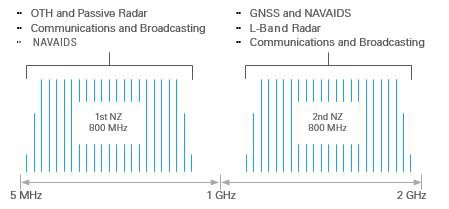

그림 1. 5 MHz–2 GHz 대역의 신호 예

과제

검증 및 검증 테스트, 스펙트럼 감시, 다중 성좌 GNSS, 소프트웨어 정의 수신기의 많은 어플리케이션에는 RF 신호의 수집, 리얼타임 처리, 기록이 필요합니다. 최신 아날로그-디지털 변환기 (ADC) 기술을 사용하면 2 GHz 이상에서 작동하는 직접 샘플링 수신기를 이용할 수 있습니다. 이를 통해 채널 간에 긴밀하게 동기화해야 하는 다중 채널 시스템의 경우 수신기의 아키텍처가 단순해집니다. 스펙트럼 감시, 가시선 밖 수동 레이더, 안테나 측정을 위한 방향 찾기 시스템의 경우가 그렇습니다.

또한 더 빠른 스펙트럼 스캔과 새로운 타입의 레이더에 대한 요구가 늘어나고 있어 넓은 순간 대역폭과 리얼타임 신호 처리 기능을 갖춘 수신기가 필요합니다.

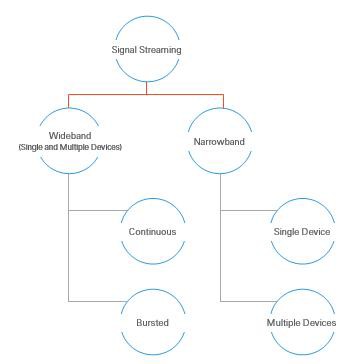

일반적으로 현재 RF 스트리밍 시스템은 고대역폭의 무손실 스트리밍과 협대역 스트리밍이라는 두 가지 형태를 취합니다. 첫 번째 타입은 사용 가능한 모든 대역폭을 기록합니다. 이는 최신 어플리케이션에서 2 GS/s 이상으로 샘플링하는 시스템의 경우 초당 기가바이트를 의미합니다. 활성 레이더 시스템은 일반적으로 광대역 스트리밍을 활용합니다.

그러나 유용한 정보의 대부분은 특정한 좁은 대역에 집중되는 경우가 많습니다. 이때 두 번째 스트리밍 타입이 사용됩니다. 협대역 스트리밍을 사용하면 데이터 축소와 인라인 신호 처리가 가능합니다. 이러한 시스템은 여러 중앙 주파수를 가지는 상대적으로 좁은 대역의 HDD 신호를 스트리밍해야 합니다.

수동 레이더 애플리케이션에서 수집, 스트리밍, 분석 (또는 기록)된 협대역 신호의 한 가지 예는 국가에 따라 대역폭이 6 MHz에서 8 MHz이며 VHF/UHF 주파수 범위에 있는 DVB-T (디지털 비디오 방송-지상파) 또는 ATSC (Advanced Television Systems Committee) 송신기에서 발생할 수 있습니다.

협대역 스트리밍의 다른 예로는 GPS L5/L2와 GLONASS G1 및 G2 신호를 모두 사용해야 하는 GNSS 다중 성좌 수신기 테스트입니다. 사용자는 폭이 수 MHz에 불과하지만 간격은 수백 MHz일 수 있는 신호를 집중적으로 살펴볼 수 있습니다.

그림 2. 이 문서에서 다루는 스트리밍 어플리케이션의 분류

이렇게 광대역 신호를 수집한 후 이러한 스트리밍 시스템에 후속 다운컨버전 (주파수 이동), 데시메이션, 균등화, 교정이 필요합니다. 그 결과로 얻은 협대역 신호는 복조되고 디코딩되며 추가로 필터링되고 증폭되어 HDD 또는 이러한 기능 조합에 저장됩니다.

상위 레벨에서 일반적인 스트리밍과 채널화 어플리케이션은 그림 2와 같이 나눌 수 있습니다.

광대역 스트리밍

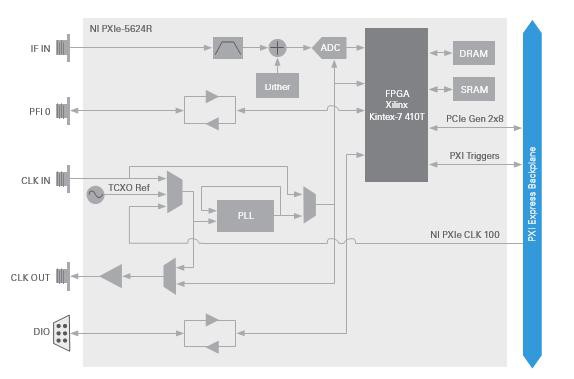

광대역 스트리밍과 관련된 과제를 더 잘 이해하려면 먼저 IF 수신기의 기술 스펙을 이해해야 합니다. 이 문서에서는 PXIe-5624R 모듈을 중점적으로 다룹니다. IF 수신기는 일반적으로 믹서, IF 수신기, LO용 신호 소스로 구성된 벡터 신호 분석기의 일부입니다. 예제 벡터 신호 분석기의 구조는 PXIe-5668R - 고성능 26.5 GHz 광대역 신호 분석기 소개 백서에 잘 설명되어 있습니다.

IF는 5 MHz~2 GHz 주파수 범위와 일반적으로 800 MHz의 대역폭을 특징으로 합니다 (자세한 내용은 기술 스펙 참조). ADC의 양자화 효과를 줄이고 스펙트럼 성능을 향상시키는 데 도움이 되는 대역 제한 노이즈 (디더) 신호를 추가한 후 ADC는 12비트 분해능에서 최대 2 GSa/s로 신호를 샘플링합니다. 온보드 FPGA는 이러한 샘플을 처리하고 PCI Express Gen 2x8을 통해 다른 디바이스 (PXI Express 컨트롤러, RAID)로 데이터를 전송합니다. 이를 통해 이론상 최대 4 GB/s의 데이터 스트리밍이 가능합니다. 광대역 스트리밍의 경우 FPGA는 들어오는 모든 데이터에 대해 한 번만 디지털 다운컨버전 (DDC)을 수행합니다. 그러나 이 문서의 뒷부분에서 설명하는 협대역의 경우 독립적으로 여러 번 다운컨버전이 이루어집니다.

그림 3. PXIe-5624R IF 디지타이저의 블록다이어그램

비트 패킹

광대역 스트리밍을 생각할 때 PCI Express 버스의 이론상 사용 가능한 대역폭뿐만 아니라 실제 한계 (즉, 같은 버스를 통해 이동하는 컨트롤 메시지)도 고려해야 합니다. PCI Express 버스를 통해 데이터를 전송하는 가장 간단한 방법은 ADC의 데이터가 12비트인 경우에도 16비트 샘플을 하나씩 전송하는 것입니다. 그러나 이 방식은 PCIe-5624R 모듈에서 사용할 수 있는 PCI Express 링크당 4 GB/s라는 이론상 한계 (2 GS/s의 2바이트/샘플은 4GB/s와 같음)로 이어져 사실상 연속 스트리밍이 불가능해집니다. 그러나 현명한 해결책이 있습니다. 바로 비트 패킹입니다. 비트 패킹을 사용하면 4개의 12비트 샘플이 3개의 16비트 워드로 패킹됩니다. 결과적으로 이 방법을 사용하면 데이터 속도가 4 GB/s에서 3 GB/s로 줄어 연속 데이터 스트리밍이 가능해집니다.

모듈 간 동기화

같은 타입의 여러 모듈에서 연속으로 스트리밍해야 하는 경우가 종종 있습니다. 이러한 다채널 동기화 RF 시스템은 방향 찾기와 같은 특정 어플리케이션을 지원합니다. 시스템은 서로 다른 채널 사이에서 들어오는 신호의 위상 차이를 분석하여 신호 소스의 방향을 결정할 수 있습니다.

이 경우 디지타이저는 같은 참조 클럭에 고정됩니다. 기본으로 참조 클럭은 100 MHz PXI Express 백플레인 클럭입니다. 따라서 동기화하면 여러 디바이스에서 동시에 수집을 시작할 수 있습니다. 더 정확히 말하면 각각에 대해 10 ps 범위 내에서 수집을 시작할 수 있습니다. 그러나 온도가 같을 경우 디지타이저 간 스큐를 실행마다 똑같이 유지하는 것이 중요합니다. 따라서 스큐는 교정을 통해 개선할 수 있습니다. 동기화에 타이밍 모듈이나 외부 케이블 연결이 필요하지 않습니다. 동기화는 PXI Express 백플레인에서 두 개의 트리거 라인을 사용합니다.

버스트 모드

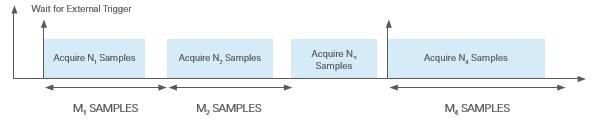

버스트 모드에서 데이터는 트리거 신호가 발생한 후에만 호스트로 스트리밍됩니다. 트리거 신호는 PFI0 커넥터를 사용하여 IF 디지타이저 보드에 직접 연결되거나 소프트웨어로 트리거될 수 있습니다. 사용자는 버스트 모드에서 몇 가지 파라미터를 설정할 수 있는 방식으로 FPGA의 로직을 정의할 수 있습니다.

- 기록 길이 (Nx)

- 기록 주기 (Mx)

- 트리거당 기록 개수

- 트리거 이전 샘플 개수

그림 4. 버스트 수집 시나리오의 예

이러한 버스트 시나리오는 다양한 기록 길이와 지연을 허용하는 방식으로 구현될 수 있습니다. 시나리오 설명은 호스트 머신에서 정의되고 나중에 FPGA로 스트리밍될 수 있습니다. 그러나 트리거 신호는 PFI0 신호가 125 MHz에서 샘플링되기 때문에 약 8 ns의 불확실성으로 샘플을 생성할 수 있습니다.

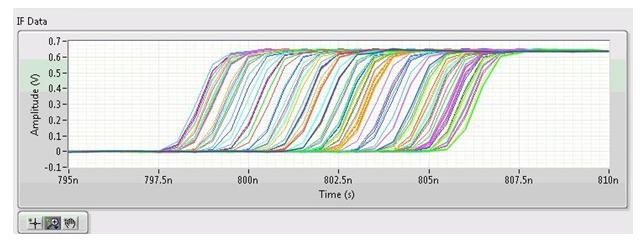

그림 5. 125 MHz에서 샘플링되는 PFI0으로 인한 트리거 불확실성

협대역 스트리밍

협대역 스트리밍은 GNSS 검증, 스펙트럼 모니터링, 수동 레이더, 방향 찾기 어플리케이션에 필요한 경우가 많습니다. 이러한 경우 사용자는 정의된 더 큰 스펙트럼 구성요소 내에 있으며 공간적으로 분산된 여러 안테나에서 오는 상대적으로 좁은 대역의 여러 신호에 관심을 보이는 경우가 많습니다.

필수적으로 신호를 동시에 수집해야 하기 때문에 기존의 스윕 벡터 신호 분석기를 사용할 수 없습니다. 이러한 과제를 해결하는 솔루션을 채널라이저라고 합니다. 이 어플리케이션은 협대역 신호가 모두 포함된 광대역 신호를 수집한 후 FPGA에서 DDC를 사용하여 분리하기 때문에 데이터 속도가 크게 감소됩니다.

디지털 다운컨버전

병렬 구조로 FPGA에서 많은 DDC 로직 블록을 구현할 수 있어 여러 협대역 신호를 동시에 분석할 수 있습니다. DDC의 첫 번째 단계에서는 디지타이저 범위 내 모든 주파수에서 기저대역으로 신호를 이동하는 디지털 쿼드러처 믹서가 사용됩니다. 다음 단계에서는 데시메이트입니다 (샘플 속도 감소). 데시메이션의 각 단계 이전에 프로그램 가능한 디지털 FIR 저역 통과 필터가 샘플 속도가 감소할 때 나타나는 앨리어스를 방지합니다. 사용자는 부분제거된 데이터를 동위상과 구적법으로 가져올 수 있습니다.

또한 사용자는 다음과 같이 시스템에서 아날로그 결함의 디지털 수정을 위해 디지털 신호를 처리할 수 있습니다.

- 디지털 게인 - I 및 Q 신호 진폭을 디지털 방식으로 컨트롤

- 디지털 오프셋 - I 및 Q 신호 오프셋을 디지털 방식으로 컨트롤

- 균등화 - I/Q 데이터를 필터링하여 디바이스의 아날로그 응답 균등화

- I/Q 손상 - I/Q 데이터를 수정하여 게인 불균형, 구적 스큐 또는 DC 오프셋과 같은 I/Q 손상을 수정하거나 적용

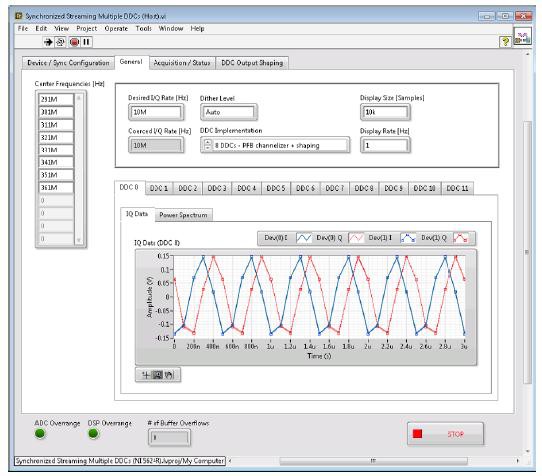

PXIe-5624R 디바이스에는 Xilinx Kintex-7 XC7K410T가 갖춰져 있어 37.5 MHz I/Q 속도의 경우 최대 12개의 DDC 또는 93.75 MHz I/Q 속도의 경우 최대 8개의 DDC에 맞출 수 있습니다 (자세한 내용은 NI에 문의). 서브 대역을 RAID로 스트리밍하거나 호스트 컴퓨터에서 온라인으로 분석할 수 있습니다.

IF 수신기를 사용하는 다중 안테나 DDC

위에서 언급한 것처럼 여러 PXIe-5624R 디바이스는 방향 찾기 어플리케이션과 같이 여러 안테나에서 수집하기 위해 동기화할 수 있습니다. 이러한 경우 사용자는 선택한 I/Q 속도로 최대 12개의 중앙 주파수를 정의할 수 있으며, 여러 IF 모듈은 여러 안테나의 신호를 다운컨버전합니다. PXI Express 솔루션은 여러 PXIe-5624R ADC의 동기화를 단순화합니다.

- 이러한 경우 다음 파라미터를 설정할 수 있습니다.

- 채널의 중앙 주파수

- 채널의 I/Q 속도

- ADC 클럭 소스

- 클럭 출력

- 버스트 크기 (버스트 수집의 경우)

- 샘플의 버스트 대기 기간

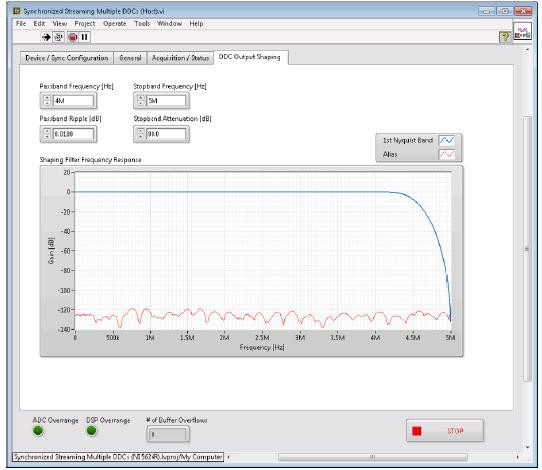

- 형성 필터의 파라미터

그림 6. 다중 모듈, 다중 채널 채널라이저 어플리케이션의 설정 윈도우 예제

그림 7. 형성 필터의 파라미터

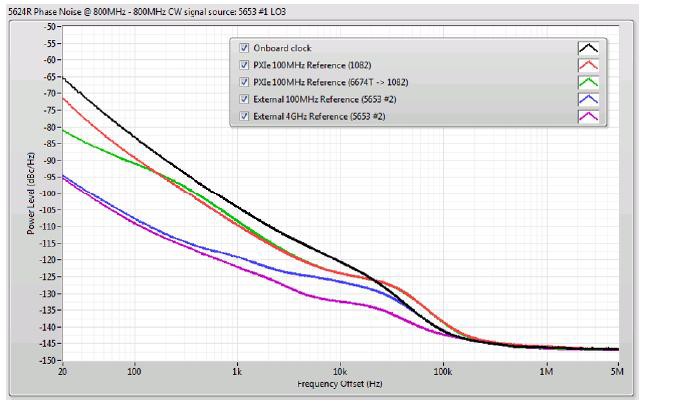

그림 8. 위상 노이즈 감소에 사용할 수 있는 다양한 옵션

위상 노이즈 고려사항 및 개선사항

PXIe-5624R IF 수신기의 개방형 아키텍처를 사용하면 위상 노이즈 최소화가 중요한 어플리케이션에서 외부 클럭 신호를 사용할 수 있습니다. 사용자는 시스템의 요건과 사용 가능한 예산에 맞춰 클러킹 신호를 ADC에 전달하는 가장 좋은 방법을 선택할 수 있습니다. 그림 8은 클럭 소싱의 다양한 설정을 보여줍니다. PXIe-6674T 모듈은 다중 모듈, 다중 섀시 시스템 (그림 8에서 녹색으로 표시된 위상 노이즈)을 위해 개발된 타이밍 및 동기화 모듈인 반면, PXIe-5653은 낮은 위상 노이즈 LO 생성기 (그림 8에서 파란색과 자주색으로 표시)입니다. PXIe-5653 모듈은 가장 낮은 위상 노이즈를 제공하는 반면, PXIe-6674T는 비용과 성능을 절충할 수 있습니다.

결론

NI의 PXI 기반 IF 수신기 (PXIe-5624R)에는 FPGA가 내장되어 있으며 레이더 테스트, GNSS 검증, 민첩한 스펙트럼 모니터링, 방향 찾기와 같이 가장 까다로운 스트리밍 어플리케이션을 지원하는 강력한 디바이스입니다. PXI 플랫폼의 장점과 결합된 개방형 아키텍처로, 위상 동기화가 가능하고 일관성을 갖춰 여러 채널로 쉽게 확장할 수 있습니다.

또한 NI 모듈형 방식을 사용하면 믹서 (PXI Express 폼 팩터에서 최대 26.5 GHz의 중앙 주파수 또는 72 GHz~76 GHz 라디오 헤드), 스위치, 전력 증폭기/감쇠기, 프리셀렉터 모듈과 같은 구성 요소를 추가할 수 있습니다.