高速シリアル通信の解説

概要

高速シリアルは、デバイスのサイズ縮小とデータ通信レートの向上を実現する技術として、ますます人気が高まっています。この技術資料では、高速シリアル通信リンクの基本概念について説明します。

内容

高速シリアルのニーズ

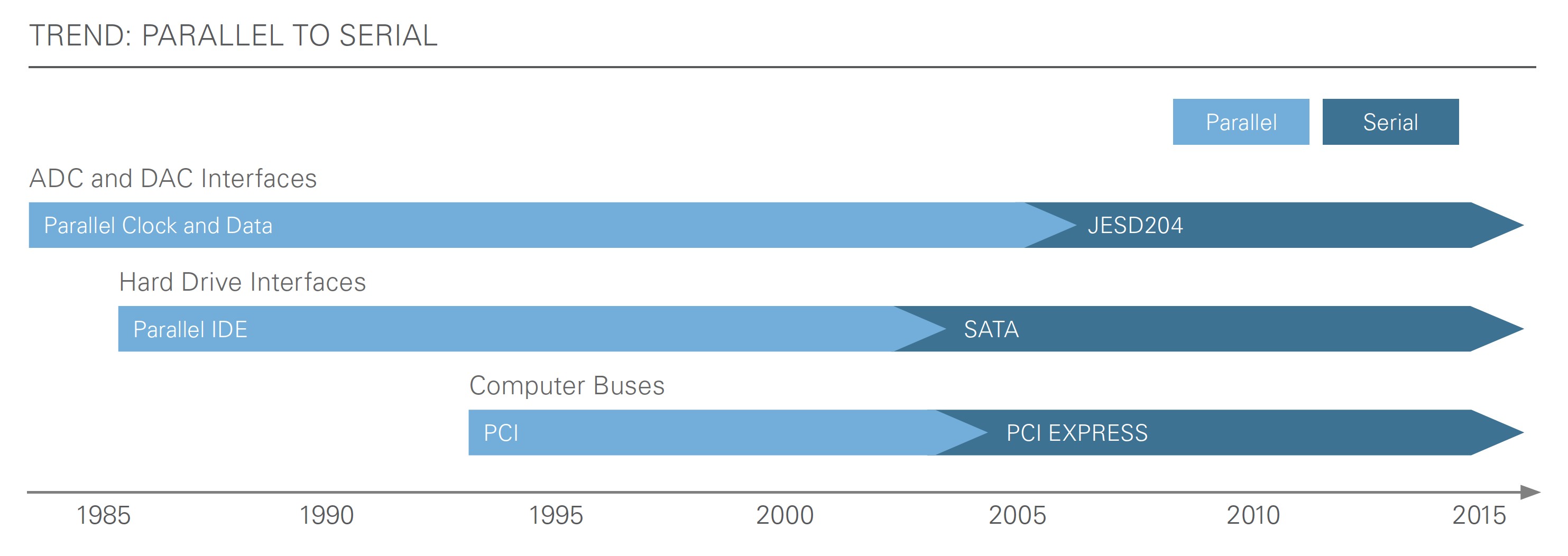

消費者は常に、性能の向上、サイズの小型化、消費電力の縮小を求めています。2000年代初頭に、ビッグデータの世界におけるこうした需要が、パラレルから高速シリアルデジタル通信バスへの急激なシフトを引き起こしました。その結果、デバイスのフットプリントの著しい小型化や、データスループットの大幅な向上、電力要件の低下が実現しました。これらの機能により、SATA、USB、PCI Expressなど、消費者が現在利用している多くのテクノロジが活用できます。

図1:2000年代初頭に、市場は一般的なパラレル通信規格からシリアル規格へと移行し始めました。

メリット

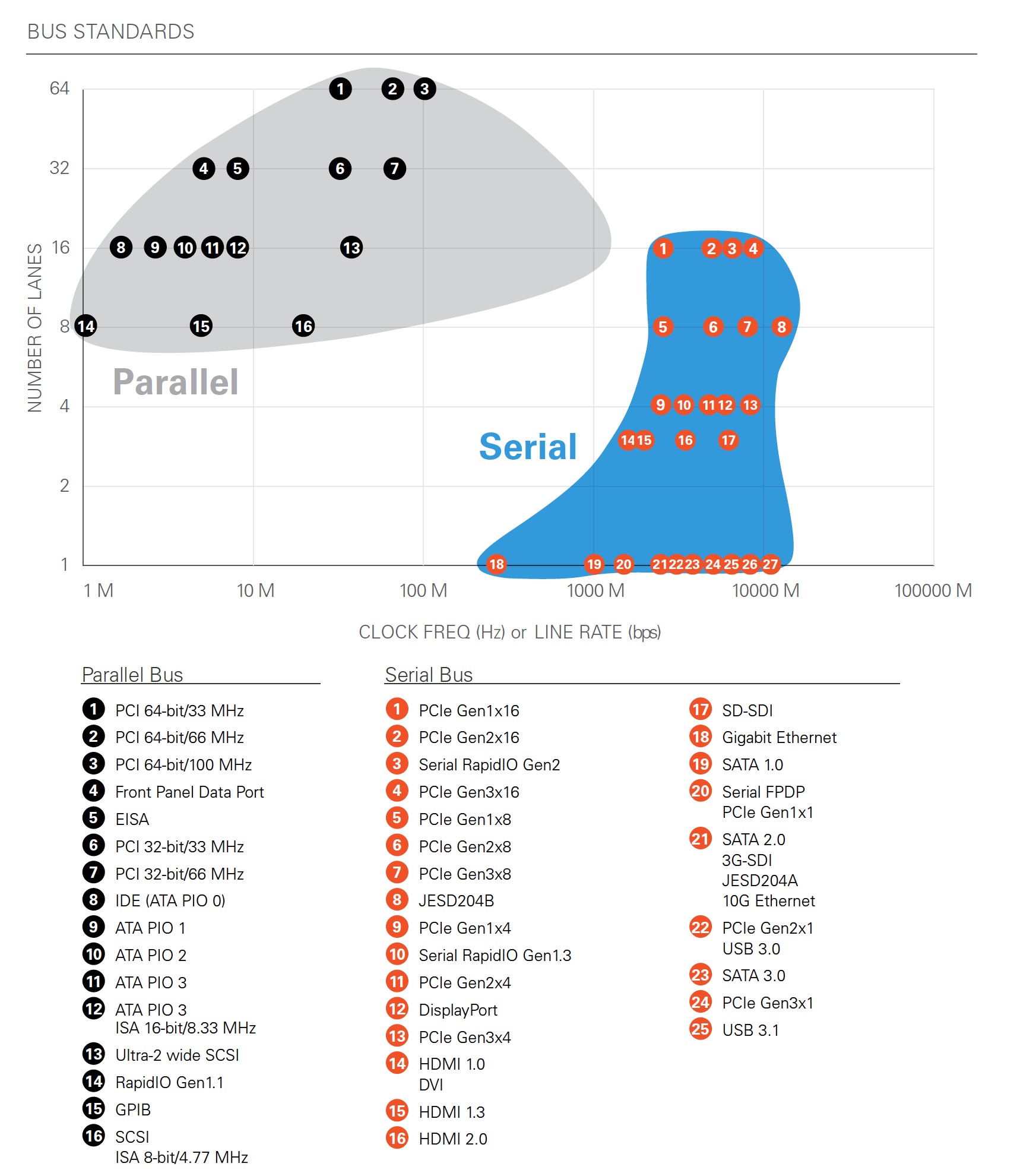

パラレルバスのクロックレートは、個々のクロックおよびデータラインでスキューが発生し、高速なレートでビットエラーを引き起こすため、約1~2 GHzが物理的限界とされています。高速シリアルバスは、1つの差動信号にデータとクロックの両方の情報を含め、データを符号化して転送するため、エンジニアはパラレルバスの速度制限を回避できます。現在では、10 Gbpsで転送を行うデータレーンを備えた高速シリアルリンクが一般的です。また、シリアルリンクの複数のレーンを位相同期しながら1つのバスにまとめることで、高いデータスループットが実現できる通信リンクを形成することができます。

データをシリアル化し、より高速で転送すれば、集積回路 (IC) のピン数を減らすことができるため、サイズを縮小しやすくなります。さらに、シリアルレーンはより速いクロック速度で動作できるため、パラレルバスの場合よりも高いデータスループットが実現します。

図2: このグラフは、広く普及しているバス規格と、それぞれのレーン数をラインレートに対比させたものです。これらのシリアル規格ではパラレル規格よりもはるかに高いラインレートが可能になるため、スループットの向上につながります。

デメリット

ピン数が減ることによって設計の複雑性は軽減できるものの、必要とされる高速転送を可能にするには、設計に新たな課題が生じます。RF周波数に達する設計では、適切な信号整合性を確保するために、RFアプリケーションと同様のアナログに関する考慮が必要です。こうした信号整合性の問題を軽減するため、高速シリアルリンクには、符号化、プリエンファシス、イコライゼーションといった技術が使われます。

高速シリアルリンクの層

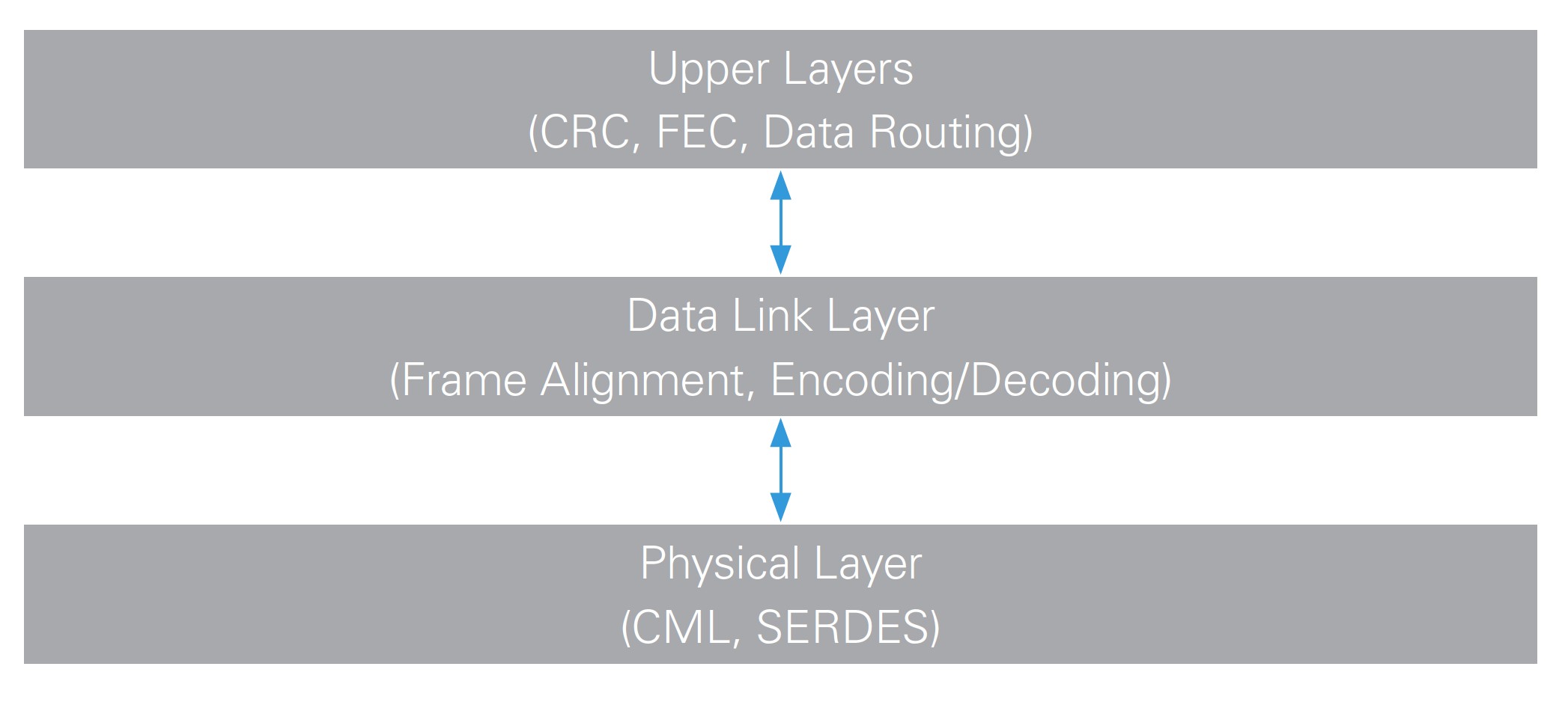

シリアル接続を機能させるには、各エンドが特定のパラメータ内で動作するということで一致している必要があります。これらのパラメータは、複数の機能層に抽象化できます。

図3: 物理層とデータリンク層の上に層が追加できます。これらの層はプロトコルとアプリケーションによって異なり、通常、最もよくカスタマイズされます。

物理層

物理層は、デバイス間の電気的な互換性を確保し、データリンク層に対してクロックを同期させます。

接続インタフェース

高速シリアルプロトコルが異なれば、送信機と受信機の接続インタフェースに定義される要件も異なります。これによって、接続時に送信機と受信機の電気的互換性が保たれます。高速シリアルリンクの電気信号は、1 Gbpsを超える速度の通信に必要な極端な立ち上がり時間と立ち下がり時間の実現や、電磁放射線を最小限に抑え、コモンノードノイズを除去して耐ノイズ性を向上させることが困難です。さらに、このような速度でピーク-ピーク値の電圧が1 Vを超えることはほとんどなく、通常、LVDS (Low-Voltage Differential Signaling)、ECL (Emitter-Coupled Logic)、またはCML (Current-Mode Logic) といった規格が使われます。

クロックデータリカバリ

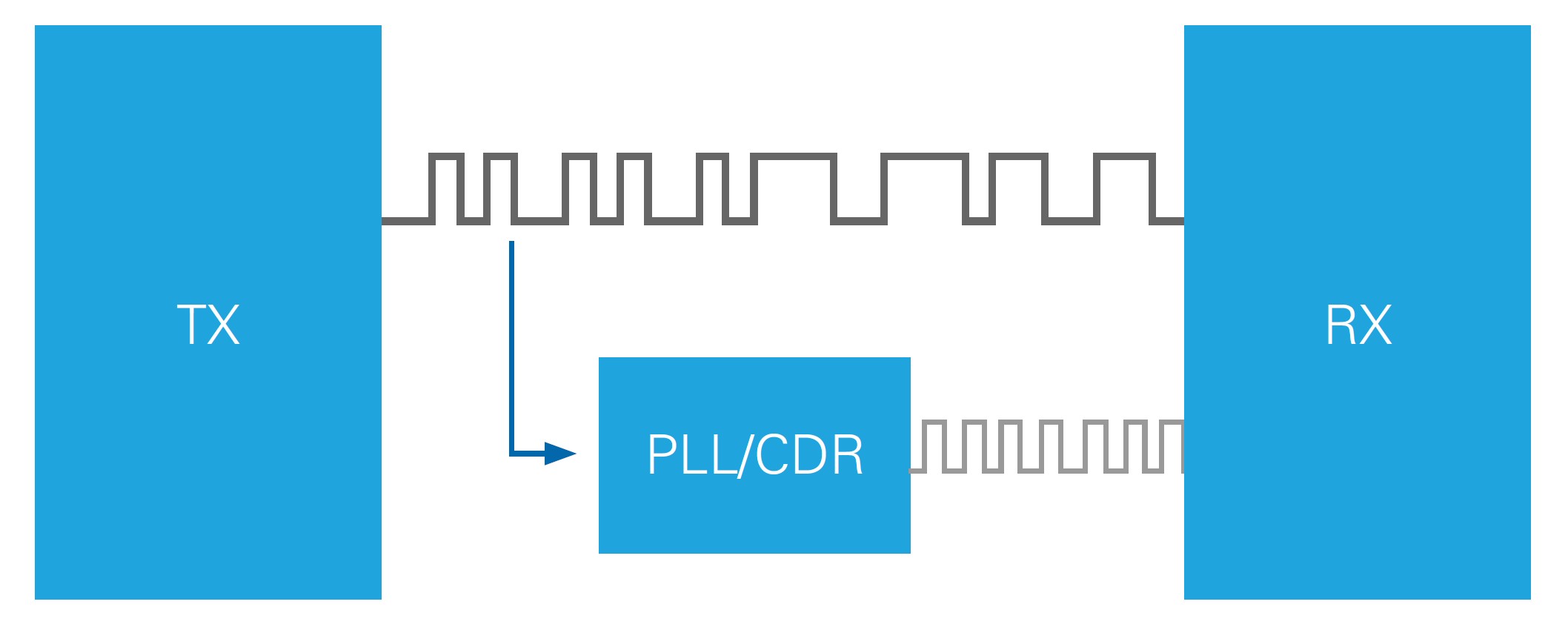

高速シリアルリンクの物理層が持つもう1つの重要な機能は、クロックデータリカバリ (CDR) です。CDRは、データを受信する側のデバイスが、実際のクロック信号なしで、受信データのクロック情報を抽出できる機能です。データリンク層は、符号化による頻繁なビット遷移を確保することで、これを実現します。これにより、位相ロックループ (PLL) および位相補間 (PI) 回路が送信クロックを再作成し、それを使用してタイミングエラーを最小限に抑えながら受信データストリームをキャプチャできます。

図4: データリンク層で符号化を行うことで、0と1の頻繁なシフトが行われるため、CDR回路は受信データを位相同期ループさせ、符号化したデータビットを同期サンプリングすることができます。

信号整合性の考慮点

ビットシフトを行うデータを5 GHz以上のレートで伝送すると、アナログ設計に課題が発生します。RF設計特有の周波数範囲における伝送速度となるため、信号整合性の問題が生じます。そこで、高品質のPCB、コネクタ、ケーブルを使い、こうした高いデータレートで問題なく通信できるようにする必要があります。また、PCBの設計者は、高速シリアルリンクの設計時に伝送ラインの理論を理解する必要があります。スタブ、インピーダンス不整合、トレース長の不一致を回避し、信号の歪みを最小限に抑えるための適切なテクニックを使用することが必要です。

イコライゼーション

イコライゼーションとは、周波数応答を増やすために、チャンネルの電気的挙動を反作用させる処理です。この処理は十分なリンクマージンを確保するために、通信リンクの送信機あるいは受信機のどちらかで行われますが、このイコライゼーションという用語は通常、受信機の側で使われます。高速シリアル信号がPCBトレースを通過し、コネクタやケーブルを経由して、受信機に到達するとき、信号の周波数成分全体に対して減衰が均等に加わらず、信号に歪みが生じます。マルチギガビットトランシーバ (MGT) のイコライゼーション設定は、信号がサンプリングされる前に、信号の周波数成分に応じてゲインまたは減衰を適用し、信号およびリンクのマージンを十分に確保します。多くのMGTに搭載されている自動イコライゼーションは、最適な設定を自動的に検出し、継続的にイコライザーをその設定にアップデートします。

プリエンファシス

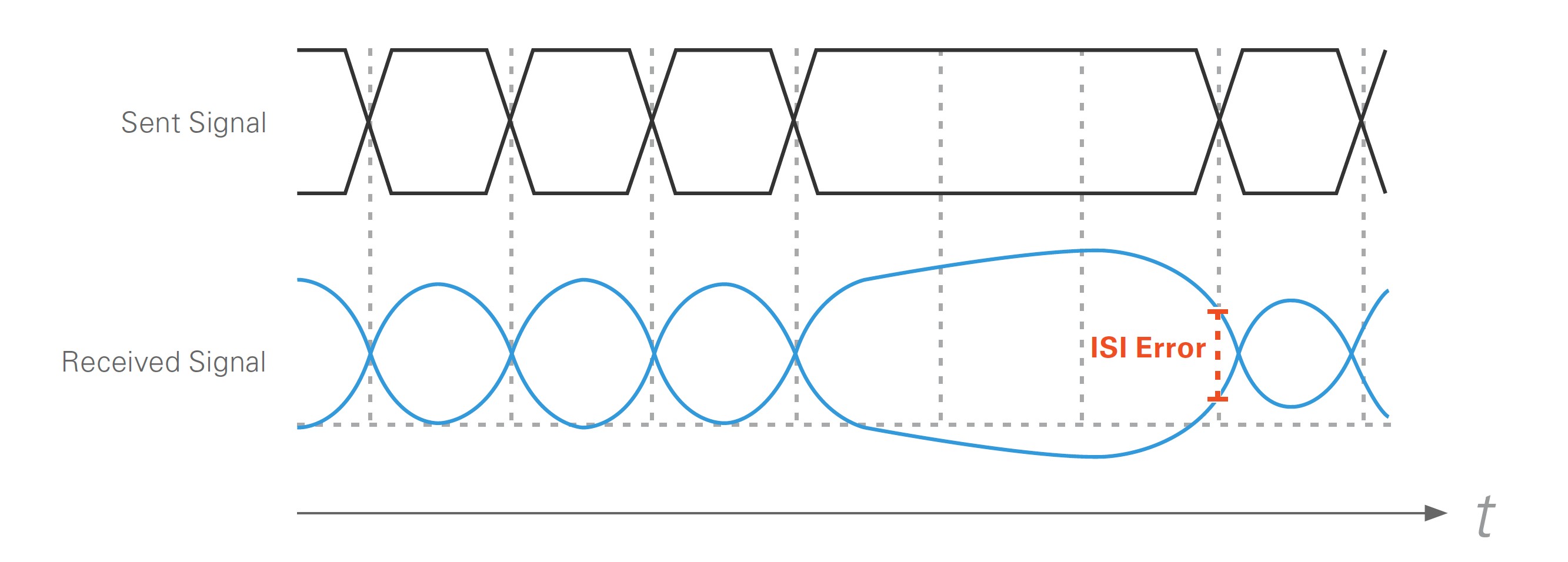

プリエンファシスとは、通常、高速シリアルリンクの送信機側のイコライゼーションを指します。主に、シンボル間の混信 (ISI) によって生じるアナログの問題を解消するために使用します。高速ラインレートにおいては、ビットデータが伝送中に相互に影響を及ぼします。たとえば、1が3つ連続で伝送され、次に0が1つ伝送される場合、ラインには正のバイアスが形成されているため、データラインがこの0をすぐに0として伝送することが難しくなります。

図5: ISIによる信号の劣化は、ビットがシフトしないことでラインがバイアスを形成し、次に来る逆のビットのシフトがすばやく行われないことで起こります。

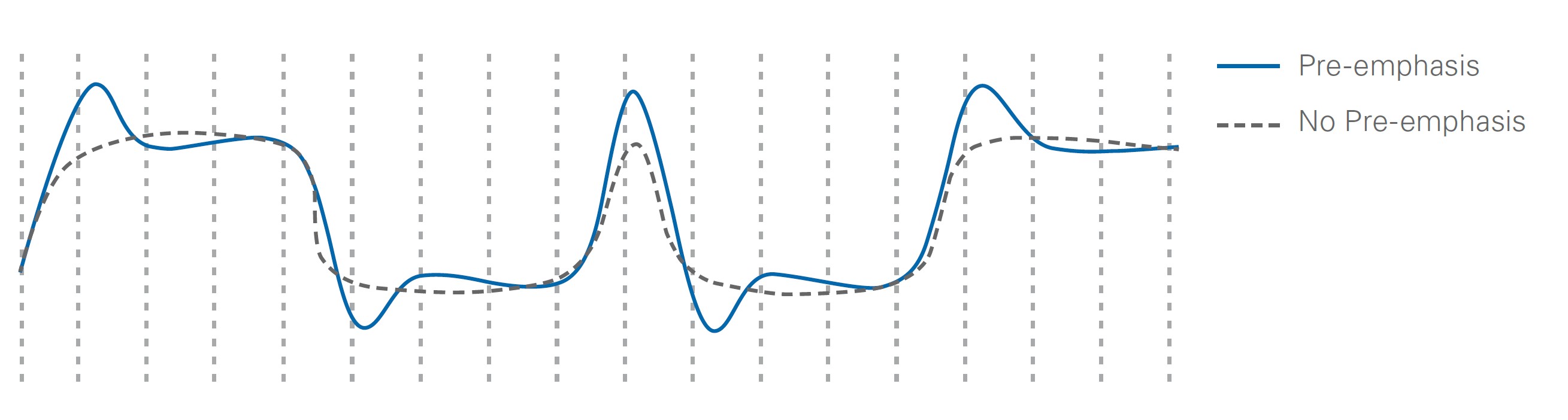

ISIを克服するには2つの方法があります。LowからHigh、あるいはHighからLowへシフトする最初のビットのみに問題があることがわかっている場合は、シフト後の最初のビットのみを増幅することができます。その結果、図6に示す信号が生成されます。

図6: プリエンファシスとは、信号のシフト後に最初のビットを増幅することです。これは、ISIなどの問題の軽減に役立ちます。

さらに一般的な方法を用いて、同様の波形を得るには、最初のビットを増幅する代わりに、最初のシフト後のビットを減衰します。この挙動はハイパスフィルタで実現が可能です。シフトするビット (高周波数) が、シフトしないビットよりも少なく減衰されるためです。

データリンク層

データリンク層は、データを操作することで、信号整合性の向上、正常な通信の確保、物理的なビットのデータへのマッピングを行います。これを可能にする機能は符号化スキームと、アライメント、クロック補正、チャンネルボンディングを行う制御符号です。

符号化スキーム

符号化の目的は、頻繁なビットのシフトを確実に行うことで、正常なCDRを行い、データのDCバランスを維持することです。正常なCDRを行うには、符号化スキームによって、データ信号のビットシフトを十分行い、CDR回路がデータストリームに対する位相同期を維持できるようにする必要があります。ビットシフトが十分でないために、CDR回路内のPLLの同期が維持されない場合、受信機ではデータビットのクロックを同期できず、ビット誤差またはリンク障害が発生します。CDRは、頻繁なビットシフトを行うシンボルの伝送を保証することで実現し、その結果として、オーバーヘッドビットがデータに追加されることになります。

DCバランスもシリアルリンクの機能を維持する上で重要です。DCバランスの量が制限されていない場合、信号が最適なロジックのHigh/Lowレベルから遠ざかってしまい、ビット誤差が発生する可能性があります。DCバランスは、伝送されるシンボルの1と0の数の均衡を保つことで確保されます。DCバランスが維持される信号では、一定の時間にわたって伝送される0と1の数が統計的に等しくなります。

8b/10bの符号化方式

一般的な符号化方式として、8b/10bがあります。8ビットのデータすべてに2ビットを追加することで、符号化のオーバーヘッドが生じます。このような2ビットの追加は、8ビットのデータのビット表記 (シンボル) の4倍のシンボルを供給します。8b/10bエンコーダは、特定のデータワードと制御シンボルにマッピングするために、最も頻繁なビットシフトと最適なDCバランスを備えた定義済みシンボルを選択することで、多くのシンボルオプションを絞り込みます。これらのシンボルはルックアップテーブルに格納され、データの符号化と復号化に使用されます。

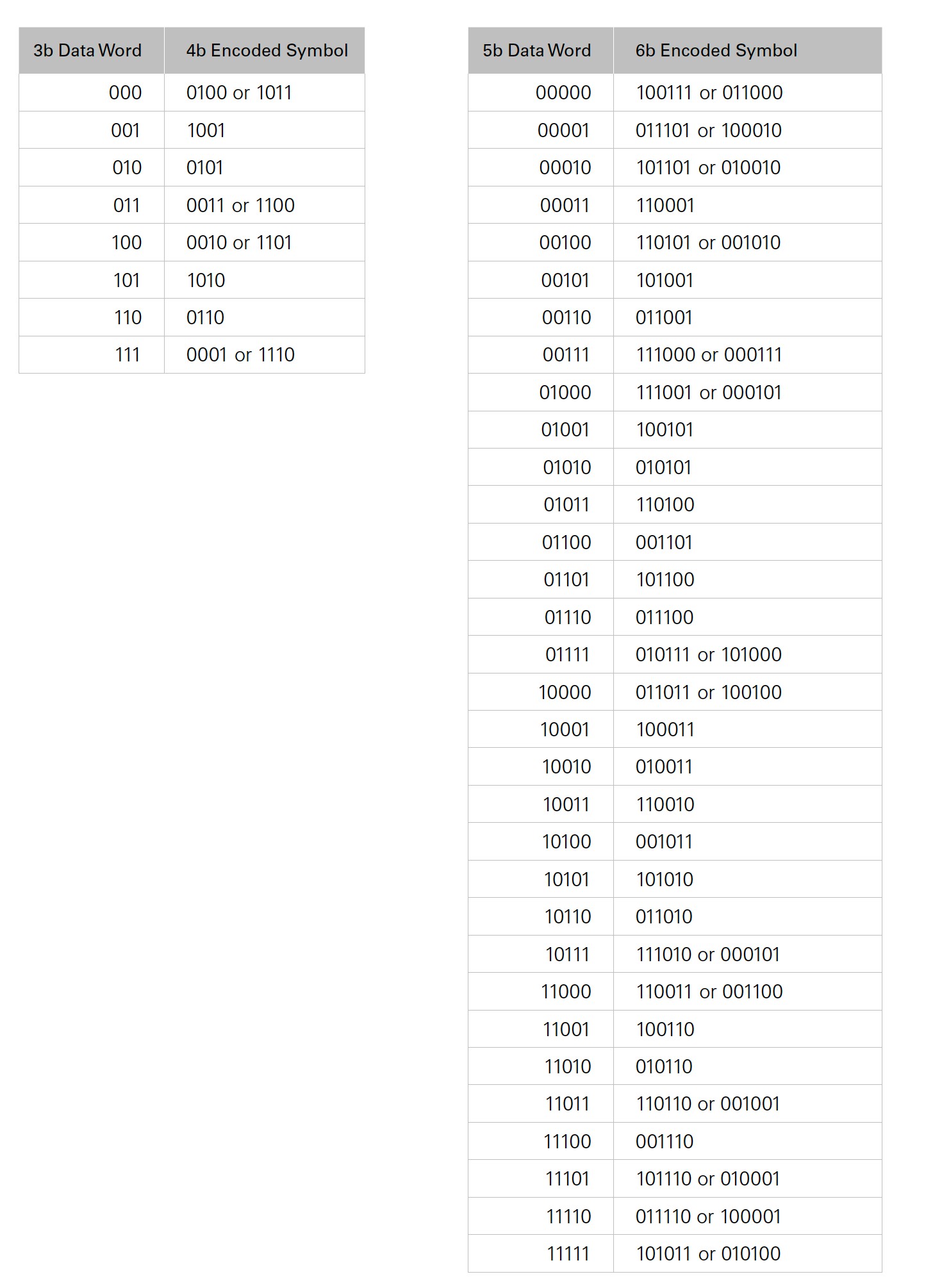

8ビットのデータワードが符号化されるとき、エンコーダはデータワードを5ビットと3ビットに分け、データワードに対して、5b/6bと3b/4bという、別々の符号化を実行します。最下位5ビットは5b/6bテーブルに送られ、最上位3ビットは3b/4bに送られます。

表1: エンコーダは、最上位3ビットを3b/4bテーブルに、最下位5ビットは5b/6bテーブルに送ることで、8bデータワードを符号化します。その後、エンコーダは不均衡に基づいてこれらを結合し、CDR回路に適した頻繁なシフトを行う10bシンボルを形成します。

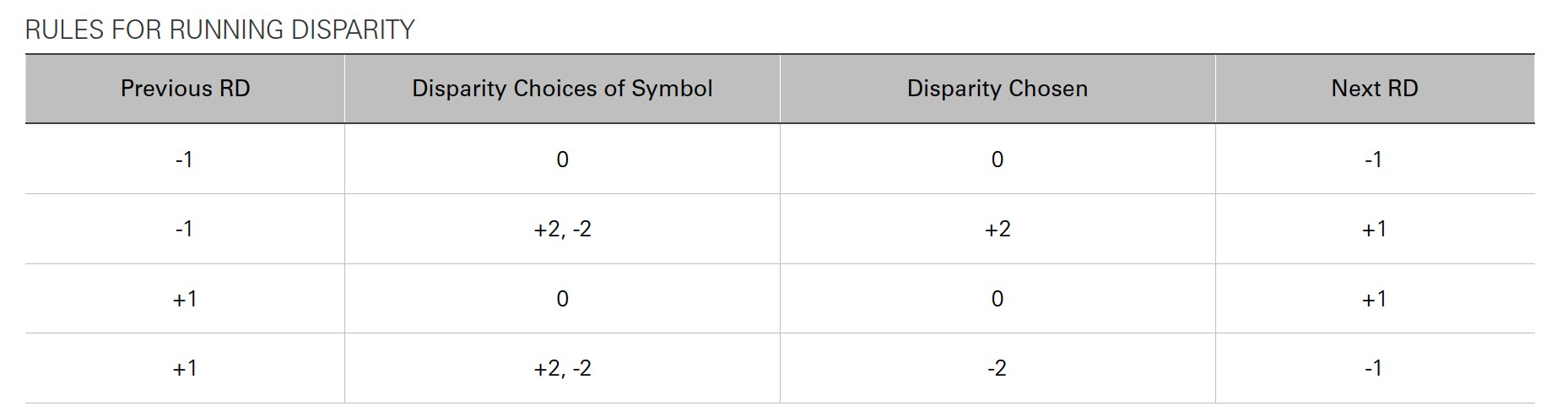

理想的な状態は、すべてのシンボルの0と1の数が等しくなり、DCバランスが維持される状態です。しかし、5b/6bおよび3b/4bテーブルのシンボルにはこれが当てはまらないため、「ランニングディスパリティ」として知られる概念に基づいて判断する規則が実装されました。 これは、伝送された1と0の数の累積差です。8ビットを表すには1と0の数が等しいシンボルが十分にないため、データワードの一部は、0が1より多い1つのシンボルと1が0より多いもう1つのシンボルの、2つのシンボルで表されます。たとえば、1101の3b/4bテーブルのシンボルは、0010としても表記できます。使用するシンボルをどちらにするか選択するとき、エンコーダは常にランニングディスパリティのバランスを取ろうとします。8b/10bのシンボルの差をすべて表すと、常に0、+2、または-2となります。表2は、使用するシンボルを決定するエンコーダのプロセスを示しています。

表2:ランニングディスパリティの規則では、DCバランスが維持できるように、使用するコードワードのバージョンを決定します。

たとえば、データワード10010001を符号化するとします。最上位3ビット (100) が3b/4bテーブルへ送られ、最下位5ビット (10001) が5b/6bテーブルに送られます。これが伝送されている最初のワードの場合、エンコーダは-1という差を想定します。したがって、この例におけるランニングディスパリティは-1ということになります。5b/6bの部分は何も選択しませんが、3b/4bの部分は差が+2か-2かを決定します。ランニングディスパリティが-1のため、差が+2 (1101) の3b/4bコードが選択されます。3b/4bと5b/6bのコードが結合されると、符号化シンボルの合計は1101100011になります。このシンボルが伝送された後、ランニングディスパリティは+1 = -1 + 2となります。

64b/66bの符号化方式

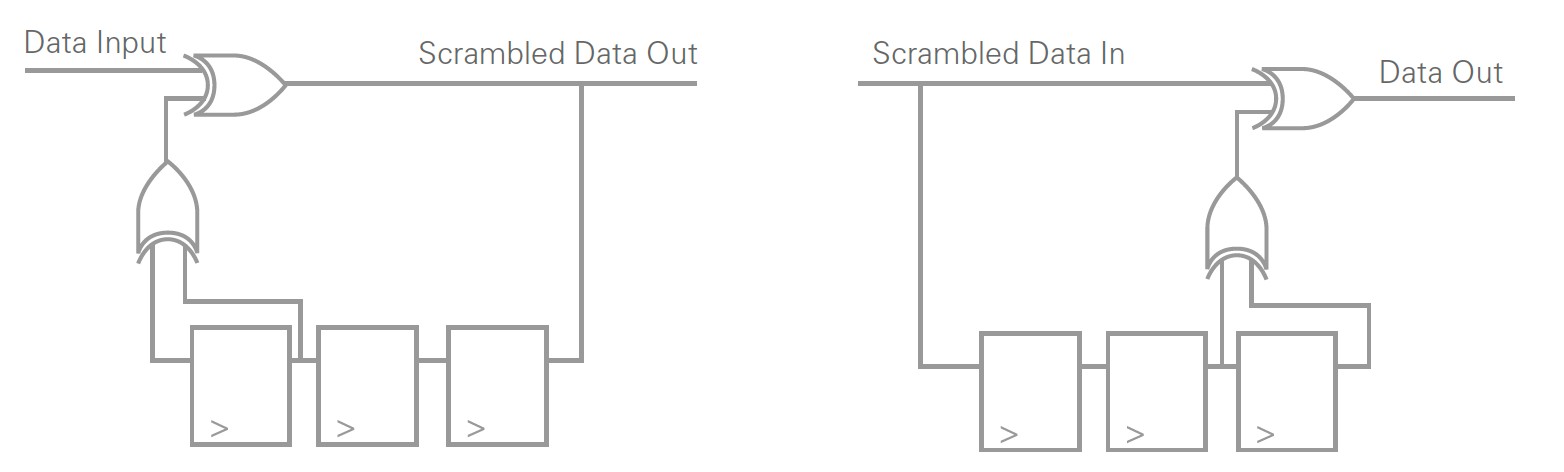

8b/10bの符号化とは異なるアプローチを使用して、64b/66bの符号化でも同様のタスクを実行できます。64b/66bの符号化では、コードテーブルの代わりに、スクランブリングという技術を用います。スクランブリングには、0と1が高確率で連続しないようにスクランブルするハードウェア回路が必要です。スクランブリングすると、符号化データの0と1のパターンは頻繁なシフトによってランダム化されますが、受信側では再び元に戻すことができます。

図7:スクランブリング回路によって、出力データのランダム化が行われ、DCバランスが均衡になりますが、受信側で再びデータを元に戻すことが可能です。スクランブリングはルックアップテーブルとは異なったデータ符号化の方法です。

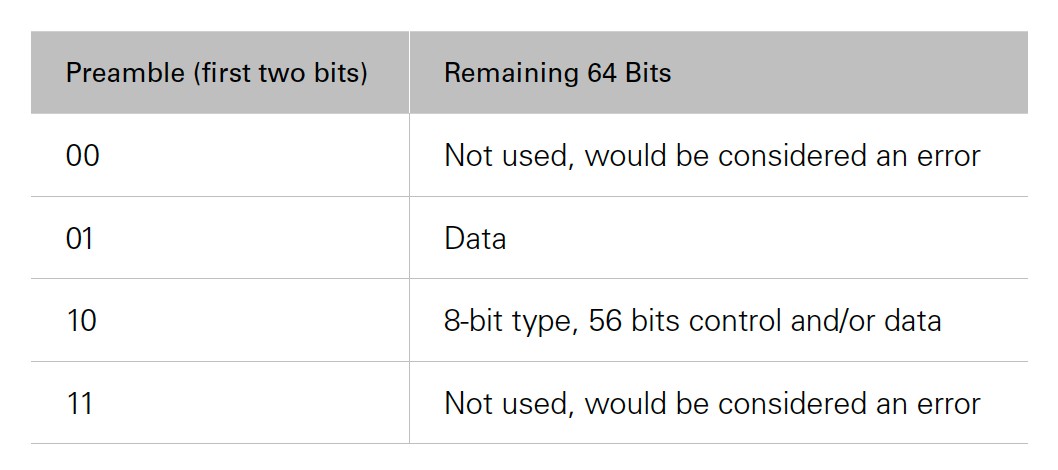

66ビットの最初の2ビットはプリアンブルで、残りの64ビットに関する情報を含んでいます。8b/10bと比較したときの64b/66bの主なメリットはオーバーヘッドを減らせる点です。64b/66bのオーバーヘッドは3%を少し上回りますが、8b/10bのオーバーヘッドは20%です。64b/66bの符号化の欠点の1つは、8b/10bの符号化のようにDCバランスに制限がない点です。スクランブリング回路は0と1のパターンをランダム化する点では大変優れており、統計的に見れば、DCバランスの不均衡はわずかですが、64b/66bの符号化は8b/10b程にはDCバランスが取れません。

表3:64b/66bシンボルの最初の2ビットはプリアンブルです。プリアンブルは次に続く64ビットの復号化に関する情報を含んでいます。表3のプリアンブルの意味は、10ギガビットイーサネットにも当てはまります。

64b/67b

特定の電子機器は、時間の経過とともにDCオフセットに非常に敏感になります。これは、64b/66bの符号化方式にも当てはまる場合があります。DCオフセットが制限されていないため、設計者にとって魅力的ではない可能性があります。こうした状況においては、8b/10bスキームの高いオーバーヘッド (20%) に悩まされることになります。64b/67bでは、1ビットのオーバーヘッドを追加することで、ランニングディスパリティを±96に制限することができます。

送信機はランニングディスパリティを監視し、新たにスクランブリングされたコードワードの差を計算します。新しいコードワードの差の数字が低くなる場合、そのシンボルを伝送します。新しいコードワードによって差の数字が高くなる場合、エンコーダはスクランブリングされた64ビットのビットパターンを反転します (プリアンブルは差が0のため反転は不要)。追加されたビットは反転ビットと呼ばれ、デコーダに対してデータを反転する必要があるかどうかを伝えます。これによって、DCオフセットに反応しやすいチップエレクトロニクス製品でも、低いオーバーヘッドと、制限のあるDCオフセットの両方のメリットを活用できるようになります。

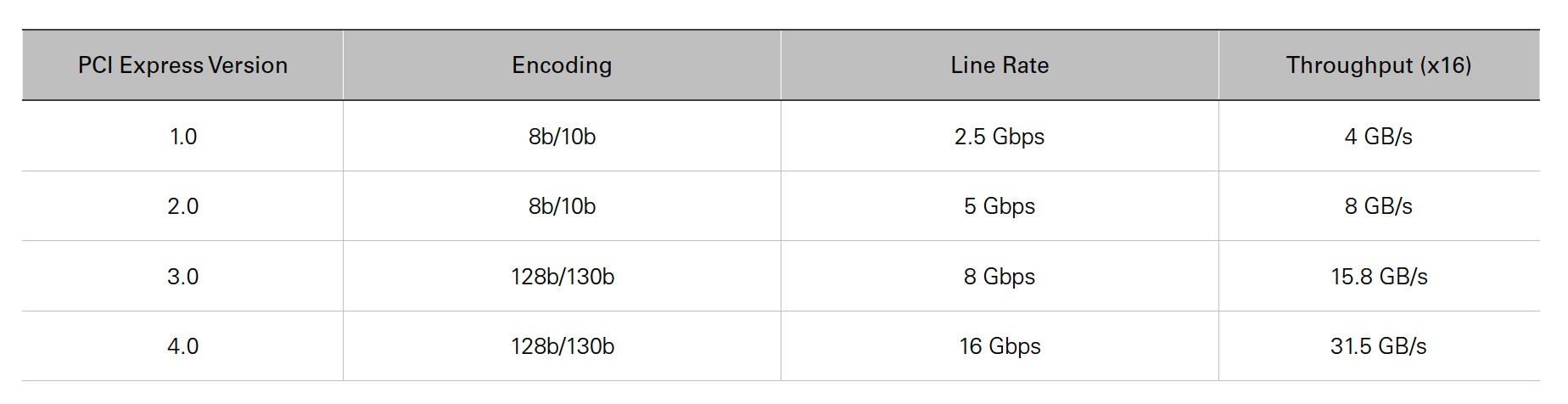

128b/130b

PCI Express 1.0と2.0の両方で8b/10bが使用される一方、PCI Express 3.0と4.0では、実現可能なラインレートでより高いデータスループットを得るため、128b/130bが使用されています。128b/130bは、プリアンブルが2ビットのままでペイロードを2倍にした64b/66bだと言えます。表4は、PCI Expressの仕様を示しています。

表4:この表は、第4世代のPCI Expressの仕様を示しています。PCI Express 3.0と4.0は、128b/130bへ移行することで、より管理しやすいラインレートでデータスループットを向上できるようになりました。

制御シンボル (Kコード)

制御シンボルは、8b/10b符号化を指すときはKコードとも呼ばれており、高速シリアルリンクの重要な機能です。データから差別化できるシンボルであり、受信機が異なる制御管理に使用できるものです。たとえば、復号化の前のバイト境界のアライメント、クロック補正テクニック、チャンネルボンディングによる複数レーン全体でのデータ一貫性などに対する制御です。

アラインメントとカンマ検出

復号化が正しく機能するためには、受信機が符号化データの正しいワード境界を認識する必要があります。受信機は入力されるデータをスキャンして、制御符号 (8b/10bスキームのアラインメントで使用される場合は、カンマとも呼ばれます) を探します。制御文字は符号化されたデータの境界を定義します。受信機がアラインメント符号を特定したら、符号化データのワード境界の概念ができるため、符号化データを復号化ロジックへ送り込むことができます。

クロック補正符号

クロック補正が必要になるのは、送信されたクロック信号が受信されるクロック信号と同じソースに対して同期していないときです。これらのクロック信号が同じ公称周波数であったとしても、クロック周波数の不正確さが少しずつ重なることで、徐々に差が出てきます。エラスティックバッファと呼ばれることもあるFIFO (First-In-First-Outメモリバッファ) があることによって、受信機は送信機と受信機の間に生じたクロック信号の小さな差を把握し、クロック補正を行うことができます。

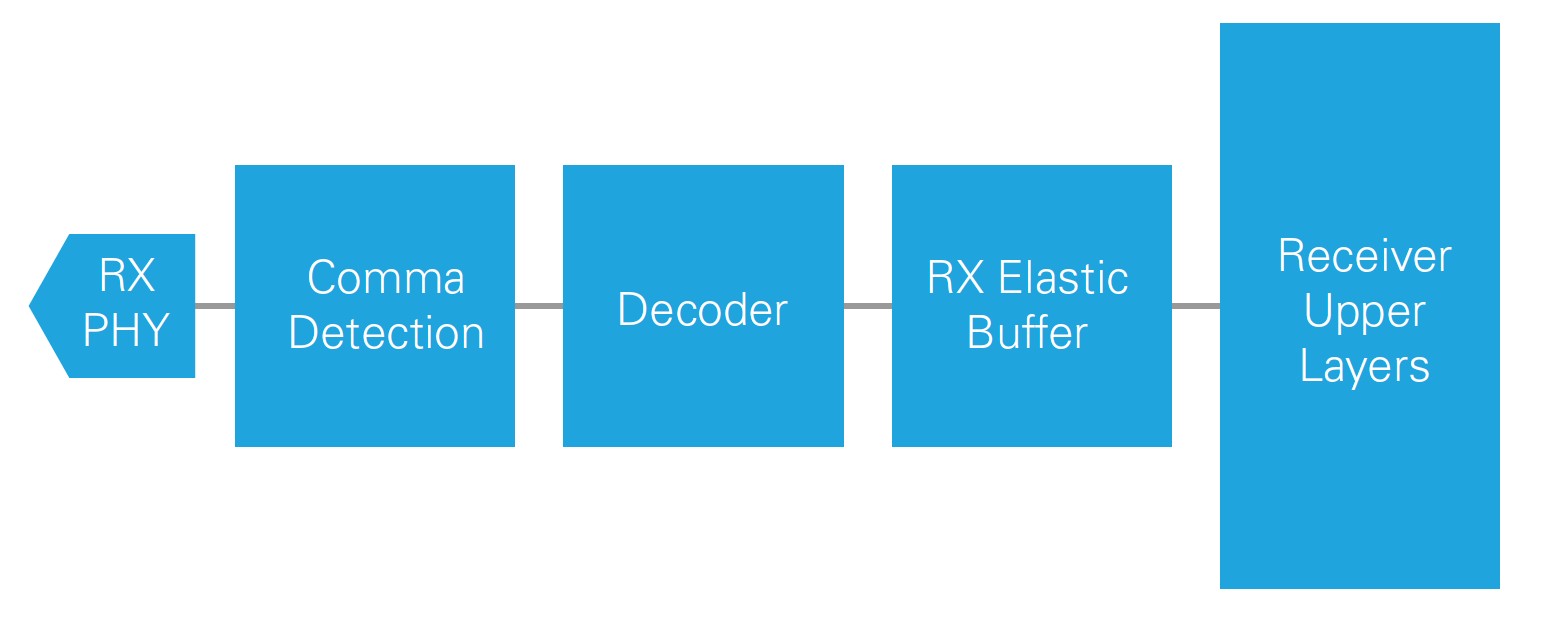

図8:デコーダと受信機の上位層との間にあるRXエラスティックバッファがクロック補正の実行に必要です。クロック信号間のタイミングのずれから生じるエラーを防ぐためにデータをバッファに格納し、基準クロックを共有せずに2デバイス間の通信を可能にします。

クロック補正ロジックは、エラスティックバッファがオーバーフローおよびアンダーフローしないように管理します。受信機のクロックがエラスティックバッファからデータを読み取る速度より、送信クロックの実行速度のほうがやや速い場合、クロック補正が行われないとオーバーフローが起こることがあります。受信機の読み取りロジックより、送信クロックの速度のほうがやや遅い場合、クロック補正が行われないとアンダーフローが起こることがあります。

クロック補正の符号として、制御符号が使用されます。送信機は実際のデータにこのクロック補正符号を周期的に挿入して送信します。また、送信されるクロック補正符号の周波数は、アプリケーションおよびハードウェア設計のクロック補正ニーズによって決まります。受信機のクロック補正ロジックは、受信機のエラスティックバッファがアンダーフロー状態になりそうになると、追加のクロック補正符号を挿入して、それを防ぐことができます。また、エラスティックバッファがいっぱいになり、オーバーフロー状態になりそうになると、バッファに格納されたクロック補正シーケンスを破棄して、データのためにスペースを空けることができます。

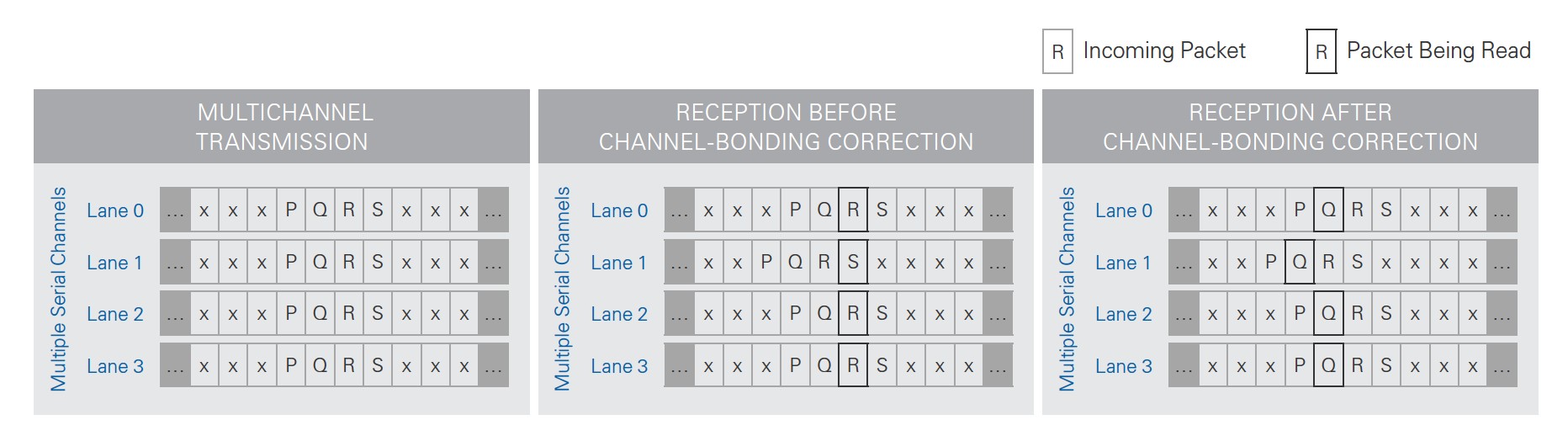

チャンネルボンディング

ラインレートと符号化のスキームが、必要なデータスループットを1つのシリアルレーンで達成できない場合、複数のレーンを使用することがあります。たとえば、HDMI規格は3つのシリアルデータレーンを使用して、データの合計帯域幅を実現します。複数レーンを使用してデータを送信すると、伝播遅延が生じ、データが受信機の各受信レーンに異なるタイミングで到達します。アプリケーションによっては、受信機のすべてのレーンに対してデータのアラインメントが必要になり、このプロセスのことをチャンネルボンディングと呼びます。クロック補正に使用される受信機の各受信レーンのエラスティックバッファは、チャンネルボンディングにも使用されます。

チャンネルボンディングを可能にするには、特別な制御符号を選択して、チャンネルボンディング用に用意する必要があります。シリアルリンクには1つのマスタレーンがあり、その他はスレーブと見なします。マスタレーンとすべてのスレーブレーンが送信機から同時にチャンネルボンディング符号を送信します。受信側のマスタレーンがエラスティックバッファの特定の位置にチャンネルボンディングのシーケンスを見つけると、すべてのスレーブレーンに対して、それぞれのチャンネルボンディングのシーケンスを探すように指示を送ります。すべてのエラスティックバッファの読み取りポインタは、チャンネルボンディングのシーケンスが格納された場所のオフセットに合わせて調節されます。各データレーンが独自のエラスティックバッファに対して独自のオフセットを持っているため、受信機は各エラスティックバッファの異なる場所から読み取りを行い、最後にアラインメントの取れたデータを読み取ることができます。

図9:チャンネルボンディングは各受信レーンのエラスティックバッファの読み取りポインタを変更し、受信機が複数のデータレーンにわたって同期したデータを読み取れるようにします。

アイドル符号

制御符号には他にも重要な使用例があり、その1つがアイドル符号です。クロックデータリカバリが位相同期を維持するために、送信機は継続的にビットデータを送信する必要があります。送信するデータがない場合は、アイドル符号を送信する必要があります。これもプロトコルが決める制御符号で、受信機はこの符号が真のデータではないことを認識しています。

その他の上位層

その他の上位層はデータリンク層の上に位置し、特定のニーズに合わせて通信を調整します。上位層の機能に対して特定の規格を持つプロトコルもあれば、自由に決めることができるプロトコルもあります。一般的な通信のカスタマイズとしては、エラーチェック/修正やパケットベース通信のヘッダ情報、リンクのステータス情報などがあります。

データリンク層と物理層の上の層は、アプリケーション固有のニーズに合わせて最も一般的にカスタマイズされた層です。一般的な上位層のカスタマイズの例として、巡回冗長検査 (CRC) と前方誤り訂正 (FEC) を使ったエラー検出/修正があります。データ転送効率のトレードオフとして、スキームを使用してエラーを検出または修正できます。CRCは、伝送データにビットエラーがあるかを検出する規則を実装しますが、そのエラーを修正することはできません。アプリケーションをカスタマイズしてデータを再要求できます。対照的に、FECの場合は伝送データにエラー修正情報が含まれており、これによって、受信機では限られた量のビットエラーからの回復が可能になります。これは、チャンネルにノイズが多い場合や、通信レートが高すぎて信号整合性によるビットエラーが多い場合に便利な機能です。FECを設計に含めるかどうかは、データレートの効率と信号整合性の要件の厳しさとのトレードオフになります。

まとめ

正常な通信を確立するには、高速シリアルリンクの複数の層で多くの課題があります。各レベルで異なる概念を把握することで、各層の実装とテストが可能になります。ある層が機能するには、その下位層が正常に機能している必要があります。物理層とデータリンク層に定義された多くの仕様の1つを使用することで、低レベルの詳細を独自に決定する必要はありません。標準的な物理層とデータリンク層を使うことのもう1つのメリットは、こうした下位レベルのすべての詳細を実装するインターネットプロトコル (IP) が使用できることです。その大変良い例がXilinx社のAuroraプロトコルです。軽量のデータリンク層プロトコルを実装する無償IPで、ポイントツーポイントシリアル通信に使用できます。これにより、クロック補正、チャンネルボンディング、アイドル文字、エンコーディング/デコードなどの細かな細部を抽象化できるため、アプリケーションに特化した上位層に集中することができます。

サイズの小型化、消費電力の縮小、性能の向上を同時に実現する高速シリアルリンクは、急速に普及しています。通信業界では、ラインレートのさらなる高速化や、ビッグデータの世界の実現のために、高速シリアル技術を継続的に改善し続けています。