PXI高速シリアル計測器の概要

概要

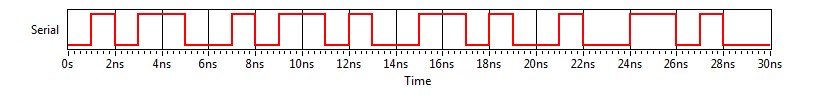

PXI高速シリアル計測器は、高速シリアルプロトコルの検証、インタフェース、テストに役立ちます。選択されたPXIe-7903やPXIe-7902などの一部の高速シリアルデバイスは、大量のデータ移動とインラインリアルタイム信号処理を実現するために高性能FPGAコプロセッシング機能を必要とするエンジニア向けに設計されています。このハードウェアにはXilinx Kintex™ UltraScale+™または7シリーズFPGAが搭載されており、LabVIEW FPGAモジュールを使用してプログラム可能なため、アプリケーション固有のカスタマイズと再利用を最大限に高めることができます。また、FPGAマルチギガビットトランシーバ (MGT) を活用して、最大28.2 Gb/秒のラインレートを実現し、最大48個のTX/RXレーンに対応します。PXIプラットフォームに基づくため、PXIクロック機能とトリガをはじめ、ディスク間データストリーミングやピアツーピア (P2P) ストリーミングなどの高速データ移動機能を最大レート7 GB/秒で利用できるというメリットがあります。

内容

高速シリアルインタフェースの登場

求められるデータ帯域幅がかつてないほどに高まる中、有線インタフェースはクロックレートと並列性を向上させることで対応しています。ただし、従来のパラレルデータバスでは、クロックとデータライン間のわずかなスキューにより、インタフェースのビット誤り率を脅かされる可能性があります。シリアルデータリンクは、特定の差動トレースのペアのデータストリームにクロックを埋め込むことでこの問題を解決し、クロックとデータ間のスキューの可能性を排除します。この機能には、インタフェースの受信側で追加の電子部品が必要となるほか、クロック回復のために追加のエンコーディングが必要ですが、これによりデータレートが劇的に高速化するので、帯域幅のニーズを満たすことができます。

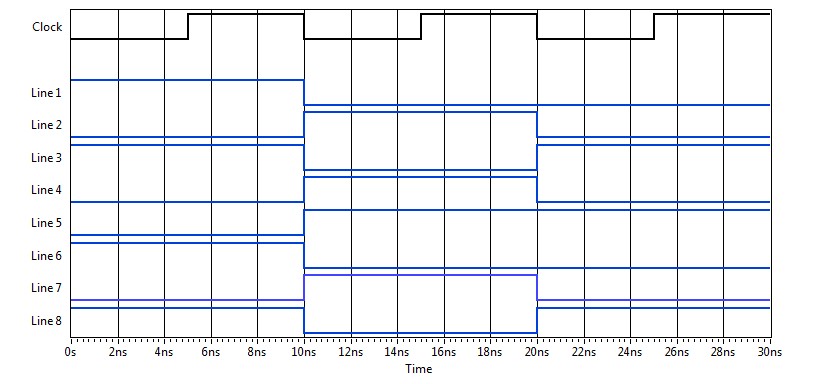

図1.同じデータ帯域幅での並列クロック (黒) とデータ (青)、およびデータに埋め込まれたクロック (赤)。

最新のデータ通信プロトコルは、そのようなパラレルインタフェースから、PCI Express、HDMI、DisplayPortビデオ規格、IEEE 1394b、USB 3.0などの高速シリアルインタフェースへと移行していきました。設計およびテストエンジニアにとって、これらのインタフェースの検証は、新しいテストハードウェアを必要とする新たな難題となります。従来、エンジニアは高価なオシロスコープやビット誤り率テスタ (BERT) を使用して、物理インタフェースの特性を評価し、プロトコル固有のアナライザとジェネレータを使用して、プロトコルスタックが正しく実装され、データの送受信が効率よく行われていることを検証していました。ただし、自動V&Vおよび製造テストでは、これらのシリアルインタフェースをテストするための最適化されたハードウェアは存在しません。オシロスコープとビット誤り率テスタは、対象範囲のわりに高価で低速ですが、一方でプロトコル固有のハードウェアは自動テストシステムに組み込むには柔軟性が十分でないことがよくあります。一方、プロトコル固有のハードウェアは、他のテストに再利用したり、他のテスト対象デバイス (DUT) に転用することはできません。

FPGAは、これらの課題に対するソリューションを提供します。最新の高性能FPGAには、一般にさまざまな高速シリアルインタフェースに対応する複数のマルチギガビットトランシーバ (MGT) が搭載されています。適切なプロトコル固有のIP、LabVIEW FPGAモジュールによるグラフィカルプログラミング、PXIエコシステムの利点を組み合わせると、新しい高速のソフトウェア設計型シリアル計測器となります。

高速シリアルモジュール

表1.PXI高速シリアル計測器。

¹8 Gbpsと9.8 Gbpsの間の達成可能なラインレートのギャップ。

²PXIe-7903は2スロットモジュールです。

高いデータレートと20 GHzを超えるアナログ帯域幅を持つアプリケーションでは、接続とケーブル配線が重要です。PXIe-7903、PXIe-7902、PXIe-6594、PXIe-6593、PXIe-6592、PXIe-6591にはそれぞれ、特定の使用例で接続を簡素化するための異なるオプションがあります。3つのモジュールはすべて、ユーザがプログラム可能なXilinx FPGAをコアに備えています。

これらの計測器の重要な技術が、Xilinx 7シリーズGTXトランシーバです。800 mVpp (通常最大で1000 mVpp) の信号振幅によって電力消費と放射妨害波を低減する差動インタフェースである電流モードロジック (CML) と、高データレートでの反射とその結果起こる信号異常を最低限に抑える100Ωの差動 (1シグナル経路につき50Ω) インピーダンスを利用します。さらにそれらのトランシーバは、ケーブルの長さを補完する信号忠実度を最大に高めるための送信振幅がプログラム可能となっています。また送信のプリエンファシス/ポストエンファシスと自動適応レシーバイコライザによって、アナログチャンネル/ケーブルの帯域幅の制約を克服しています。

すべての高速シリアルインタフェースには、ラインレートの整数除数で動作する基準クロックが必要です。柔軟性を最大に高めるため、GTXトランシーバには、基準クロックを最大100回乗算してシリアルデータレートを生成する位相ロックループ (PLL) が搭載されています。また、最大80倍のシリアル/パラレルおよびパラレル/シリアル変換器も搭載していますので、FPGAクロック周波数を制限しつつ、高いシリアルデータレートを実現します。さらに、トランシーバには8b/10b、64b/66b、64b/67bエンコーディング/デコーディング構造が内蔵されていますので、クロックリカバリのために十分な数の信号遷移が確保され、汎用のFPGAリソースの消費も防ぐことができます。『Xilinx 7シリーズFPGAs GTX/GTHトランシーバユーザガイド』では、Xilinx GTXトランシーバについての詳細が記載されています。

計測器に搭載されたXilinx FPGAは、高速シリアルトランシーバを提供する以外にも、いくつかの重要な役割を果たします。これらは使用しているプロトコルのロジック、およびハードウェア構成およびシステム全体でのデータの生成、受信、移動のためのアプリケーション固有のユーザロジックを実装します。

図2. PXIe-7903ハードウェアアーキテクチャの主要インタフェースおよびデータレート。

表2. PXI高速シリアル計測器と各FPGAの仕様。

FPGAには最大20 GBのオンボードDDR3 DRAMが直接接続されており、ユーザ定義のアクセスパターンで最大25 GB/秒 (理論上の最大値) の速度で読み書きすることができます。また、FPGAにはPXI ExpressバックプレーンへのPCI Express x8 Gen 3インタフェースが搭載されていますので、ホストとディスク間のデータ転送や、単方向で7 GB/秒、双方向で各方向につき2.4 GB/秒 (合計で4.8 GB/秒) で、システム内の他のFPGA対応デバイスとのピアツーピア接続が可能です。

低ジッタで高忠実度の基準クロックは、あらゆる高速シリアル通信システムで極めて重要なコンポーネントです。すべてのモジュールにオンボードの任意レートのシンセサイザが搭載されており、PXIe-6591、PXIe-6592、PXIe-7902を搭載したXilinx GTXトランシーバでは500 Mbps~8 Gbps (最大デバイス速度9.8 Gbps) の全範囲でMGTが動作します。他方で、PXIe-6593、PXIe-6594、PXIe-7903は、最小ラインレートと最大ラインレートの間にこのようなギャップが生じることなく動作します。PXIe-6591、PXIe-6592、PXIe-6593、PXIe-6594は、内蔵基準クロックをエクスポートするためのフロントパネル同軸接続を備えており、4つのモジュールすべてに外部基準クロックをインポートするための接続があります。最後に、このデバイスはPXI Express 100 MHzまたはDStarAバックプレーンクロックを、MGTのリファレンスとしてルーティングすることができます。

ソフトウェア

ソフトウェア設計型計測器は、機能は固定機能の計測器と同じですが、オープンなユーザプログラマブルFPGAを使用して計測ハードウェアをカスタマイズすることができます。PXI高速シリアル計測器でさまざまなプロトコルやアプリケーションをサポートためには、このレベルのカスタマイズが必要です。そのため、これらのデバイスをプログラミングするための単一の高レベルAPIはありません。代わりにホスト (CPU) とFPGAコードの両方に対してLabVIEWソフトウェアを使用して直接プログラムし、その2つをローレベルのNI-RIO APIで接続するという方法を取ります。短時間での開発着手を支援するため、異なるプロトコルの使用方法や計測器のさまざまな使用モデルを示すサンプルをご用意しています。

オープンなFPGAなら、他の計測器では不可能なレベルのカスタマイズが可能です。何よりもまず、計測器が構成されているシリアルプロトコルを実装しています。これだけで、PXIe-7903、PXIe-7902、PXIe-6594、PXIe-6593、PXIe-6592、PXIe-6591は、さまざまな標準およびカスタムシリアルプロトコルをサポートできます。プロトコルのみならず、ハードウェア機能をユーザが定義することで、これまでは不可能だったようなタイプのテストが可能になります。たとえば、FPGAでのアルゴリズムデータ生成により、そのような波形のダウンロードに必要な波形ストレージメモリとシステム帯域幅を減らすことができるため、テストスループットが向上します。応答比較、インテリジェントトリガ、データ削減/圧縮などのアルゴリズムデータ解析を行えば、ホストCPUが処理するデータ量を劇的軽減できるため、テストにかかる時間を短縮できます。

ユーザ定義のDRAMアクセスで、DRAMを刺激領域と応答領域に柔軟に分けることが可能となります。圧縮・解凍のカスタムアルゴリズムが利用できるので、DRAMのサイズと帯域幅を最大限に活用できます。標準の波形記録・再生は可能ですが、プロトコル、ラインレート、レーン数、I/O帯域幅によってはDRAM帯域幅を超えることがあります。最後に、高速シリアル計測器とホストまたはその他計測器との間でのユーザ定義のデータ移動は、システムレベルの統合において極めて高い柔軟性を誇ります。たとえば、高速デジタイザでアナログデータをデジタルサンプルに変換し、NIピアツーピア転送を利用してそのデータを7 GB/秒のレートで高速シリアル計測器に転送して、そのデジタルサンプルをシリアルプロトコル経由で外部デバイスに送ることが可能です。また別の方法では、高速シリアル計測器はシリアルデータストリームを捉えてホストCPUに転送し、最終的に高帯域RAIDアレイの数時間あるいは数日分の連続ストレージに最大7 GB/秒で送ることができます。

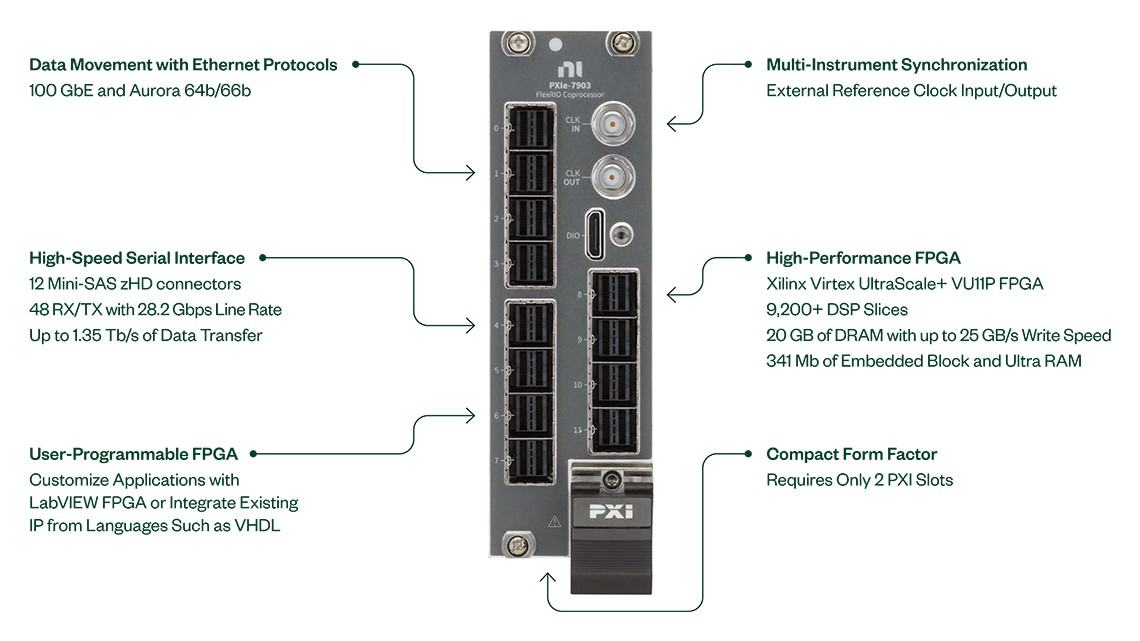

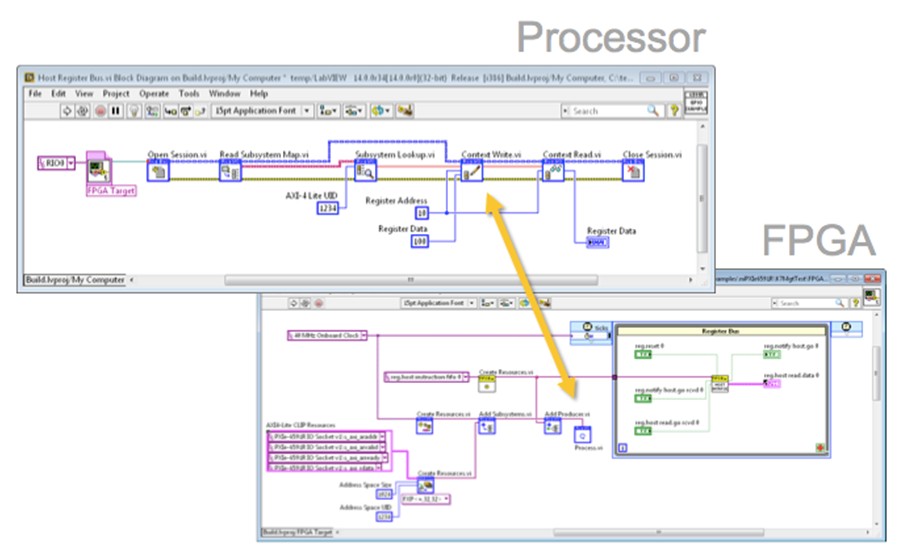

LabVIEW FPGAを使用すると、そのような高速シリアル計測器の構成とプログラミングが容易になります。図3は、LabVIEWを使ってアクセス可能な主要インタフェースと、それを表すコードを示しています。LabVIEW FPGAとNI-RIO APIは、ホストCPUとFPGA間のPCI Expressベースのデータ転送において、レジスタの読み取り/書き込みや双方向DMA転送など、効率的なメカニズムを提供します。DRAMアクセスは、一般に低水準ハードウェア記述言語 (HDL) による管理が必要な難度の高いインタフェースですが、抽象化された要求、読み取り、書き込みインタフェースにより簡素化され、同時に高スループットと基本の読み取り/書き込みアービトレーションを実現します。GTXトランシーバの構成は一般的にプロトコル固有であり、トランシーバ構成を内蔵した多くの高速シリアルインタフェース (HDLまたはネットリスト) 向けのIPがすでに数多く存在しています。このシリアルプロトコルインタフェースは、ソケット化されたコンポーネントレベルIP (CLIP) インタフェースを介してLabVIEW FPGAで利用可能です。CLIPノードを使用すると、LabVIEWで実装されていないコードの同期操作ができますが、LabVIEW FPGAダイアグラムへのインタフェースは明確に定義されています。一般的なシナリオでは、Xilinx Vivado IPカタログに含まれるプロトコル固有のXilinx IP (トランシーバ構成を含む) と、VHDLのシンレイヤを使用して、LabVIEW FPGAへのインタフェースを定義します。LabVIEW FPGAは任意のユーザロジックを実装するための各種言語を提供していますので、プロトコルの実装後は、条件判断、ステートマシンの実装、DUT制御、信号処理、データ移動などを組み込むことができます。

図3. LabVIEW FPGAを使用すると、PXI高速シリアル計測器でユーザプログラマブルFPGAの主要な機能にグラフィカルにアクセスできます。

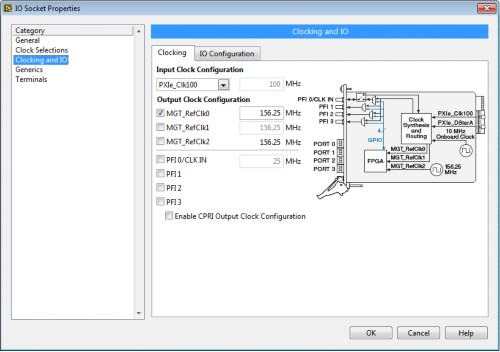

LabVIEWは、ユーザプログラマブルFPGAに実装するロジックを定義するだけでなく、プロジェクト階層と関連する構成ページにより、ハードウェア構成を簡素化することができます。たとえば、それらの高速シリアル計測器の基準クロック構成では、FPGAに電源を投入した際にレジスタに適用されるロジックに加え、複雑なアルゴリズムを使用して、最大4個もの集積回路に適用する多数のレジスタ設定を特定する必要があります。LabVIEW FPGAでは、これがオプションをグラフィカル表記したダイアログボックスとして表示され、設計ルールとガイドによって有効な構成が強化されます。この手法により任意クロックシンセサイザとルーティング回路の構成が簡素化され、数時間あるいは数日かかっていたタスクが数分で実行できるようになります。

図4. LabVIEW FPGAは、複雑なプロセスを簡素化するクロック構成用の直感的なグラフィカルインタフェースを提供します。

コードの再利用を可能にし、一般的なタスクを簡素化するため、PXI高速シリアル計測器は特定の計測器の設計ライブラリをサポートしています。これは相互に動作可能で汎用機能を備えたLabVIEWインタフェースを持つホストおよびFPGAコードライブラリです。Instruction Frameworkは、ランタイムでの動的ハードウェア構成用計測器設計ライブラリです。それらのシリアル計測器では、ほとんどのハードウェア機能 (クロック構成など) をLabVIEWプロジェクトで静的に構成できますが、ユーザはInstruction Frameworkを利用してアプリケーションに特化したファームウェアパラメータを制御できます。たとえば、Instruction Frameworkにより、FPGA上のAXI-4 Liteインタフェース経由で利用できるレジスタ設定のホスト構成が簡素化されます。これは通常XilinxシリアルプロトコルIPにあります。

図5.AXI-4 Liteインタフェースを介してレジスタを読み書きするためのプロセッサおよびFPGAコード。

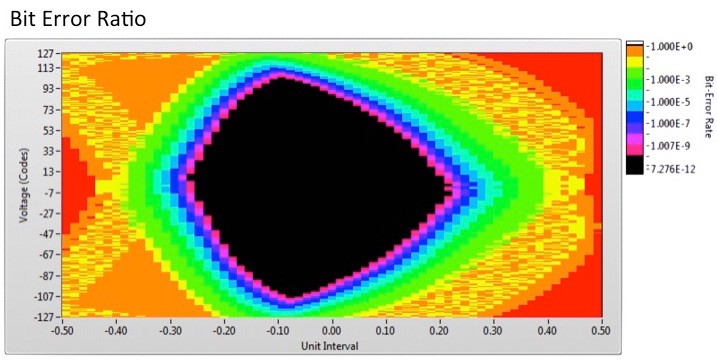

Instruction Frameworkをベースに作成されたEye Scan計測器設計ライブラリは、高速シリアル受信チャンネル向けにデバッグ機能を提供します。Xilinx GTXトランシーバは、各チャンネルに2つの受信機コンパレータを備えています。一方のコンパレータが、回復されたクロック周波数と位相に基づきシリアルアイの中心を自動で追跡し、もう一方のコンパレータは振幅と位相が個別に変動可能になります。後者のコンパレータのパラメータを変化させ、前者のコンパレータの結果と比較すると、Eye Scan計測器設計ライブラリは、インタフェースのリンクマージンの特定に便利で、Xilinx GTXトランシーバのビット誤り率フロアに対し高精度の統計的アイダイアグラムを作成することができます。さらに、Eye Scan計測器設計ライブラリは独自の組み合わせのハードウェアリソースを使用するため、他のプロトコルIPと共存し、他のアプリケーション専用機能と同時に実行することが可能です。

図6. PXI高速シリアル計測器用LabVIEW計測器設計ライブラリには、ループバック構成を使用して統計アイスキャンを実行するための参照設計が含まれています。

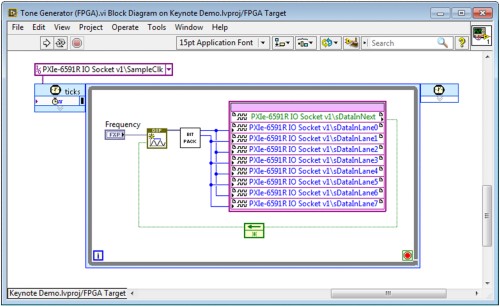

これらの計測器設計ライブラリ以外にも、他のNIソフトウェア設計型計測器はDRAMベースのマルチレコード集録/生成など、さまざまな役立つ関数のライブラリを提供しています。PXIe-7903、PXIe-7902、PXIe-6594、PXIe-6593、PXIe-6592、PXIe-6591では正式にサポートまたはテストされていませんが、計測器設計ライブラリのハードウェア非依存性によっては、PXI高速シリアル計測器でも使用できる場合があります。

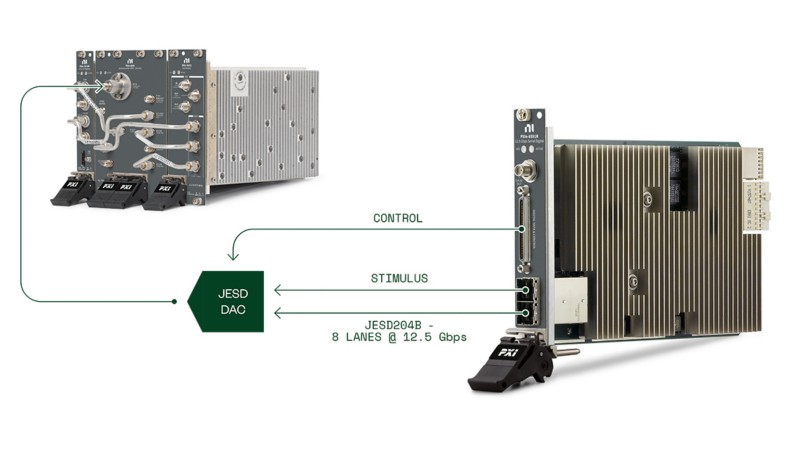

図7.エンジニアはDSP計測器設計ライブラリを使用して、正弦波を合成し、シリアルJESD204Bプロトコル経由でD/A変換器に転送することができます。

プロトコル

PXI高速シリアル計測器のXilinx GTXトランシーバは、さまざまなプロトコルをサポートしています。NIでは、一般的なプロトコルといくつかのアプリケーションパターン用のLabVIEWアーキテクチャを統合する方法を示すために、多数のソフトウェアサンプルを提供しています。各サンプルにはサポートする計測器向けのコンパイル済みのFPGAビットファイルと、関連のソースコードとプロトコルIPが含まれています。最終的なアプリケーションでこのコードを修正する必要がある場合は、一部のプロトコルではXilinxのIPライセンスでFPGAを再コンパイルする必要があります。このプロトコルIPは、XilinxまたはAvnetやDigiKeyなどの販売者から購入いただけます。

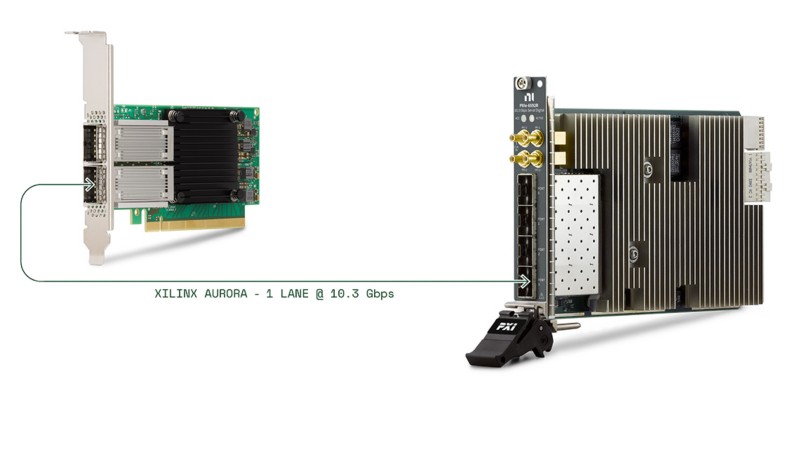

Xilinx Aurora

Xilinx Auroraは、シリアル2点間インタフェース向けに設計された軽量、低レイテンシ、省スペースのプロトコルです。Xilinx GTXシリアルトランシーバのフルレートをサポートするほか、レーンボンディングによってさらに広い帯域幅に対応します。本来高帯域データ移動のために設計されたもので、フロー制御、フレキシブルフレーミング、シンプレックス/フルデュプレックスチャンネルのオプションがあります。Xilinx Auroraの詳細については、下記のリンクを参照してください。

http://www.xilinx.com/products/design_resources/conn_central/grouping/aurora.htm

高速シリアル計測器ドライバ用計測器設計ライブラリは、Aurora 64b66b用のサンプルプロジェクト参照設計をインストールします。NIにはAurora 8b10b用のWebサンプルがあります。

JESD204BおよびJESD204C

無線広帯域変調デジタル伝送のニーズを満たすため、A/D変換器 (ADC) とD/A変換器 (DAC) のサンプルレートと分解能が高まるのに伴い、変換器との送受信のデータレートも向上しています。従来の並列クロック/データインタフェースでは、より統合性の高い回路ピンと緊密な許容性が求められます。JESD204BおよびJESD204Cは、そのようなインタフェースを高速シリアルに移行することで、この難題に対処しています。高速シリアル通信は、高いデータ帯域幅と低遅延時間で、複数の変換器の同期を容易にするものです。JESD204Bは、最大12.5 Gbpsと32レーンをサポートしますので、最新の高帯域、高速、多チャンネルADC/DACに対応します。JESD204Cは最大32 Gbpsのレートをサポートします。JESD204Bは8B/10B符号化を使用しますが、JESD204Cは8B/10B、64B/66B、64B/80Bをサポートします。

10ギガビットイーサネット

回線速度10.3125 Gbpsの10ギガビットイーサネット (10 GbE) は、実質的におよそ1 GB/秒の帯域幅を提供します。10ギガビットイーサネットインタフェースの大部分は、8P8C/RJ45ベースのインタフェースを備えた光またはSFP+ダイレクトアタッチ銅ケーブルです。PXIe-6592の10ギガビットイーサネットの例では、Xilinx 10ギガビットイーサネットPCS/PMA IPコアとOpenCores.org 10ギガビットイーサネットメディアアクセスコントローラの使用により、10GBASE-SR、-LR、-ER光インタフェースおよびSFP+ダイレクトアタッチもサポートします。LabVIEW FPGAに実装されている軽量のUDPスタックは、このMAC/PHYソリューションの上に配置されています。10ギガビットイーサネットIPコアの詳細については、下記のリンクを参照してください。

https://www.xilinx.com/products/intellectual-property/10gbase-r.html

PXI高速シリアル計測器ドライバ用計測器設計ライブラリは、1 GbEおよび10 GbE用のサンプルプロジェクト参照設計をインストールします。

100ギガビットイーサネット

100ギガビットイーサネット (100GbE) は、10ギガビットイーサネットよりも大幅に高速な100ギガビット/秒 (Gbit/s) の速度でイーサネットフレームを転送できます。100 GbEは、さまざまな光および電気インタフェース、およびさまざまな数の光ファイバ素線を提供します。主なインタフェースには、100GBASE-KR2、100GBASE-CR2、QSFP28などがあります。

LabVIEW FPGAには、100 GbE用のサンプルが付属しています。

CPRI

CPRIは、無線機器制御 (REC) と一般にリモートラジオヘッド (RRH) と呼ばれる無線機器 (RE) の間の光インタフェースを定義します。ラジオヘッドの構成と同期や、デジタルI/Q (ベースバンド) データの転送が容易になります。Xilinx CPRI IPコアの詳細については、下記のリンクを参照してください。

https://www.xilinx.com/products/intellectual-property/do-di-cpri.html

Serial RapidIO

Serial RapidIOは、高性能のシリアルインターコネクトプロトコルで、通信インフラ、航空宇宙/防衛組み込みコンピューティング、高帯域ライフサイエンス用機器、工業用制御など、エネルギー効率の高い組み込みシステム向けに最適化されています。最大6.25 Gbpsの速度、4つのレーンボンディング、低レイテンシ、フロー制御、順序どおりのパケット伝送、比較的小さいフットプリントといった特徴があります。Xilinx Serial RapidIO IPコアの詳細については、下記のリンクを参照してください。

http://www.xilinx.com/products/intellectual-property/ef-di-srio.html

PXIe-6592用のシリアルRapidIOの参照設計は、NIコミュニティから入手できます。2倍より大きいSRIOインタフェースには、PXIe-6591を推奨します。

その他のプロトコル

前述の例は、PXI高速シリアル計測器と互換性のあるすべてのプロトコルの完全なリストではありません。地域のNIセールスエンジニアが、特定のプロトコル、上記の例のカスタマイズ、またはカスタムまたは独自プロトコルの統合に関する質問にお答えします。

サンプルアプリケーション

PXI高速シリアル計測器の柔軟なアーキテクチャにより、それぞれ異なるデータ移動パターン、シリアルプロトコル、ソフトウェア機能を利用したさまざまな使用例をサポートできます。

プロトコル機能テスト

PXI高速シリアル計測器の一般的な使用例としては、特定のDUTに対するプロトコルに特化した機能テストの実行があります。そのようなテストは、DUTがシリアルプロトコルを介して「外の世界」と確実に通信していることを確認するのが目的です。DUTのレジスタの読み取り/書き込み、データスループットと遅延時間のベンチマーク、その他のプロトコルに特化した属性や内蔵テストモードなどの実行を行います。また応答のタイムアウト、エラーの注入、フロー制御コマンドの無視など、障害シナリオでDUTがどのように応答するかのテストを実施することもあります。関連タスクには、リンクビット誤り率計測、最大/最小ラインレートなどの物理層ストレステスト、バーンインテスト、さらには計測器が解析、カスタムトリガ、データキャプチャをFPGAで実行するバススヌーピングなどがあります。

DUTの制御/刺激/応答

PXI高速シリアル計測器のもう1つの一般的な使用例として、DUTの制御、刺激、応答のキャプチャがあります。このシナリオでは、計測器は必ずしも高速シリアルプロトコルを直接的にテストしているわけではありません。むしろ高速シリアルプロトコルを使用してDUTとの間でデータを送受信をしていますので、デバイスの他の部分もテストしている可能性があります。さらに、予備のデジタルI/Oを使用すると、SPIなど、並列または低速シリアルプロトコルを使用したDUTの制御ができます。

以下の例では、DACのアナログ出力特性をテストするために、PXIe-6591がJESD204Bプロトコルを使用してDACを刺激します。

図8. 最新の高性能DACおよびADCの多くは、JESD204B高速シリアルプロトコルを使用した通信が含まれています。

高帯域データ移動

多くの高性能組み込みアプリケーションでは、PXIプラットフォームを活用でき、他社製ハードウェアやNI PXIデバイスとの間で高帯域幅、低レイテンシのデータ移動が必要になります。これらのアプリケーションのために、PXI高速シリアル計測器はLabVIEW FPGAハードウェア処理、PXI Express計測器へのピアツーピアデータ転送、ディスクとの高帯域転送といった機能を備えています。同時に標準の高速シリアルプロトコルを介して、外部デバイスとの高帯域接続が可能です。

以下の例では、NIのオシロスコープがアナログ信号をサンプリングし、ピアツーピアデータストリーミング技術により、デジタル化された生データをPXIe-6592高速シリアル計測器に送信します。次に、計測器はLabVIEW FPGAに含まれているアルゴリズムを使用して、リアルタイムでデータを処理します。最後に、FPGA間のシリアル通信向けに設計された軽量Xilinx Auroraプロトコルを使用して、処理済みデータを他社製デバイスに送ります。

図9. PXI高速シリアル計測器は、他社製デバイスを使用した高帯域幅、低レイテンシのデータ移動に最適なソリューションです。

リンクデバッグ/パラメトリックテスト

高速シリアルインタフェースは極めて高い周波数信号を利用するため、信号品位が低いと通信の妨害につながる恐れがあります。そのような問題が生じた場合、デバッグツールがあればリンクの状態の確認に役立ちます。前述のEye Scan計測器設計ライブラリを使用すると、受信信号のリンクマージンを特定して、通信の問題が低信号品位によるものなのかを識別することができます。この機能は、本来アプリケーション開発時のデバッグを目的としたものですが、デバイスの検証や製造テストでもデバイス特定の性能パラメータの確認に使用することができます。しかし、PXI高速シリアル計測器の振幅およびタイミング確度は公称値であり、NIはこれらのパラメータについて保証された性能またはトレーサビリティを提供しません。一部のアプリケーションでは、現場での校正や調整も可能なオプションとなります。

その他のパラメトリックテストには、特定のプロトコルの代わりに業界標準パターン (PRBS-7、PRBS-15、PRBS-23、PRBS-31) を使用する既知の疑似乱数ビットシーケンス (PRBS) のビット誤り率があります。送信機と受信機のラインレートは、特定のDUTでサポートされるビットレートの範囲を決定するために変更できます。最後に、送信機の振幅およびプリ/ポストエンファシスを変化させて、自動ゲイン制御や動的等化など、受信機の感度をテストすることも可能です。

PXIe-6591およびPXIe-6592については、下記のリンクにあるNIコミュニティで追加の資料を参照できます。PXI高速シリアル計測器で使用するその他の物理層解析ツールについては、NIコミュニティのNI MGTデバッグツールを参照してください。PXIe-6593およびPXIe-6594については、「PXIe-6593およびPXIe-6594高速シリアルデバイスでアイスキャンを使用する」を参照してください。

必須スキル

LabVIEWとLabVIEW FPGAによって高速シリアル技術の実装が劇的に簡素化されていますが、PXI高速シリアル計測器のプログラミングを成功させるには特定の専門技術が不可欠です。LabVIEWで開発されているため、LabVIEWグラフィカルプログラミングに精通していることが重要です。ご不明点につきましては、ni.comにあるNI LabVIEWアプリケーション開発トレーニングコースのページをご覧ください。さらに、非プロトコルFPGAロジックをLabVIEW FPGAでカスタマイズするには、高スループットのLabVIEW FPGAプログラミングについて深く理解する必要があります。詳細については、NI LabVIEW高性能FPGA開発者ガイドを参照してください。 既存のIPまたはサンプルを使用するプロトコルでは、プロトコルIPとLabVIEW FPGAダイアグラムの接続を定義するにはVHDLの知識と経験が必要です。また新しいプロトコルやカスタムプロトコルを実装するには、高度なデジタル設計の専門技術が役立ちます。特定のNIパートナーは、社内にこれらの機能を持たない人向けにこれらの機能を提供しています。お客様に合ったアライアンスパートナーを見つけるには、お近くのNI事業所までお問い合わせください。

表4. 高速シリアル計測器のプログラミングには、インタフェースで必要な変更のレベルに応じて、異なるレベルのスキルとツールが必要です。

次のステップ

- NI PXI高速シリアルモジュールを使用して、データ移動と信号処理を最大化する方法を学ぶ。

- 高速シリアル通信リンクの基本概念について学ぶ。

- 高速シリアルプロトコルを無線トランシーバの機能テストシステムに実装するための参照設計の例を参照してください。

- ハードウェアドライバに含まれていないその他のプロトコル参照設計は、ソフトウェア設計型計測器向けサンプルおよびIPとNI FlexRIOコミュニティから入手してください。

- PXI高速シリアル計測器を購入する。

- カスタムPXIシステムを構築する。

|  |  |  |  |  | |

| 仕様 | PXIe-6591 | PXIe-6592 | PXIe-6593 | PXIe-6594 | PXIe-7902 | PXIe-79032 |

| ラインレート | 500 Mbps–12.5 Gbps¹ | 500 Mbps–10.3125 Gbps¹ | 500 Mbps–16.3 Gbps | 500 Mbps–28.2 Gbps | 500 Mbps–12.5 Gbps | 500 Mbps–28.2 Gbps |

| チャンネル数 | 8 TX/RX | 4 TX/RX | 8 TX/RX | 8 TX/RX | 24 TX/RX | 48 TX/RX |

| FPGA | Kintex 7 K410T | Kintex 7 K410T | Kintex UltraScale KU040、KU060 | Kintex UltraScale+ KU15P | Virtex™ 7 485T | Virtex UltraScale+ XCVU11P |

| DRAM | 2 GB | 2 GB | 4 GB | 8 GB | 2 GB | 20 GB |

| ホストストリーミング帯域幅 | 3.2 GB/秒 | 3.2 GB/秒 | 7 GB/秒 | 7 GB/秒 | 3.2 GB/秒 | 7 GB/秒 |

| コネクタ | Mini-SAS HD | SFP+ | QSFP28 | QSFP28 | Mini-SAS HD | Mini-SAS HD |

| ケーブルのオプション | 銅線または光 | 銅線または光 | 銅線または光 | 銅線または光 | 銅線または光 | 銅線または光 |

| Aux DIO | 20 SE | 4 SE | 8 GPIO | 8 GPIO | 該当なし | 8 GPIO |

| 仕様 | FPGA | LUT | DSPスライス | 組み込みブロックRAM |

| PXIe-6591 | Kintex-7 K410T | 254,200 | 1,540 | 28 Mb |

| PXIe-6592 | Kintex-7 K410T | 254,200 | 1,540 | 28 Mb |

| PXIe-6593 | Kintex UltraScale KU040 | 242,400 | 1,920 | 21.1 Mb |

| Kintex UltraScale KU060 | 331,680 | 2,760 | 38 Mb | |

| PXIe-6594 | Kintex UltraScale+ KU15P | 523,000 | 1,968 | 34.6 Mb |

| PXIe-7902 | Virtex-7 485T | 303,600 | 2,800 | 37 Mb |

| PXIe-7903 | Virtex UltraScale+ XCVU11P | 2,835,000 | 9,216 | 341 Mb |

| モデルを使用 | LabVIEW | 高スループットLabVIEW FPGA | VHDL | 広範なデジタル設計の専門技術 |

| 既存のパーソナリティを使用 | — | — | — | |

| FPGAコードをカスタマイズするが、プロトコルはカスタマイズしない | — | — | ||

| 既存のプロトコルを統合 | — | |||

| 新規またはカスタムプロトコルを実装 |