デジタル状態、電圧レベル、ロジックファミリ

概要

デジタル信号のデジタル状態、電圧論理レベル、論理レベルファミリについて学びましょう。このチュートリアルは、計測器の基本シリーズの一部です。

内容

デジタル状態

デジタルデバイスには、オンとオフの2つの状態しかありません。これらの2つの状態のみを使用して、デバイスは大量のデータを通信し、他のさまざまなデバイスを制御できます。バイナリでは、これらの状態は1または0で表されます。通常、バイナリ1は論理HIGH、0は論理LOWとみなされます。

電圧レベル

しかし、デジタルデバイスは多くの場合、無限の状態を持つアナログデバイスによって駆動されます。無限の数の状態を2つの状態のみにするにはどうすればよいでしょうか。その答えは、論理HIGHまたは論理LOWを表す電圧を定義する電圧論理レベルを作成することです。

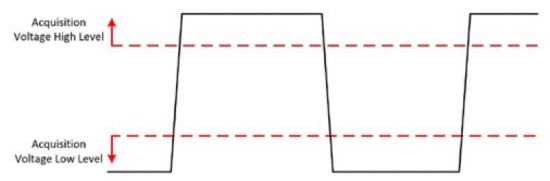

図1: 電圧レベルは、論理HIGHまたはLOWを表すアナログ電圧を定義します。

システムは選択した任意の値で電圧論理レベルを定義できますが、多くの回路は論理HIGHをグランドに対して+5 Vまたは+3.3 Vで表し、論理LOWをグランドまたは0 Vで表します。このタイプのシステムは、正またはアクティブHIGHと呼ばれます。ピンがアクティブ化される仕組みを説明します。アクティブHIGHピンの場合、ピンを高電圧に接続します。

負またはアクティブLOWシステムはその逆です。より高い電圧は論理LOWを表し、より低い電圧は論理HIGHを表します。アクティブLOWピンの場合、ピンをグランドに接続してLOWにする必要があります。データシートでは、ピンがアクティブLOWであることを示すために、ENのようなピン名の上にラインを追加することがしばしばあります。

HIGHとLOWは指定されていますが、ほとんどのシステムでは実際にはより実用的な範囲が設定されています。たとえば、論理HIGHは2 V~5 Vの間の任意の値であり、論理LOWは0 V~1 Vの任意の値です。これらの範囲外の電圧は無効とみなされ、障害状態または論理レベル遷移中にのみ発生します。

ZおよびX状態

デジタル信号には、オンとオフの2つの状態しかありませんが、追加の状態を使用して、デジタル信号の集録および生成を支援できます。トライステート論理では、3つ目の状態 (出力がラインから切断された高インピーダンス状態) が可能です。この状態はHIGHまたはLOWではなく、浮動または高インピーダンス状態です。これにはZが指定され、通常はイネーブルラインとして使用されます。

Z状態の最も一般的な用途は、複数のトランスミッタで駆動可能な1つ以上のデジタルラインをテストすることです。メモリチップのデータポートがその良い例です。コンピュータがメモリデバイスに書き込みを行う場合、コンピュータはメモリチップに書き込むためのデータを、メモリデバイスのデータピン (0 または 1) 上で駆動する必要があります。その後、コンピュータのプロセッサがメモリから情報を読み取る必要がある場合、メモリデバイスは以前に保存されたデータ値をコンピュータプロセッサに戻す必要があります (通常、データピンのZ状態)。

4番目の状態は、Xで指定されたホールド状態です。デジタル信号を生成する際、どの状態であっても、デバイスがチャンネルを現在の状態に維持させると便利な場合があります。この状態は、初期状態またはアイドル状態を設定するときに役立ちます。

データを収集する際、X状態は別の「Don't Care」が指定されます。この状態は、収集したデジタル信号を予測される信号と比較するときに役立ちます。たとえば、10個の値の信号の中で、最初の4つの値のみを考慮する場合があります。最後の6つの値に対してX状態を使用し、最初の4つの値だけを比較することができます。

| 状態 | 指定 |

|---|---|

| 0 | 論理LOW |

| 1 | 論理HIGH |

| Z | 高インピーダンス |

| X | ホールド状態またはDon't Care |

表1: デジタル信号はHIGHまたはLOWの状態のみが可能です。ただし、Z状態とX状態は、デジタル信号を生成または収集するアプリケーションで役立ちます。

ロジックファミリ

標準化されたロジックファミリを使用して、回路やコンポーネントを簡単に操作できます。これらは論理HIGHまたは論理LOWを構成する標準化された電圧レベルを提供します。ロジックファミリ内のすべての回路は、同じ特性を共有しているため、同じファミリ内のその他の回路と互換性があります。

シングルエンドロジックファミリ

シングルエンドロジックファミリは、グランドを基準とする電圧レベルを指定します。4つのレベルは以下のように定義されます。

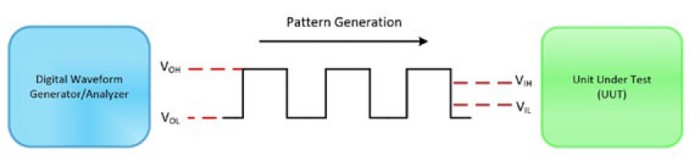

- VOH (出力HIGHレベル電圧) - これは生成電圧HIGHレベルとも呼ばれます。アクティブ駆動生成用に構成されている場合、これはデバイスが論理HIGHを生成する際に生成される電圧です。オープンコレクタ生成用に構成されている場合、これはデータチャンネルを高インピーダンス状態に設定することと同じです。

- VOL (出力LOWレベル電圧) – これは、生成電圧LOWレベルとも呼ばれます。これは、デバイスが論理LOWを生成する際に生成される電圧です。

- VIH (入力HIGHレベル電圧) – これは、集録電圧HIGHレベルとも呼ばれます。これは、デバイスが論理HIGHを読み取り、デバイスに送信するために必要な電圧レベルです。

- VIL (入力LOWレベル電圧) – これは、集録電圧LOWレベルとも呼ばれます。これは、デバイスが論理LOWを読み取り、デバイスに送信するために必要な電圧レベルです。

図2: 出力と入力にシングルエンド論理レベルが指定されている。

デバイスと正確に通信するには、以下の条件が満たされるようにデジタルデバイスを構成してください。

- VOH ≥ DUT VIH

- VOL ≤ DUT VIL

- VIH ≤ DUT VOH

- VIL ≥ DUT VOL

- VIH > VIL

通常、あるデバイスの出力電圧と別のデバイスの入力電圧の間にはクッションがあります。これは、ノイズマージンまたは耐ノイズ性レベル (NIM) と呼ばれます。ノイズの多い環境にあり、不正確なデータビットの問題が生じている場合には、この値を増やすことを検討してください。

いくつかのシングルエンドロジックファミリがあります。TTLは、集積回路で非常に一般的で、コンピュータ、家電製品、テスト装置などの多くのアプリケーションで使用されています。バイポーラトランジスタで構築された回路は、論理状態の切り替えと維持を行います。TTLはまた、特定の電流仕様と立ち上がり/立ち下がり時間を満たす必要があります。詳細については、TTL対応信号の定義をお読みください。

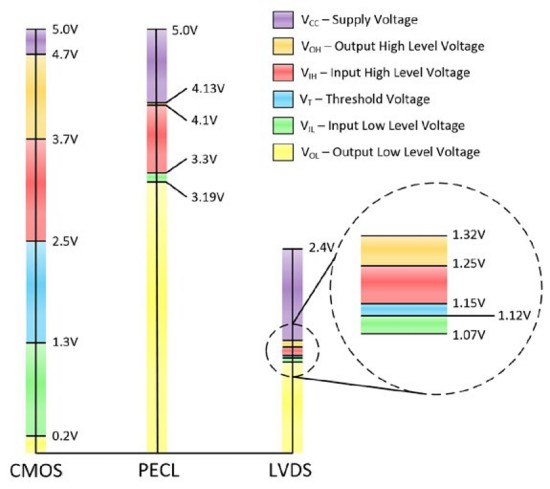

図3: 標準5 V TTL電圧レベル

もう1つの一般的なICファミリはCMOSです。これらのデバイスは、耐ノイズ性が高く、消費電力が少なく、ベース電圧が低くなります。互換性を高めるため、ほとんどの電圧レベルはTTLデバイスと同様です。これにより、TTLデバイスからCMOSデバイスへの切り替えは簡単になりますが、逆方向への切り替えは難しくなることがあります。CMOSへの電圧が高すぎると、チップが破損する可能性があります。この場合、分圧器を使用して電圧を下げることができます。

図4: 標準CMOS電圧レベル

差動ロジックファミリ

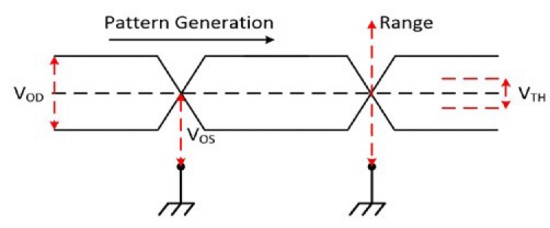

シングルエンドロジックファミリは、グランドを基準として設定された電圧レベルを使用します。ただし、差動ロジックファミリは、グランド基準ではなく、2つの値の差を使用します。差動信号が論理LOWとして解釈されるためには、信号が相補信号よりもしきい値 (VTH) と呼ばれる特定の値以上小さい必要があります。信号は基準化され、一緒に送信されるため、シングルエンドロジックファミリを使用するよりも高い耐ノイズ性を達成できます。差動ロジックファミリの電圧レベルは通常、絶対電圧ではなく差動電圧で指定されます。4つのレベルは以下のように定義されます。

- VOD (出力差動電圧) – これは信号間の電圧差です。

- VOS (オフセット電圧) – これは差動信号のコモンモードです。これは2つの信号の平均と考えてください。これはグランドを基準とします。

- VTH (しきい値電圧) - これは、デバイスが有効な論理状態を登録するために必要な電圧の差です。

- VRANGE (入力電圧レンジ) – これは、デバイスが許容するグランドを基準とする絶対電圧です。

まとめ

- 電圧論理レベルは、論理HIGHまたは論理LOWを表す電圧を定義します。

- 多くの回路はグランドに対する+5 Vまたは+3.3 Vを論理HIGH、グランドまたは0 Vを論理LOWで表しています。このタイプのシステムは、正またはアクティブHIGHと呼ばれます。

- トライステート論理では、Z状態は高インピーダンス状態で、通常はイネーブルラインとして使用されます。

- デジタル生成では、X状態は現在の論理レベルを維持します。デジタル集録では、Don't Care状態を示します。

- ロジックファミリは、論理HIGHまたは論理LOWを構成する標準化された電圧レベルを提供します。

- TTLはVCC= 5 Vに基づいています。

- CMOSは、VCC= 3.3 Vに基づいています。

- 差動ロジックファミリは、グランド基準ではなく、2つの値の差を使用します。

- LVDSは、VCC= 3.3 Vの低ノイズ、低電力、低振幅の差動方式です。

- LVPECL回路は、各チャンネルに一対の信号ライン (VCC= 3または3.3 V) を必要とするECL回路の一種です。