Le contrôleur pour FlexRIO : Une analyse approfondie de l’instrumentation déployable

Aperçu

Le contrôleur pour FlexRIO est une solution commerciale prête à l’emploi (COTS) conçue pour les applications qui nécessitent des E/S hautes performances et un traitement de signaux en temps réel dans un format compact et autonome. La combinaison d’E/S modulaires, d’un FPGA programmable par LabVIEW et d’un processeur embarqué permet aux ingénieurs de reconfigurer complètement le matériel pour des applications spécifiques, ce qui distingue le contrôleur pour FlexRIO de la plupart des instruments COTS. Le contrôleur partage également les mêmes modules d’adaptation, FPGA et expérience logicielle que FlexRIO sur PXI, ce qui en fait une cible de déploiement idéale des solutions développées sur la plate-forme PXI. Bien qu’il ait beaucoup en commun avec FlexRIO dans PXI, il s’adresse aux applications embarquées où les solutions plus petites, plus légères et de faible puissance sont préférables.

Contenu

- Architecture interne

- Interface du module d’adaptation FlexRIO

- FPGA

- Série haute vitesse

- Cadencement

- Processeur

- Connectivité

- Emballage physique

- Résumé

- Étapes suivantes

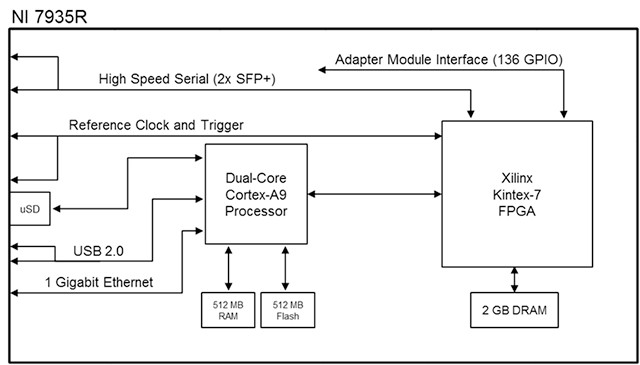

Figure 1 : Le contrôleur pour FlexRIO est un périphérique d’acquisition et de traitement de signaux autonome doté d’E/S hautes performances et d’un grand FPGA Kintex-7.

Architecture interne

Le contrôleur pour FlexRIO est construit autour d’un grand FPGA Kintex-7 qui est connecté à une interface d’E/S modulaire, un processeur et 2 Go de DRAM DDR3. Avec plus de 400 000 slices logiques, 1 540 slices de traitement de signaux numériques (DSP) et 28 Mo de RAM, une quantité considérable de traitement de signaux peut être implémentée sur le FPGA. Le processeur ARM double cœur fournit une connectivité réseau et USB pour l’interface avec d’autres périphériques, ainsi qu’un stockage embarqué pour l’enregistrement des paramètres et des données.

La combinaison d’un grand FPGA et d’un processeur à faible puissance est particulièrement précieuse lorsque la plupart des algorithmes peuvent être implémentés sur le FPGA, ce qui laisse le processeur ARM double cœur pour la configuration et la surveillance du système. Cette architecture rapproche l’intelligence du front, où un FPGA hautes performances peut être utilisé pour transformer des données haute vitesse en informations significatives.

Figure 2 : Avec un grand FPGA Kintex-7, le contrôleur pour FlexRIO est idéal pour les applications où les algorithmes de traitement de signaux doivent s’exécuter en temps réel.

Si des données à large bande passante doivent être regroupées dans un emplacement central, les modèles NI 7932R et NI 7935R disposent également de deux ports série haute vitesse pour le streaming de données directement à partir du FPGA en utilisant 10 Gigabit Ethernet UDP, Xilinx Aurora ou des protocoles personnalisés.

Interface du module d’adaptation FlexRIO

Figure 3 : NI 5772 est un module d’adaptation de numériseur haute vitesse à 2 voies couramment utilisé dans les mesures temporelles et fréquentielles.

En savoir plus sur le kit de développement de modules FlexRIO

FPGA

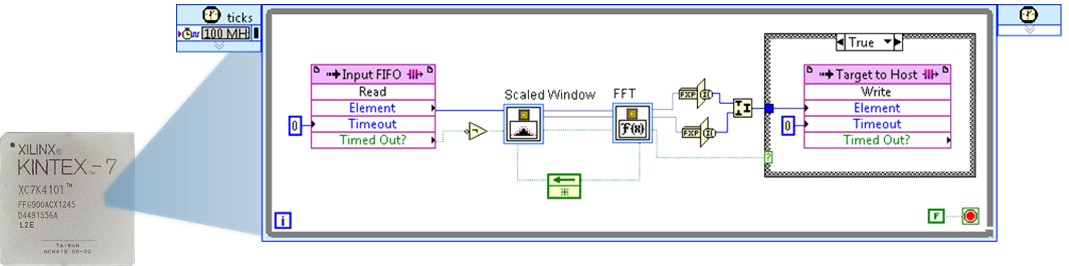

Les utilisateurs programment le FPGA à l’aide du logiciel de conception de système LabVIEW avec le module LabVIEW FPGA, ce qui permet à la fois la capture d’algorithmes basés sur LabVIEW et l’intégration VHDL/Verilog. Les bibliothèques LabVIEW existantes peuvent être utilisées pour accélérer le développement avec une infrastructure de mouvement de données, des fonctions de traitement de signal avancées telles qu’une transformée de Fourier rapide (FFT) à bande ultralarge et des algorithmes de rééchantillonnage en parallèle, et un streaming DMA géré vers l’hôte. Les conceptions peuvent être simulées dans LabVIEW avant de les compiler localement ou via le NI Compile Cloud Service. Une fois le fichier bitfile FPGA compilé à l’aide de LabVIEW FPGA et de Xilinx Vivado, les fichiers bitfile sont déployés via LabVIEW sur la machine de développement, par des applications temps réel, construites avec LabVIEW ou C/C++, qui s’exécutent sur le contrôleur, ou à partir du flash du périphérique au démarrage. Dans de nombreuses conceptions FlexRIO, la logique est cadencée à des centaines de mégahertz, ce qui rend le respect des contraintes de cadencement plus difficile. NI recommande aux nouveaux développeurs de LabVIEW FPGA de commencer par consulter le High-performance LabVIEW FPGA Developers Guide pour connaître les meilleures pratiques en matière de cadencement et d’optimisation des ressources.

Figure 4 : LabVIEW simplifie la programmation FPGA en fournissant un environnement de développement graphique intégré pour la conception, la simulation, la mise au point et le déploiement.

Les ingénieurs peuvent choisir entre deux options de FPGA : un Xilinx Kintex-7 K325T et un K410T plus grand. Pour le développement initial, l’utilisation du plus grand FPGA disponible présente des avantages importants. Non seulement il offre la flexibilité d’ajouter des fonctionnalités pendant le développement, mais il offre aussi la possibilité de compiler le même code sur un FPGA plus grand, ce qui réduit généralement les temps de compilation pendant la conception et permet une itération plus rapide. Avec les interfaces d’E/S fournies par NI, le code LabVIEW FPGA écrit pour une cible matérielle peut être rapidement porté vers d’autres matériels NI, même du matériel avec des FPGA et des capacités d’E/S différentes.

FPGA | Tranches | LUT | Bascules bistables | Tranches DSP | Bloc RAM (ko) | DRAM embarqué |

Kintex-7 K410T | 63 550 | 254 200 | 445 200 | 1 540 | 28 620 | 2 GO |

Kintex-7 K325T | 50 950 | 203 800 | 407 600 | 840 | 16 020 | 2 GO |

Figure 5 : Le contrôleur pour FlexRIO comprend deux FPGA Xilinx différents permettant aux utilisateurs de choisir la bonne pièce pour l’application. NI recommande d’utiliser le plus grand FPGA pour le développement initial avant de tenter d’optimiser la conception du déploiement.

La DRAM est une ressource qui apporte une valeur ajoutée substantielle aux algorithmes de traitement de signaux à plusieurs étages et à la bufférisation des données sur les bus non déterministes. Afin de rendre ces types d’opérations possibles, les trois variantes du contrôleur pour FlexRIO ont un banc de 2 Go de DRAM DDR3 connecté au FPGA. L’interface DRAM a une largeur de données de 512 bits et est accessible efficacement à des fréquences d’horloge allant jusqu’à 166 MHz, ce qui donne une bande passante théorique maximale de 10,6 Go/s entre la DRAM et le FPGA. Les lectures et écritures d’accès aléatoire diminuent le débit DRAM, cependant, NI a des lectures et écritures séquentielles de référence supérieures à 9 Go/s. La DRAM peut être adressée à l’aide de l’élément LabVIEW Memory dans LabVIEW FPGA ou en tant que FIFO à l’aide de la Memory Instrument Design Library (IDL).

Apprenez à utiliser efficacement la DRAM.

Série haute vitesse

Pour les applications qui nécessitent un flux de données à large bande passante après l’acquisition et le traitement des signaux, NI 7932R et NI 7935R sont équipés de deux émetteurs-récepteurs série haute vitesse, capables chacun de diffuser des données jusqu’à 10,3125 Go/s. Cette technologie repose sur des émetteurs-récepteurs multi-gigabit (MGT) Xilinx GTX qui sont acheminés du FPGA vers deux connecteurs SFP+ sur la face-avant. NI fournit des exemples de projets LabVIEW FPGA pour les protocoles UDP Ethernet 10 Gigabit et Xilinx Aurora. Les utilisateurs expérimentés avec VHDL peuvent en implémenter d’autres, comme Serial RapidIO ou des protocoles personnalisés.

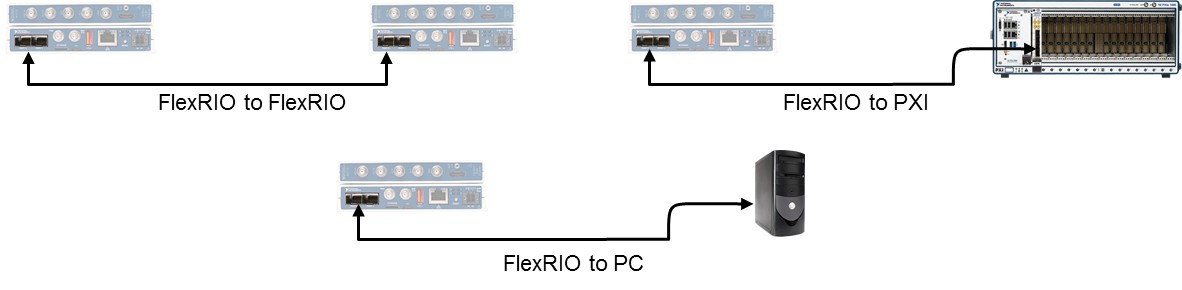

Les exemples de configurations de flux de données qui utilisent ces ports série haute vitesse incluent le partage de données entre plusieurs contrôleurs à l’aide de Xilinx Aurora, pour le streaming de données vers PXI en utilisant Aurora ou 10 Gigabit Ethernet, et le streaming de données vers un PC de bureau, un enregistreur de données, un système de stockage d’espace réseau (NAS) ou un serveur en utilisant 10 Gigabit Ethernet.

Figure 6 : Les ports série haute vitesse sont conçus pour le streaming de données à haute bande passante vers un certain nombre de périphériques. Les protocoles de communication sont définis dans LabVIEW FPGA et chaque émetteur-récepteur peut s’exécuter jusqu’à 10,3125 Go/s.

En savoir plus sur la technologie série haute vitesse dans les produits NI

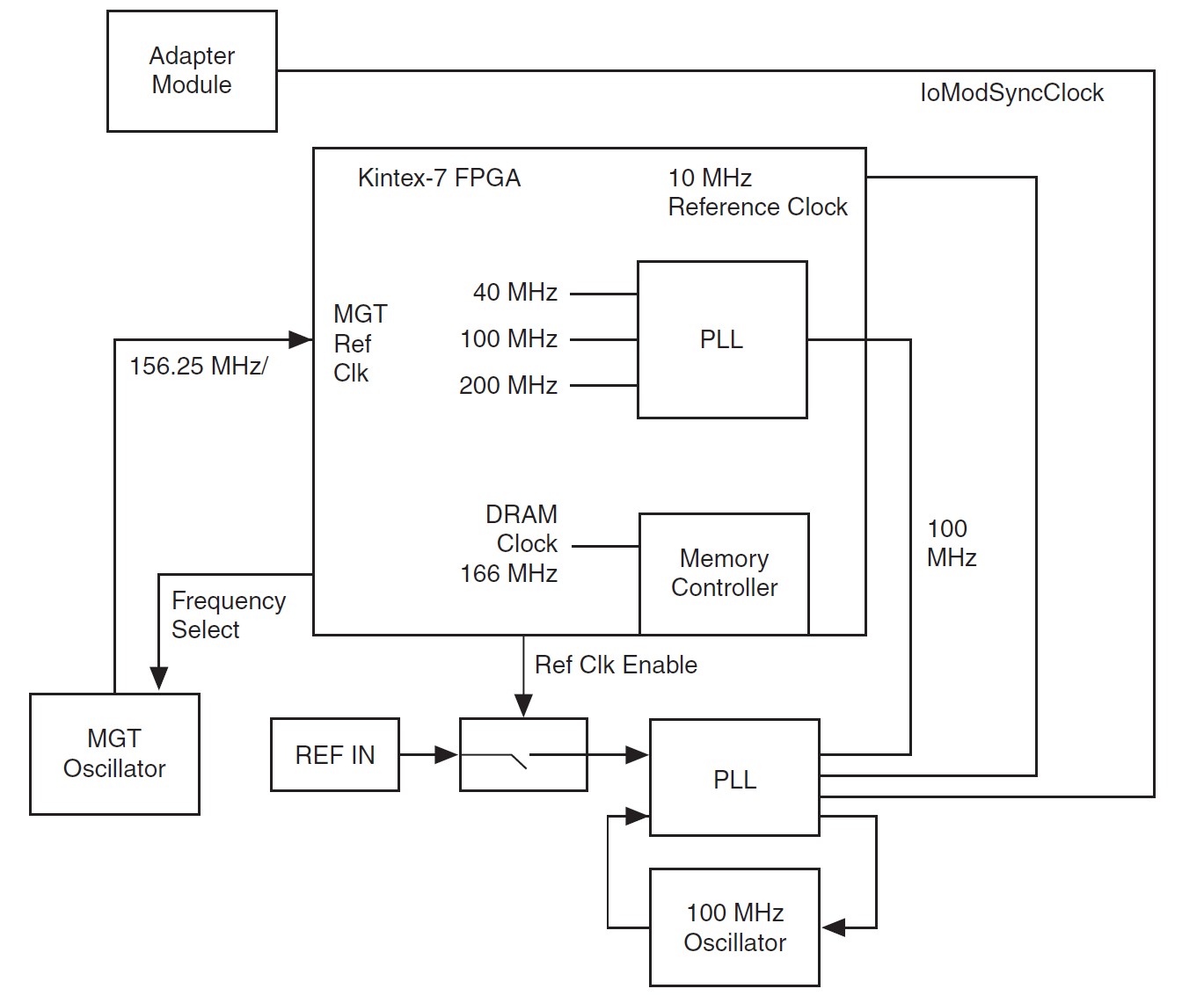

Cadencement

Les ingénieurs travaillant avec des FPGA et des E/S haute vitesse passent souvent beaucoup de temps à implémenter une architecture d’horloge et de synchronisation appropriée. Pour simplifier ce processus, le contrôleur pour FlexRIO dispose d’un certain nombre d’options d’horloge, y compris une entrée d’horloge de référence externe à 10 MHz, une ligne de déclenchement bidirectionnelle, un oscillateur 100 MHz embarqué et la capacité de verrouillage en phase à une référence externe. Pour assurer un transfert de données synchrone entre le module d’E/S et le FPGA, l’horloge d’échantillonnage du module d’E/S est partagée avec le circuit d’horloge du contrôleur pour FlexRIO. Des horloges supplémentaires peuvent aussi être dérivées sur le FPGA.

Figure 7 : Avec le circuit d’horloge du contrôleur pour FlexRIO, les utilisateurs peuvent synchroniser plusieurs périphériques avec une précision de sous-échantillonnage.

Pour les systèmes distribués et l’horodatage, un récepteur GPS peut être connecté afin de fournir une horloge de 10 MHz à l’entrée d’horloge de référence et une entrée d’impulsion par seconde au déclenchement SMA. Pour des exigences de synchronisation moins strictes, l’hôte NI Linux Real-Time supporte aussi l’IEEE 1588 basé sur logiciel. Pour les systèmes où la synchronisation électrique est possible, une source de 10 MHz comme l’Octohorloge Ettus peut être utilisée pour fournir une horloge de référence partagée. Dans le cas où plusieurs unités sont co-localisées, il convient d’envisager les fonctionnalités d’horloge et de synchronisation avancées de la plate-forme PXI.

Processeur

Le processeur ARM Cortex-A9 double cœur ajoute la flexibilité et la connectivité nécessaires au déploiement du contrôleur pour FlexRIO sur le terrain. Il peut être utilisé pour fournir des données à un réseau, ajuster des paramètres de configuration, enregistrer des données et des messages, ou même mettre à jour les logiciels et le firmware FPGA qui s’exécutent sur le périphérique. Le processeur exécute le système d’exploitation NI Linux Real-Time, qui offre un plus grand déterminisme et une plus grande fiabilité, ainsi que les avantages standard du noyau Linux. Le système d’exploitation temps réel (RTOS) est programmable via LabVIEW avec le module LabVIEW Real-Time et prend également en charge le développement en C/C++ en utilisant votre environnement de développement intégré (IDE) préféré. La programmation et la construction d’applications à partir de LabVIEW permettent aux développeurs d’accéder à des bibliothèques pré-construites pour la communication réseau et les E/S sur fichiers, ce qui simplifie considérablement le développement.

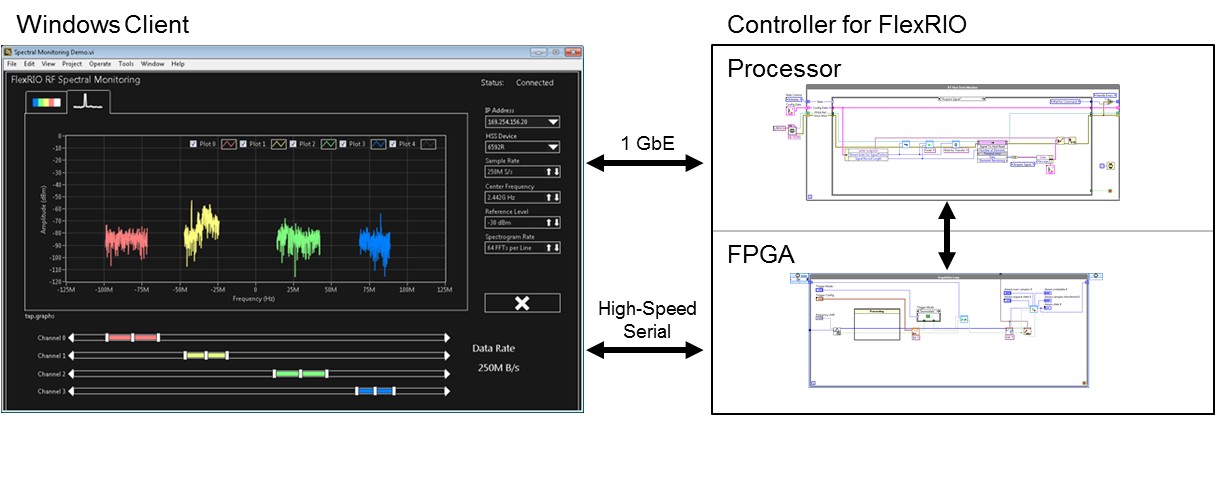

En ce qui concerne les utilisateurs familiers avec FlexRIO, la principale différence lors du passage de FlexRIO sur PXI au contrôleur pour FlexRIO est qu’une couche de communication réseau est ajoutée entre le FPGA et le client Windows traditionnel. Au lieu de cibler le FPGA directement à partir de Windows, le code développé pour NI Linux Real-Time cible le FPGA et l’utilisateur est responsable de la programmation de toute communication réseau de surveillance ou de configuration du système. Sur les périphériques NI 7932R et NI 7935R, les utilisateurs peuvent tirer parti des deux ports série haute vitesse pour le streaming de données directement à partir du FPGA via UDP Ethernet 10 Gigabit ou Xilinx Aurora.

Figure 8 : Un système déployé comporte souvent trois couches d’application : un firmware qui s’exécute sur le FPGA, un code LabVIEW ou C/C++ qui s’exécute sur l’hôte Linux Real-Time, et une application client pour la configuration à distance, la surveillance ou l’enregistrement des données.

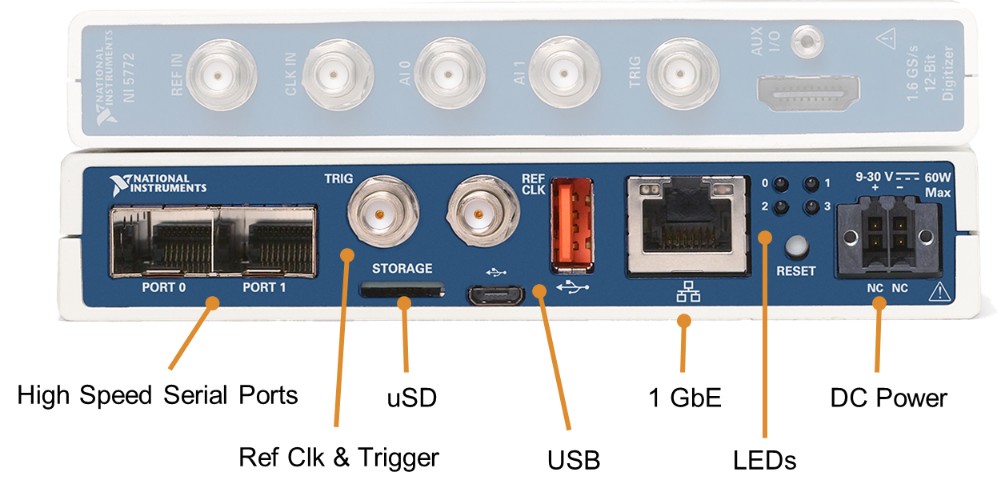

Le processeur a également accès à 512 Mo de stockage flash et 512 Mo de RAM, ainsi qu’à une interface Ethernet 1 Gigabit, aux interfaces périphérique et hôte USB 2.0 et à un emplacement pour carte μSD. L’interface principale des applications déployées devrait être 1 Gigabit Ethernet, car elle supporte une bande passante considérablement plus large ; cependant, le port de périphérique USB peut être utilisé pour l’installation, la configuration et le diagnostic.

Connectivité

Toute la connectivité est exposée sur une seule face matérielle pour faciliter l’intégration du périphérique dans de plus grands systèmes. Bien que les E/S soient modulaires, les modules d’adaptation analogiques fournissent également au FPGA des E/S numériques via un connecteur d’E/S auxiliaire. Le contrôleur accepte une alimentation CC entre 9 et 30 volts, ce qui signifie qu’il peut être alimenté par pile pour les systèmes portables.

Figure 9 : Outre la connectivité fournie par les modules d’adaptation FlexRIO, le contrôleur pour FlexRIO dispose d’interfaces standard dédiées aux flux de données, de connecteurs SMA pour l’horloge et la synchronisation, de ports USB pour communiquer avec les périphériques et de LED pour l’indicateur d’état visuel.

Tous les connecteurs ont des mesures pour le maintien du câble, à l’exception des deux ports USB. Le port hôte USB (de couleur orange) est spécialement conçu pour une rétention élevée, alors que le port de périphérique USB est destiné à être utilisé principalement à des fins de diagnostic.

Emballage physique

Le boîtier en aluminium du périphérique élimine la nécessité de concevoir des mécaniques personnalisées et est conçu pour faciliter son intégration en fournissant des performances analogiques et thermiques cohérentes dans une variété de scénarios. Avec le kit de montage, l’unité peut aussi être montée en toute sécurité sur le panneau.

Figure 10 : Le contrôleur pour FlexRIO est empaqueté pour les applications embarquées dont la taille, le poids et la puissance sont limités.

L’emballage inclut également plusieurs fonctionnalités pour garantir la fiabilité et la maintenance à long terme. Tout d’abord, les développeurs ont accès à des crochets logiciels pour surveiller les températures du FPGA et du processeur. Si la température du FPGA ou du processeur dépasse les limites de sécurité, le périphérique s’arrête automatiquement pour éviter d’endommager les composants internes. Le refroidissement actif est assuré par un ventilateur utilisable qui peut être surveillé dans un logiciel et ajusté automatiquement en fonction de la température du périphérique. À 40 °C, le délai moyen entre les défaillances (MTBF) du ventilateur est de plus de sept ans.

Pour les scénarios où les chocs, les vibrations, la température ou l’humidité sont préoccupants, le contrôleur pour FlexRIO est coté de manière similaire au PXI ; il supporte un choc semi-sinusoïdal de pic de 30 g, une vibration de 0,3 geff entre 5 Hz et 500 Hz, des températures ambiantes de 0 °C à 55 °C et une humidité non condensante de 5 à 95 %.

Résumé

La capacité de prototyper rapidement des algorithmes qui s’exécutent en temps réel est un avantage que NI offre depuis plus d’une décennie avec l’architecture d’E/S reconfigurables (RIO) LabVIEW et LabVIEW FPGA. Pour les ingénieurs et les scientifiques qui prototypent de nouvelles technologies dans des domaines tels que les radars, la surveillance du spectre, les communications, les machines industrielles, les ultrasons et l’imagerie médicale, cette plate-forme permet un prototypage plus rapide avec un maximum de réutilisation du code pendant la production ou le déploiement.

Étapes suivantes

- En savoir plus sur FlexRIO

- Acheter des modules d’adaptation FlexRIO

- Afficher le Contrôleur pour les variantes de FlexRIO

La marque déposée Linux® est utilisée selon les termes d’une sous-licence de LMI, le détenteur exclusif de la licence de Linus Torvalds, propriétaire de la marque au niveau mondial.