From Friday, April 19th (11:00 PM CDT) through Saturday, April 20th (2:00 PM CDT), 2024, ni.com will undergo system upgrades that may result in temporary service interruption.

We appreciate your patience as we improve our online experience.

From Friday, April 19th (11:00 PM CDT) through Saturday, April 20th (2:00 PM CDT), 2024, ni.com will undergo system upgrades that may result in temporary service interruption.

We appreciate your patience as we improve our online experience.

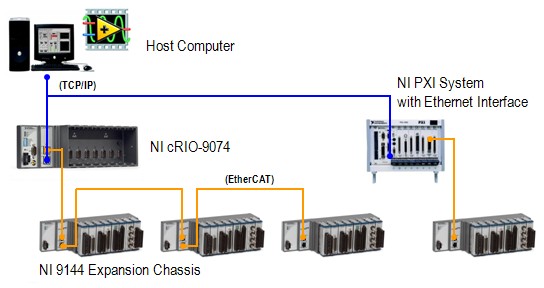

NI EtherCAT 재구성 가능 I/O(RIO) 확장 섀시는 타이밍 결정성 네트워크를 통해 동기화된 분산 I/O를 제공합니다. NI LabVIEW Real-Time Module로 프로그래밍된 섀시는 NI CompactRIO, PXI, NI 산업용 컨트롤러 플랫폼에 이더넷 포트가 2개인 NI 리얼타임 PAC(프로그래밍 가능 자동화 컨트롤러)에서 데이지 체인으로 연결될 수 있습니다. 또한, 각 EtherCAT RIO 섀시에는 사용자 정의 타이밍과 인라인 처리가 가능한 지능형 분산 디바이스용으로 LabVIEW FPGA Module로 프로그래밍할 수 있는 FPGA(Field-Programmable Gate Array)가 있습니다. 이 백서에서는 LabVIEW Real-Time에서 NI 스캔 엔진을 사용하는 NI 9144 시스템 루프 속도 벤치마크의 기술과 성능 결과를 자세히 살펴봅니다.

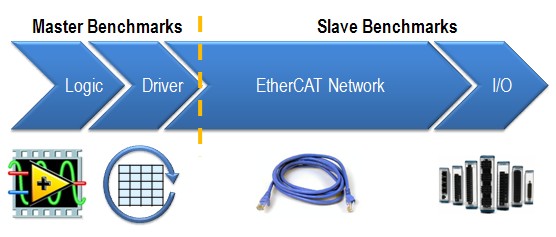

마스터 컨트롤러와 NI 9144 사이의 통신 네트워크는 EtherCAT이라는 개방형 리얼타임 이더넷 프로토콜을 기반으로 합니다. 상위 레벨에서 EtherCAT 벤치마크는 로직, 드라이버, EtherCAT 네트워크, I/O의 4가지 구성요소로 이루어져 있습니다.

그림 2. 마스터 및 슬레이브 벤치마크의 구성요소

EtherCAT 마스터 디바이스의 경우, 마스터 벤치마크는 사용자의 코드 및 코드와 EtherCAT 네트워크 간에 데이터를 이동하는 EtherCAT 드라이버에 따라 달라집니다. 일반적으로 EtherCAT 마스터 컨트롤러는 시스템 루프 속도를 제한하는 요소입니다. 그 이유는 처리 능력이 사용자 로직과 드라이버에서 데이터가 처리되는 속도에 영향을 크게 미치기 때문입니다. 컨트롤러의 능력이 강할수록 더 짧은 시간에 더 많은 I/O 데이터를 처리할 수 있습니다.

반면 슬레이브 디바이스 벤치마크는 패킷이 EtherCAT 네트워크에서 이동하는 시간과 슬레이브 I/O가 업데이트할 수 있는 속도에 따라 달라집니다. EtherCAT 네트워크의 패킷 속도는 슬레이브 디바이스 노드 개수, 이더넷 케이블 길이, 그리고 가장 중요한 와이어를 통해 푸시되는 I/O 데이터 양 등 여러 요인의 영향을 받습니다. 타이밍 결정성 프로토콜인 EtherCAT 네트워크 타이밍은 정확히 계산되기 때문에 마스터가 슬레이브가 데이터를 업데이트하고 전송하는 시기를 정확히 알 수 있습니다. 당연히 EtherCAT 네트워크 속도는 전체 시스템 루프 속도 중에서 가장 빠릅니다.

NI 9144 EtherCAT RIO 섀시를 NI PAC와 함께 사용하는 경우 이 벤치마크 구성요소는 다음 구성요소에 매핑됩니다.

로직은 사용자가 만든 LabVIEW 코드이며 드라이버는 LabVIEW의 NI 스캔 엔진과 NI-Industrial Communications for EtherCAT 소프트웨어입니다. EtherCAT 네트워크는 물리적 이더넷 케이블을 통한 통신을 뜻하며 I/O는 C 시리즈 I/O 모듈을 나타냅니다. 이 모든 소프트웨어와 하드웨어는 NI 시스템의 시스템 루프 속도 전체를 구성합니다.

단일 스캔 루프 또는 사이클 중에 EtherCAT 패킷 전송 또는 I/O 스캔은 반드시 마스터 컨트롤러와 NI 9144 슬레이브 섀시 간에 동기화되어야 합니다. I/O 스캔 중에 마스터는 슬레이브의 새로운 출력과 지침이 포함된 패킷을 내보내고 슬레이브는 마스터의 새 입력값이 포함된 패킷을 반환합니다. 마스터는 EtherCAT 패킷의 업데이트된 데이터를 사용하여 프로그램 스캔을 시작하고 NI 9144 섀시는 슬레이브 업데이트를 시작합니다. 프로그램 스캔은 마스터가 데이터를 처리하고 LabVIEW 프로그램을 실행하는 데 걸리는 시간입니다. 슬레이브 업데이트는 슬레이브가 DMA 전송, 데이터 처리, I/O 업데이트에 사용하는 시간입니다. 따라서 최소 루프 속도는 프로그램 스캔 또는 슬레이브 업데이트 중 어느 쪽에 더 많은 시간이 걸리는지에 따라 제한됩니다.

그림 4. 스캔 사이클 타이밍 다이어그램

마스터 컨트롤러에 처리할 데이터가 더 많기 때문에 네트워크의 슬레이브와 I/O 개수에 따라 프로그램 스캔 시간이 늘어납니다. 그러나 슬레이브가 I/O를 동시에 병렬로 업데이트하기 때문에 슬레이브 업데이트 시간은 늘어나지 않습니다. 따라서 네트워크에 슬레이브 I/O가 많을수록 마스터의 프로그램 스캔에 장애가 생길 가능성이 커집니다. 어플리케이션에 많은 I/O 채널이 포함된 경우 마스터용으로 PXI와 같은 고성능 컨트롤러를 사용하는 것이 좋습니다.

그림 5. NI 9144 섀시가 있는 CompactRIO와 PXI 시스템

마스터 컨트롤러의 기본 LabVIEW 프로그래밍 모드는 NI 스캔 엔진을 실행합니다. 이 엔진은 단일 포인트 I/O 값을 사용자가 지정한 속도로 스캔하여 메모리로 보내는 LabVIEW Real-Time의 구성요소입니다. 마스터 컨트롤러 벤치마크의 경우 사용자 코드를 실행하는 데 걸리는 시간은 계산되지 않습니다. 따라서 나머지 마스터 벤치마크 구성요소는 드라이버 속도입니다. 여기에는 컨트롤러가 NI 스캔 엔진 메모리 맵 간에 데이터를 I/O 변수로 전송하는 데 걸리는 시간이 포함됩니다. I/O 변수는 NI 스캔 엔진 메모리 맵의 데이터 액세스에 사용되며 LabVIEW VI에 있는 I/O 변수 노드의 각 인스턴스는 실행에 시간이 걸립니다. 각 I/O 변수 노드의 평균 실행 시간은 블록다이어그램의 노드 개수가 늘어나도 일정하게 유지되는 경향이 있으며 그림 6의 차트는 특정 마스터 컨트롤러에 이를 실행했을 때 걸리는 시간을 보여줍니다. 이 데이터를 기반으로 I/O 변수 노드당 평균 실행 시간은 NI cRIO-9074 통합 시스템의 경우 약 8µs, NI cRIO-9022 임베디드 리얼타임 컨트롤러의 경우 3.5µs, NI PXI-8106 듀얼 코어 임베디드 컨트롤러의 경우 0.3µs입니다.

그림 6. I/O 변수 노드당 평균 실행 시간

참고: 이것은 호환되는 모든 NI 컨트롤러의 리스트가 아닙니다. 자세한 내용은 타이밍 결정성 이더넷 제품 선택 가이드를 참조하십시오. 일반적으로 프로세서가 강력할수록 I/O 변수가 더 빨리 실행됩니다.

고객은 종종 마스터 컨트롤러에서 데이지 체인으로 연결할 수 있는 NI 9144 섀시의 최대 개수를 묻습니다. 이론적으로 EtherCAT 프로토콜에 따르면 한 네트워크의 최대 슬레이브 디바이스 개수는 65,535개이지만 이렇게 많은 디바이스를 하나의 마스터 컨트롤러로 제어하면 스캔 속도가 크게 저하됩니다. 따라서 여러 마스터를 사용하는 것이 가장 좋습니다. 실제로는 슬레이브 디바이스의 개수가 아니라 I/O 채널 개수가 마스터의 시스템 스캔 속도에 더 큰 영향을 미칩니다. 그림 4에서 알 수 있듯 EtherCAT 네트워크를 통해 데이터가 많이 푸시될수록 마스터의 프로그램 스캔이 증가하며, 일반적으로 슬레이브 업데이트 시간을 초과하게 됩니다. 따라서 각 슬레이브 디바이스에 추가되는 오버헤드 양에도 불구하고 2개 또는 20개의 NI 9144 섀시로 나누어진 300개의 I/O 채널은 거의 같은 시스템 루프 속도를 보입니다.

테이블 1은 마스터 컨트롤러와 NI 9144의 벤치마크를 결합하여 최소 사이클 시간 또는 시스템 루프 속도를 형성합니다.

최소 사이클 시간 = 드라이버 + EtherCAT 네트워크 + I/O 업데이트

이 벤치마크에는 사용자 코드를 실행하는 데 걸리는 시간이 포함되어 있지 않으므로 코드에 적절한 시간을 추가하십시오. 자세한 정보는 아래 관련 링크를 참조하십시오.

테이블 1. 시스템 루프 속도

이 2개의 컨트롤러와 4개의 각기 다른 I/O 모듈의 테스트를 기반으로 한 system_loop_rate_chart2.xls 벤치마킹 스프레드시트가 이 백서 끝에 첨부되어 있습니다. 이는 설정에 대한 시스템 루프 속도를 대략적으로 파악하는 데 도움이 됩니다. 사용 중인 아날로그 및 디지털 I/O 채널 개수와 LabVIEW 코드를 실행하는 대략적인 시간을 입력하기만 하면 시스템 루프 속도를 계산할 수 있습니다. 이 수식은 특정 하드웨어 설정을 기반으로 하며 다른 I/O 모듈을 사용하면 결과가 달라질 수 있다는 것에 주의하십시오.

NI 9144 확장 섀시를 다른 타사 EtherCAT 마스터와 함께 사용할 수도 있지만 LabVIEW처럼 사용하기 쉬운 프로그래밍 환경은 제공하지 않습니다. 타사 제품을 사용하는 경우 마스터 벤치마크 구성요소 없이 NI 9144와 EtherCAT 네트워크에 대해서만 벤치마크가 제공됩니다. 이는 달성 가능한 최소 사이클 시간이라는 점을 잊지 마십시오. 실제 시스템 루프 속도를 계산하려면 마스터의 프로그램 스캔과 실행 시간을 확인하고 비교해야 합니다. 수식은 다음과 같이 두 부분으로 구성됩니다.

최소 슬레이브 사이클 시간 = 패킷 전송 시간 + 슬레이브 업데이트 시간

EtherCAT 패킷이 마스터를 떠나면 패킷 전송 시간은 프레임 전송, 통신 지연, 도중에 발생하는 모든 지터의 합이 됩니다.

패킷 전송 시간 = 프레임 전송 시간 + 통신 지연 + 지터

프레임 전송으로 EtherCAT 데이터의 모든 바이트에 80ns, 데이터를 전달하는 모든 EtherCAT 프레임에 5µs가 사용됩니다. (이 총 EtherCAT 데이터는 NI 9144 섀시의 I/O 채널 개수와 유형에 직접적으로 대응합니다.) 통신 지연은 모든 NI 9144 섀시에서 600ns, 이더넷 케이블 1 미터당 5ns가 됩니다.

EtherCAT 패킷이 모든 슬레이브를 통과하여 정지하지 않고 마스터로 스트리밍된 후 모든 슬레이브는 병렬로 입력을 읽고 출력을 씁니다. 따라서 슬레이브 업데이트 시간이 가장 나쁜 슬레이브 디바이스로 시스템의 최소 슬레이브 사이클 시간이 결정됩니다.

슬레이브 업데이트 시간 = DMA 전송 시간 + 가장 나쁜 모듈 타이밍

이를 결정하려면 모든 NI 9144 섀시의 고유한 모듈 설정을 고려해야 합니다. 섀시의 모듈을 기반으로 입력과 출력 데이터의 DMA 전송 시간을 계산할 수 있습니다. 또한 가장 나쁜 시작, 변환, 굴절 타이밍을 가진 모듈을 결정할 수 있습니다. 이 값을 더하여 가장 나쁜 슬레이브 업데이트 시간을 찾습니다.

참고: LabVIEW 2009 출시 이후로 LabVIEW FPGA Module을 사용하여 하드웨어 레벨에서 NI 9144의 모듈을 프로그래밍할 수 있습니다. 따라서 업데이트 속도가 시스템 루프 속도보다 빠른 모듈을 활용할 수 있습니다. 모듈의 최대 속도로 I/O를 수집하고 FPGA 코드를 사용하여 사용자 정의 신호를 조작하고 인라인을 처리한 다음 최종 결과를 마스터 컨트롤러에 반환합니다.

NI 9144에서는 다양한 모듈 조합을 사용할 수 있으므로 이 모든 수식을 적용하고 최소 슬레이브 사이클 시간을 정확하게 계산할 수 있도록 ni_9144_only_benchmarks.xls라는 또 다른 벤치마크 스프레드시트가 아래에 제공됩니다. 올바른 값을 입력한 후 타사 마스터의 벤치마크를 계산된 슬레이브 벤치마크에 추가하여 어플리케이션의 전체 시스템 업데이트 속도를 결정합니다. 속도를 더욱 높이려면 LabVIEW FPGA 기능을 사용하여 NI 9144에 사용자 정의 인텔리전스를 다운로드할 수 있습니다.