NI PXIデバイスはどのようにPXIシャーシのバックプレーンへマッピングされていますか?

ハードウェア: PXI/CompactPCI>>Platform Modules>>Timing and Synchronization>>PXI-6651, PXI/CompactPCI>>Platform Modules>>Timing and Synchronization>>PXI-6652, PXI/CompactPCI>>Platform Modules>>Timing and Synchronization>>PXI-6653

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||

問題:

ナショナルインスツルメンツ(NI)のPXIデバイスを所有しています。このデバイスがスタートリガ、PXIトリガライン、10 MHzバックプレーンクロックもしくはローカルバスを利用可能かどうかを確認するにはどうすれば良いですか?

解決策:

NI PXIデバイスの各製品群によって異なる機能を搭載しているため、PXIバックプレーンの機能も異なります。それぞれのデバイスがどのように接続するかを理解するには、まずいくつかの理論を理解することが重要です。以下の順で理論とその実例を説明します。

1. どのPXIスロットがPXIタイミング/同期機能にアクセスできますか?

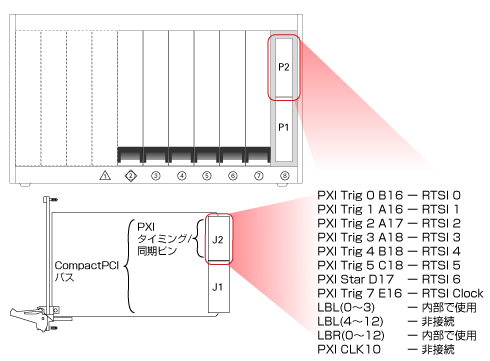

PXIはCompactPCIにタイミングおよび同期機能を追加したものです。これらの追加機能は、デバイスのJ2コネクタに実装されています(シャーシではP2コネクタになります)。

上記で説明した機能は、すべてのPXIシャーシの適切なスロットで利用することができます。これらの機能の利点を活用するには、PXIバックプレーンで信号をピンにルーティングする必要があるため、PXIデバイスの設計者次第となります。そのため、すべてのPXIデバイスがPXIバックプレーンで利用できるタイミング/同期機能を使用することができるわけではありません。

PXIデバイスおよびドライバのドキュメントに、利用可能なPXIバックプレーンの機能が記載されています。

2. PXIタイミング/同期機能を使用するためのPXIデバイス要件は何ですか?

3. NI PXIデバイスはどのようにPXIバックプレーンを使用しますか?

- どのPXIスロットがPXIタイミング/同期機能にアクセスできますか?

- PXIタイミング/同期機能を使用するためのPXIデバイス要件は何ですか?

- NI PXIデバイスはどのようにPXIバックプレーンを使用しますか?

1. どのPXIスロットがPXIタイミング/同期機能にアクセスできますか?

PXIはCompactPCIにタイミングおよび同期機能を追加したものです。これらの追加機能は、デバイスのJ2コネクタに実装されています(シャーシではP2コネクタになります)。

- 10 MHzバックプレーンクロック

10 MHzバックプレーンクロック(CLK10)は、スロット1(コントローラスロット)を除くすべてのPXIスロットに対して物理的に等しい長さの回路でルーティングされた10 MHzクロック信号です。PXI仕様(下記のリンクを参照)では、この信号が少なくとも±100 ppmの確度でなければならないと定めていますが、NIシャーシは±25 ppmの確度で提供しています。その信号は、スロット2に取り付けたPXIモジュールが搭載する10 MHzクロックソース、もしくは他のシャーシ(例: PXI-1042)からのCLK10信号を優先させることができます。いくつかのPXIデバイスは、通常、位相ロックループ(PLL)技術を使用して内部クロックを同期するために、基準信号としてCLK10信号を使用します。

- PXIスタートリガ

PXIスタートリガは、スロット2に取り付けたモジュールによって駆動させることができるトリガです。スロット2から13スロットまで物理的に等しい長さの回路でデジタルTTL信号を送ることが可能です。その結果、5ナノ秒以下の伝搬遅延でトリガを送ることができ、実質的にすべてのスロットで同時に受け取れます。さまざまなPXIデバイスが同時に処理を開始する必要があるアプリケーションにおいて非常に有効です。PXIスタートリガは、105 MHzのTTL信号まで動作検証されています。

- PXIトリガバス

コントローラスロットを含むすべてのPXIスロットでタイミングおよびトリガ信号(デジタルTTL信号)を送受信できる8ラインのバスです。この信号の品質を維持するには、20 MHz以下のデジタルTTL信号を送ることをお勧めします。

- ローカルバス

各周辺機器スロットにあるローカルバスは、左右の隣接したモジュールに接続する13ラインからなる2つのバスです。これらのローカルバスラインは、高速デジタルおよびアナログ信号(最大42 Vまで)転送することが可能です。

メモ: スロット2は、左側のローカルがスタートリガに置き換わっているため、右側のローカルバスしかありません。

上記で説明した機能は、すべてのPXIシャーシの適切なスロットで利用することができます。これらの機能の利点を活用するには、PXIバックプレーンで信号をピンにルーティングする必要があるため、PXIデバイスの設計者次第となります。そのため、すべてのPXIデバイスがPXIバックプレーンで利用できるタイミング/同期機能を使用することができるわけではありません。

PXIデバイスおよびドライバのドキュメントに、利用可能なPXIバックプレーンの機能が記載されています。

2. PXIタイミング/同期機能を使用するためのPXIデバイス要件は何ですか?

- PXデバイスは、物理的にPXIバックプレーン対してそれぞれのタイミング/同期機能に対応するピンを接続する必要があります。NI PXIデバイスのマニュアルには、バックプレーンに対する信号マッピングが記載されています。

下記の表は、PXI Eシリーズユーザマニュアルに記載されている図1-1です。ここでは、PXIバックプレーンに対して信号をデバイスのどのピンにマッピングするかを示しています。

PXI EシリーズDAQの信号 PXIピン名 PXI J2ピン名 RTSIトリガ (0...5) PXI Trigger (0..5) B16、A16、A17、A18、B18、C18 RTSIトリガ (6) PXI Star D17 RTSIクロック PXI Trigger (7) E16 予約済み LBL(0..3) C20、E20、A19、C19 予約済み LBR(0..12) A21、C21、D21、E21、A20、B20、E15、A3、C3、D3、E3、A2、B2

この表は、PXI EシリーズDAQデバイスがPXIトリガライン0、1、2、3、4、5、7を使用していますが、PXIトリガライン6がないことを示しています。これらは、PXIスタートリガラインの信号を読み取ることはできますが、PXIバックプレーンクロックを読み取ることはできません。

このデバイスは、いくつかのローカルバスの左側ライン(0~3)とすべてのローカルバスの右側ラインへ物理的な接続があります。しかし、これらのラインは従来型NI-DAQドライバで予約されており何も機能を提供していないため、ユーザがこれらのラインにアクセスすることができません。

NI-DAQmxドライバでは、NI MAXのシャーシ構成でこれらのラインの予約解除がおこなえます。下図は、表を図式化にしたものです。

お使いのデバイスのユーザマニュアルは、下記の関連リンクから検索することができます。

- 取り付けられたスロットによりPXIデバイスは異なる機能を実行することができますが、その場合はそれに応じてドライバから適切な設定をおこなう必要があります。すなわち、PXIデバイスがPXIシャーシバックプレーンのタイミング/同期ピンに接続されていても、ドライバでユーザがその機能を使えるように設定しないとそういった機能は使えません。

NIのドライバでは、NI PXIデバイスの機能を活用できるようになっています。デバイスに対応する適切なドライバをダウンロードするには、下記よりドライバと更新ページを参照して検索してください。

- 最後の要件は、コンピュータのシステムディレクトリに適切なPXIシステム初期化ファイル(pxisys.ini)を保存することです。pxisys.iniファイルにはシステムの構成が記述されていて、PXIシャーシのPCIバスをPXIシャーシの前面に記載されているスロット番号に割り当てます。

メモ: Measurement and Automation Explorer(MAX) 3.x以降では、自動的にpxisys.iniファイルを生成して適切な場所に保存します。レガシーのNI MAXでPXIシステムを構成する方法については、『ホワイトペーパー: Configuring Your PXI System in Legacy Versions of MAX』を参照してください。

pxisys.iniファイルの詳細については、技術サポートデータベース 1EGB71UI、技術サポートデータベース 2MDFG2WD、およびPXI Specificationを参照してください。

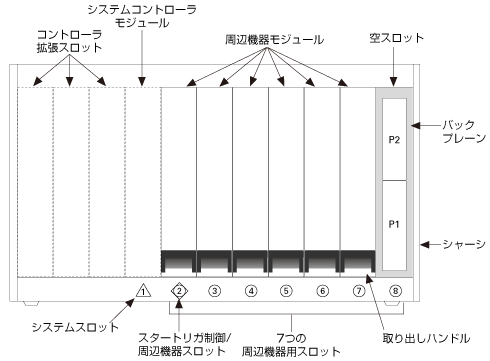

PXI仕様では、PXIシャーシで3種類のスロットが定義されています。

- システムスロット

NI PXIシャーシでは、一番左側にあるスロットです。シャーシの前面には、スロット番号「1」と三角形のグリフが記載されています。このスロットにシステムのPXIコントローラを取り付けます。

- スタートリガコントローラ

PXIシャーシの2番目のスロットです。PXIスタートリガラインを駆動するには、スロット2にこのラインを駆動できる機能を搭載したPXIデバイスを取り付ける必要があります。

たとえば、CLK10をオーバーライドするには、スロット2にCLK10信号をオーバーライドする機能があるPXIデバイスを取り付ける必要があります。シャーシの前面には、45度傾いた四角形のグリフが記載されています。

なお、このスロットは特別な機能を搭載しない通常のPXIデバイスを取り付けることもでき、周辺機器スロットとして使用することもできます。そのため、周辺機器モジュールと同じグリフも記載されています(下図を参照)。

- 周辺機器スロット

周辺機器スロットは、シャーシでスロット1および2以外のすべてのスロットで、PXI/CompactPCI規格に準拠したデバイスを取り付けることができます。いくつかのPXIデバイスには、PXIスタートリガ、CLK10信号もしくはPXIトリガラインを読み取る機能があります。

ほかには、隣接したモジュールとデータを共有するためにローカルバスを使用できる機能があります。また上記で説明したもの以外にも、異なるタイミング/同期機能にアクセスできるように設計されたPXIデバイスもあります。

下図は、NI PXI-1042シャーシのスロットタイプおよび前面に記載された番号付けとグリフを示しています。

コンピュータのシステムディレクトリにpxisys.iniファイルを保存する必要があるのは、ドライバが検索して読み取るためです。それにより、ドライバは取り付けたデバイスがPXIシャーシのどのスロットにあるかを判断します。ドライバは取り付けたデバイスのスロットによって、デバイスの異なる回路を有効にします。

たとえば、PXI-6608カウンタ/タイマデバイスには、PXIバックプレーンでCLK10信号をオーバーライドする機能がありますが、自動的にCLK10信号をオーバーライドする機能するわけではありません。

デバイスドライバであるNI-DAQもしくはNI-DAQmxは、まずPXIシャーシのスロット2にデバイスが取り付けられているかどうかを確認するため、pxisys.iniファイルを読み取る必要があります。正しく取り付けられている場合、ドライバは適切なコマンドをPXI-6608に送信し、内部CLK10信号をPXI CLK10信号にルーティングします。

- システムスロット

3. NI PXIデバイスはどのようにPXIバックプレーンを使用しますか?

| 利用可能な PXIデバイス機能 |

機能に対応する NI PXIデバイス |

補足情報 |

| CLK10信号のオーバーライド | PXI-6608 (カウンタ) PXI-6653、PXI-6652、PXI-6682 (タイミング/同期モジュール) PXI-5660 (RFアナライザ) |

|

| CLK10信号に位相ロックループ(PLL) | PXI-6653、PXI-6652 (タイミング/同期モジュール) PXI-6115、PXI-6120 (同時サンプリングDAQ) PXI-6534 (高速デジタル) PXI-5401、PXI-5404、PXI-5411、PXI-5421、PXI-5431 (波形発生器) PXI-5102、PXI-5112、PXI-5122、PXI-5620、PXI-5621 (高速デジタイザ) |

|

| PXIスタートリガを駆動 | PXI-665x, PXI-6682 (タイミング/同期モジュール) PXI-5112(高速デジタル) PXI-7344(モーション) PXI-4461、PXI-4472、PXI-4474 (DSA) |

|

| PXIスタートリガを受信 | ほとんどのNI PXIデバイスでPXIスタートリガを受信可能 例外: バスインタフェースモジュール、PXI-660xおよびPXI-653xは除く |

|

| PXIトリガラインの読み書き | ほとんどのNI PXI デバイスでPXIトリガラインの読み取り/書き込みが可能 |

これらのPXIデバイスには、PXIバックプレーンにルーティングされる7つのRTSIラインあります。

|

| ローカルバスの使用 | すべてのマルチファンクションDAQ PXI-4060、PXI-4070 (DMM) PXI-653x (高速デジタル) PXI-650x (デジタル) PXI-4021 (スイッチ制御) PXI-781xR、PXI-783xR |

PXIコンボシャーシ(PXI‐101xシャーシ)のSCXI部分を制御するには、右端のスロットにPXIデバイスを取り付ける必要があります。各デバイスタイプの機能は、以下のとおりです。

|

関連リンク:

PXI Alliance Memberホームページ: PXI Specification

ホワイトペーパー: Configuring Your PXI System in Legacy Versions of MAX

技術サポートデータベース 1EGB71UI: PXISYS.INI及び、CHASSIS.INIとは何ですか?

技術サポートデータベース 2MDFG2WD: Programmatic PXI Slot Detection

技術サポートデータベース 2NFGGQAL: OCXO Stability On The PXI-6608 Counter/Timer

技術サポートデータベース 2CCF38PQ: Accuracy Problems when I Drive the PXI Backplane Clock with a PXI-6608

技術サポートデータベース 3QQFJVZA: PXI/SCXI Combination Chassis SCXI Configurations

技術サポートデータベース 4XSC340S: What Signal Speeds Do My PXI Chassis Trigger Lines Support?

技術サポートデータベース 2WF8F22L: 複数のPXIシャーシにあるNI PXI-4472 DSAデバイスを同期するには?

技術サポートデータベース 2WF8F22L: スタートリガ信号の送受信が可能なPXIボード

製品マニュアル: Note to Users: About Your 6608 Device(PDF)

添付:

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||

報告日時: 09/08/2006

最終更新日: 03/02/2017

ドキュメントID: 417ED39E