¿Cómo Puedo Sincronizar Múltiples Dispositivos de la Serie R?

Software Primario:

Versión de Software Primario: 1.0

Versión de Software Primario Corregido: N/A

Software Secundario: LabVIEW Modules>>LabVIEW Real-Time Module

Hardware: Reconfigurable I/O (RIO)>>R Series

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||

Problema:

Quiero sincronizar mi dispositivo de la serie R con otros dispositivos PXI u otros dispositivos PCI ¿Cómo lo puedo lograr?

Solución:

Para lograr la sincronización de dispositivos múltiples, las tarjetas de la serie R son capaces de utilizar temporizaciones externas y líneas de sincronización. Para tarjetas PCI, se puede usar un bus RTSI externo para conectar varias tarjetas. Para los módulos PXI, el bus de sincronización está integrado en el plano trasero del chasis PXI y se denomina bus de disparo PXI (“PXI Trigger bus” en inglés). Puede utilizar las líneas de bus de disparo RTSI / PXI para sincronizar un dispositivo de la Serie R con cualquier otro dispositivo que admita los disparadores del bus RTSI / PXI. Para ambos factores de forma, se puede acceder al bus de sincronización a través de los nodos de E/S de FPGA. El proyecto utilizado se ha añadido como

RSeriesSync.zip al final de este documento. Para agregar una E/S RTSI o PXI para la FPGA en el proyecto:

- Haga clic con el botón derecho en la FPGA en la ventana del Explorador de proyectos y seleccione New»FPGA I/O.

- Debajo de Available Resources en la ventana New FPGA I/O, expanda el recurso RTSI o PXI (la selección variará según el dispositivo de la serie R y el factor de forma).

- Seleccione las líneas RTSI o PXI_TRIG que desea agregar y haga clic en la flecha azul que apunta a la derecha.

- Haga clic en el botón OK.

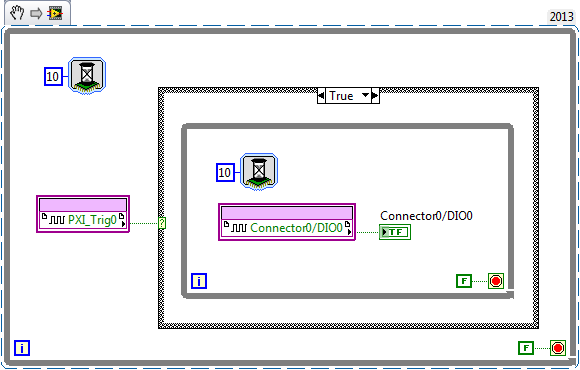

Una vez agregada al proyecto, se puede agregar un nodo FPGA I/O para dicha línea del bus de disparo RTSI/PXI. Este puede ser configurado como una señal de entrada o salida, similar a líneas digitales E/S. A continuación, se muestra un ejemplo en el cual una línea de disparo PXI es activada en un dispositivo PXI- 7811R previo a la escritura digital.

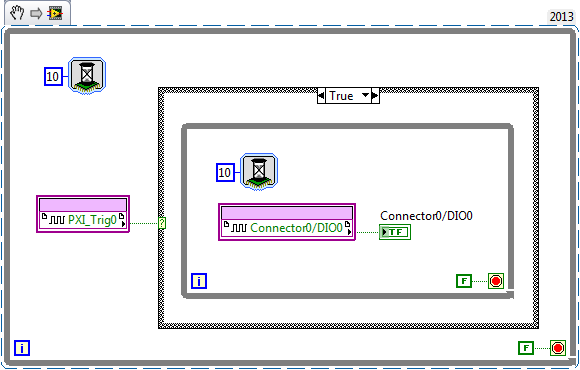

Otra tarjeta de la serie R ubicada en el mismo chasis PXI puede leer el valor del bus de sincronización. En el siguiente ejemplo, la tarjeta de la serie R espera el disparo en el bus de disparo PXI. Cuando recibe el disparo, comienza la lectura de la entrada digital.

Nota Importante:

Las líneas de bus de disparo RTSI / PXI están conectadas en paralelo a todos los demás dispositivos en el bus y, por lo tanto, cada línea de bus de sincronización RTSI / PXI debe ser manejada por un dispositivo a la vez. Se puede dañar dispositivos al manejar la misma línea de sincronización desde dos dispositivos diferentes a la vez.

Las líneas de bus de disparo RTSI / PXI están conectadas en paralelo a todos los demás dispositivos en el bus y, por lo tanto, cada línea de bus de sincronización RTSI / PXI debe ser manejada por un dispositivo a la vez. Se puede dañar dispositivos al manejar la misma línea de sincronización desde dos dispositivos diferentes a la vez.

Ligas Relacionadas:

Manual del Producto: NI R Series Multifunction RIO User Manual (June 2009)

Documento de Soporte 5M8B8100: Why are the PXI_Trig Lines Continuously Triggering with a R Series or FlexRIO Device? (en inglés)

Nota Técnica: Advanced Data Acquisition Techniques with R Series

Documento de Soporte 3TM6QU8T: Synchronizing the FPGA Clock on R Series and FlexRIO Boards to the PXI 10MHZ Clock (en inglés)

Documento de Soporte 2R5FK53J: ¿Qué es RTSI y cómo se configura?

Archivos Adjuntos:

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||

Día del Reporte: 12/29/2016

Última Actualización: 05/18/2017

Identificación del Documento: 5SRJK2VO