エンジニアからNI PXIが選ばれているのは、その計測性能の高さ、テスト時間の短縮、テスト全体のコスト削減に実績があるためです。PXIの優れた性能、モジュール性、ソフトウェア接続性を兼ね備えており、高確度、多チャンネル数、混合測定を必要とするテストアプリケーションに最適です。

以下の用途に最適:

- 電子デバイスの製造テストシステム

- 検証テストの自動化

- 多チャンネルで高速のテストアプリケーション

- 計測器、センサ、電気測定の組み合わせ

PXIはテストエンジニア用コンピュータです。これは、マルチスロットシャーシにコントローラと計測器を組み合わせたテストおよび計測用プラットフォームです。エンジニアはNI PXIを使用して、検証と製造テストのための高性能な複合測定システムを構築します。

エンジニアからNI PXIが選ばれているのは、その計測性能の高さ、テスト時間の短縮、テスト全体のコスト削減に実績があるためです。PXIの優れた性能、モジュール性、ソフトウェア接続性を兼ね備えており、高確度、多チャンネル数、混合測定を必要とするテストアプリケーションに最適です。

以下の用途に最適:

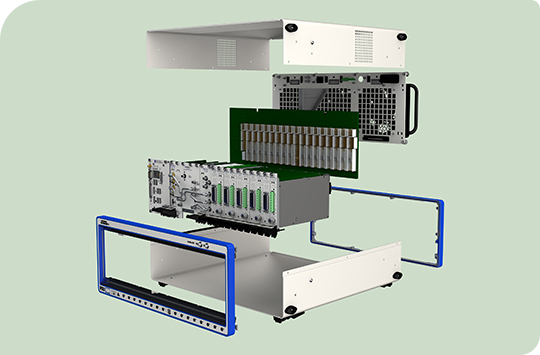

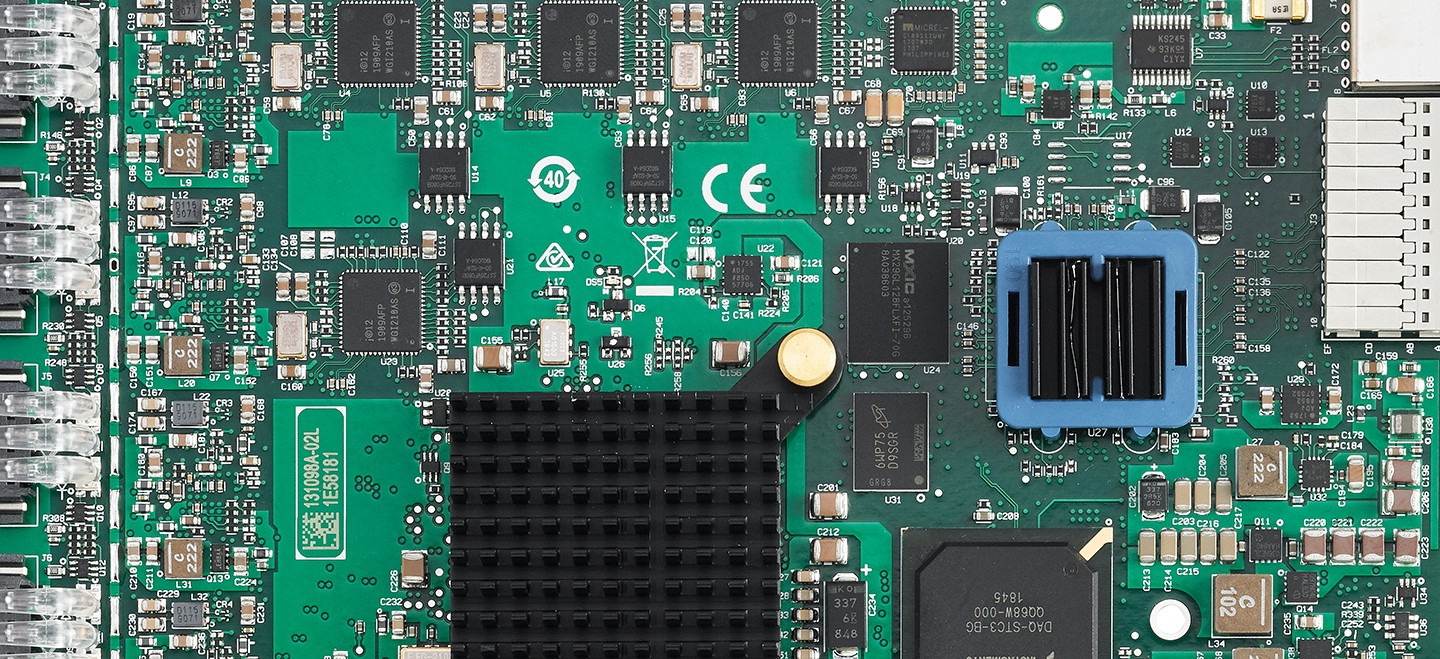

PXIシステムの主要な3つのハードウェアコンポーネント:シャーシ、コントローラ、モジュールシステムソフトウェアは、再構成とカスタマイズのいずれも可能です。

LabVIEW+ Suiteは、LabVIEW、TestStand、DIAdemなどをまとめた製品です。PXI計測器の自動化から、製造現場でのテストシーケンスのデプロイまで、LabVIEW+は必要なソフトウェアを提供します。

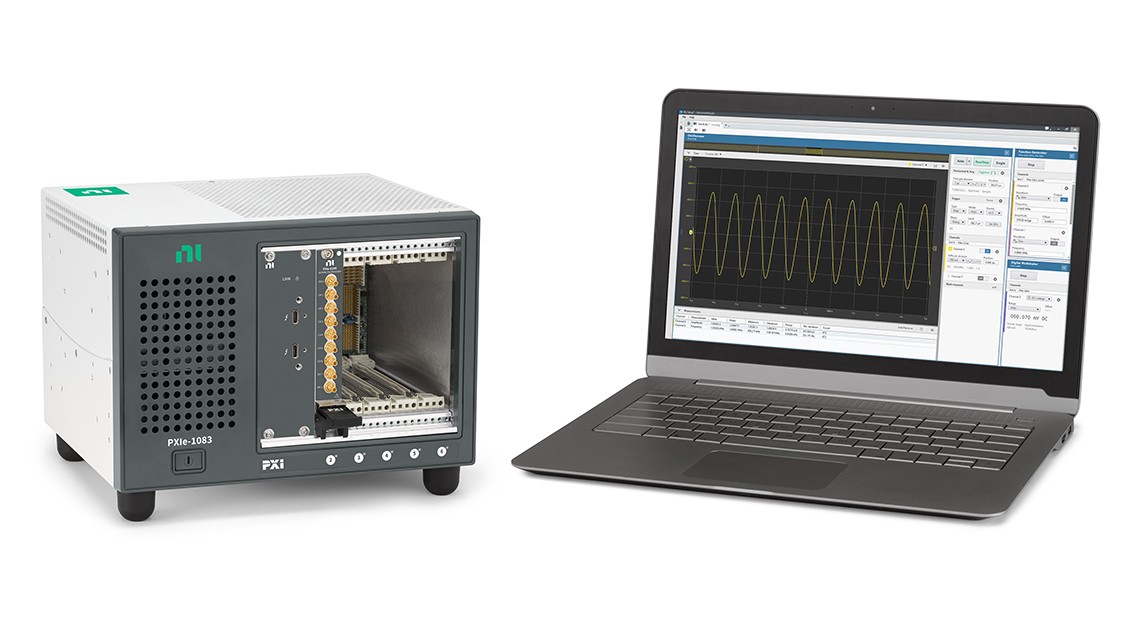

InstrumentStudioソフトウェアは、PXIシステム用の無料アプリケーションソフトウェアです。このソフトウェアは、迅速に測定を行い、テストシステムを効率的に監視およびデバッグするのに役立ちます。

シャーシはPXIシステムの基幹部分であり、PCの機械的な筐体およびマザーボードに相当します。これが電源、冷却、通信バスを提供し、計測器モジュールを同期します。シャーシのスロット数は4~18と種々のサイズがあり、ポータブル、ベンチトップ、ラックマウント、組み込みシステムなど、さまざまな用途とニーズに対応しています。

PXIコントローラには、組込コントローラとリモートコントローラがあります。組込コントローラは、リモートコントローラでPXIシステムをデスクトップ、ノートブック、サーバコンピュータから制御できる一方、外部PCなしでPXIシステムを実行するのに必要なすべてが含まれています。ニーズに合ったコントローラを選択してください。組み込みコントローラは性能が高く、リモートコントローラはコストパフォーマンスが高くなります。

PXI計測器バンドルは、NIで最も人気のある高品質な計測器の構成済みセットです。各バンドルには、5スロットあるThunderbolt™制御のPXIシャーシにPXIモジュールが含まれているため、簡単に開始できます。

ハードウェアを梱包から取り出した瞬間から、デプロイメントやライフサイクルメンテナンスに至るまで、NIは迅速な利用開始と効率的な運用ができるようにお客様を支援します。

課題を克服:

修理サービス

ライフサイクルサービス

構成

キャリブレーション

「COTSアプローチへと移行してPXIとLabVIEWを採用したことは、Philips社の製造テストの成功にとって極めて重要でした。クラス最高のモジュール式ハードウェアと業界標準のソフトウェアの組み合わせは、製造テストのエンジニアリングで数百万ドルの節約と数百時間の短縮を達成するために極めて重要でした。」

シニアマネージャー

Philips社

このオンデマンド入門向けウェビナーでは、ソフトウェアを含むNI PXIテストおよび計測システムの構成を説明します。

多くの場合、PXIシステムという1つのコンポーネントで完全に自動化されたテストセットアップが完成します。完全なテストシステム構築の最初から最後までのベストプラクティスを学びます。